Novel 12-tube SRAM (Static Random Access memory) unit circuit capable of simultaneously increasing read noise tolerance and writing margin

A noise tolerance, unit circuit technology, applied in the field of circuits, can solve problems such as extra power consumption, stability damage, etc., to achieve the effect of improving write margin, eliminating half-select problems, and solving write-half-select problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

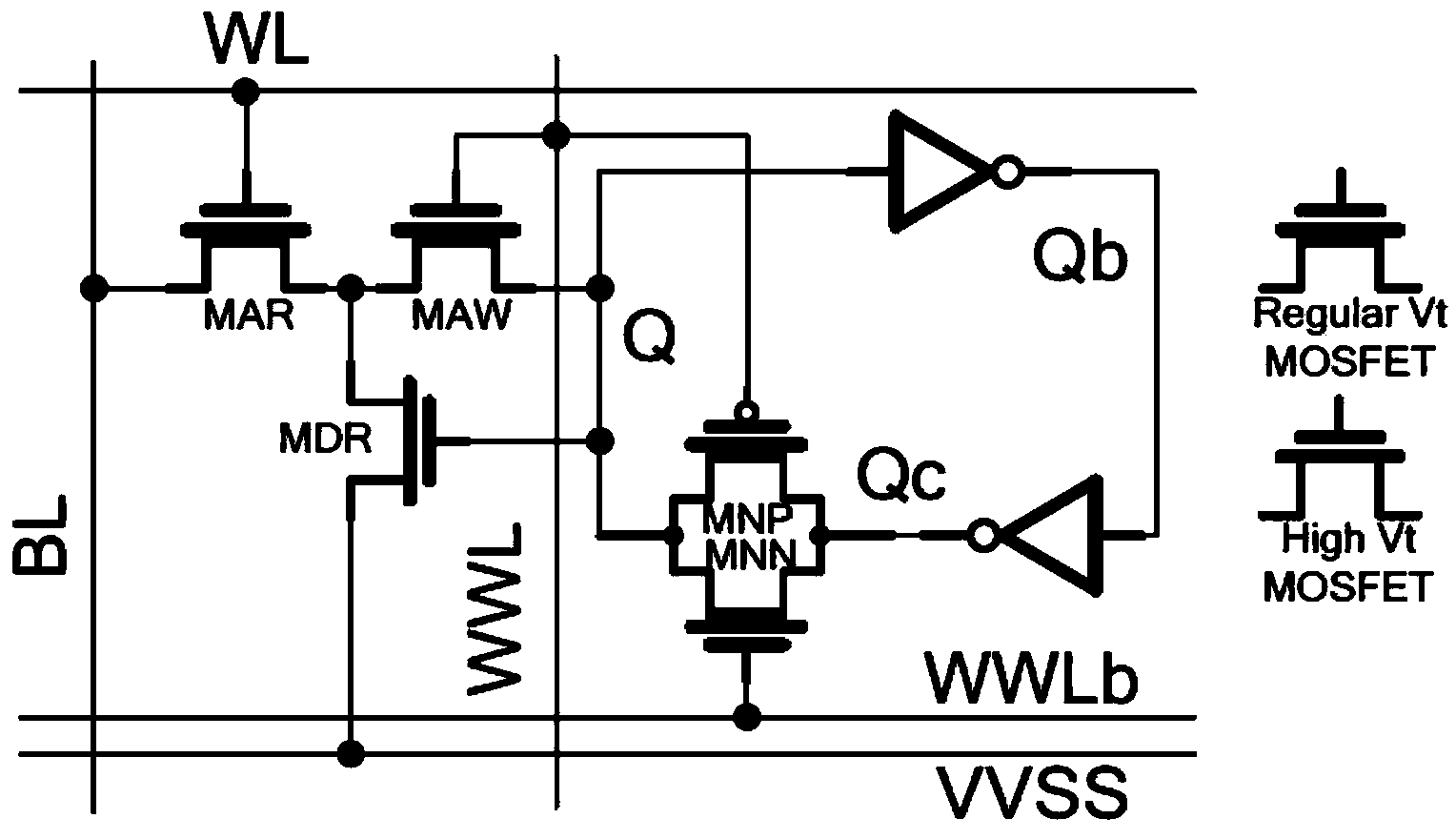

[0032] Figure 4 It is a schematic structural diagram of a novel 12-tube SRAM unit circuit that improves read noise tolerance and write margin at the same time provided by an embodiment of the present invention. like Figure 4 As shown, the circuit mainly includes:

[0033] Four PMOS transistors P1~P4 and eight NMOS transistors N1~N8;

[0034] Wherein, the NMOS transistor N1 and the PMOS transistor P1 form an inverter A1, the input terminal of the inverter A1 is connected to the word line WL, the output terminal is connected to the gate of the NMOS transistor N4, and the source of the PMOS transistor P1 is connected to the chip selection CS , the source of the NMOS transistor N1 is grounded;

[0035] The PMOS transistor P4 and the NMOS transistor N7 form a parallel structure, and the gate of the NMOS transistor N7 is connected to the word line WL;

[0036] NMOS transistor N2 and PMOS transistor P2 form an inverter A2, and NMOS transistor N3 and PMOS transistor P3 form an i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More