Fin type field effect transistor and formation method thereof

A fin field effect and transistor technology, which is applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as difficulty in adjusting the threshold voltage of fin field effect transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background art, it is difficult to adjust the threshold value of the fin field effect transistor by using the substrate bias voltage in the prior art.

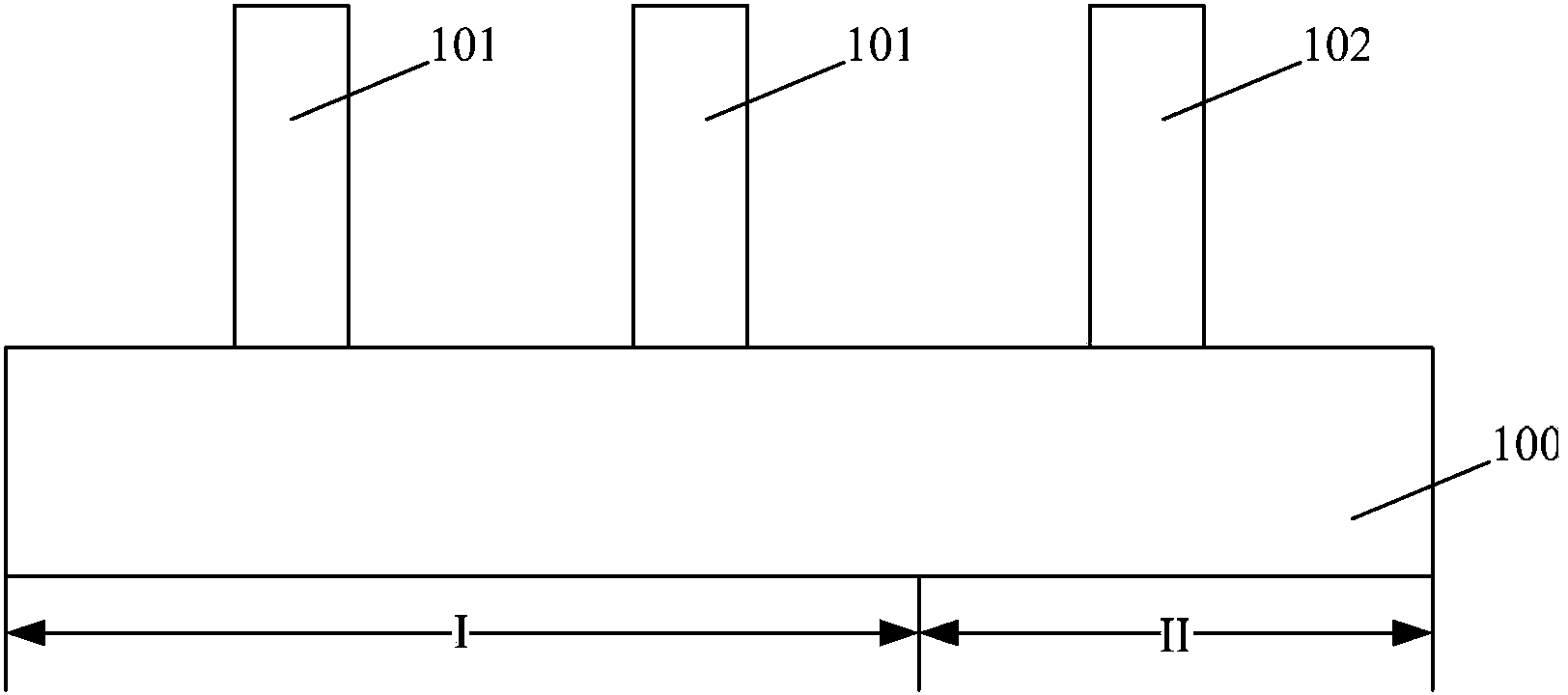

[0034] refer to figure 1 In the prior art, when adjusting the threshold voltage of the fin field effect transistor, the bias control voltage Vb is usually connected to the semiconductor substrate 10. Research has found that the bias control voltage Vb needs to pass through the semiconductor substrate 10 and the fin portion 14 Only then can it be conducted to the vicinity of the surface of the fin 14 at the bottom of the gate structure 12. Due to the high height of the fin 14, the conduction path of the bias control voltage Vb is very long, and the resistance on the conduction path is relatively large. Therefore, through the bias control The potential of the voltage Vb applied to the surface of the fin 14 at the bottom of the gate structure 12 is very small, which is not conducive to the adjustment of...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com