Through-silicon via and forming method thereof

A technology of through-silicon via and silicon germanium, which is applied in electrical components, electrical solid-state devices, circuits, etc., can solve the problems of holes in conductive pillars, unsatisfactory effects, and decreased electrical conductivity, so as to save costs, save process costs, and reduce The effect of energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

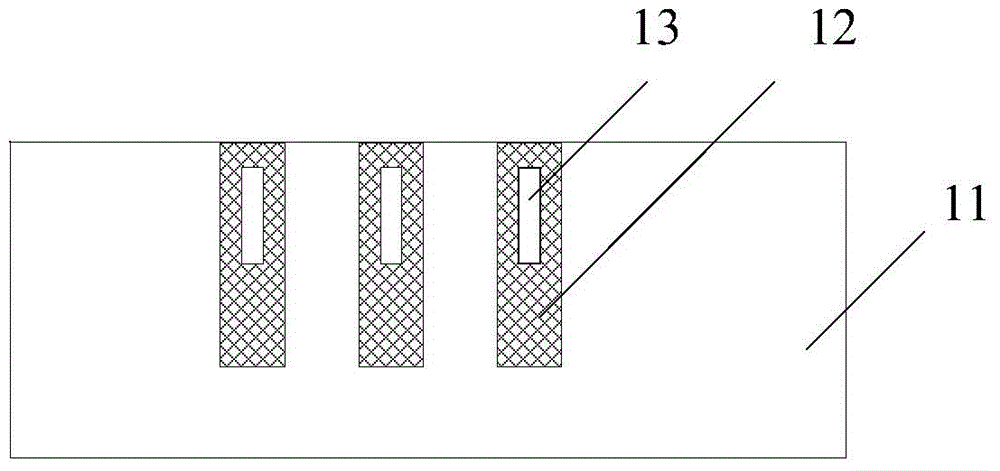

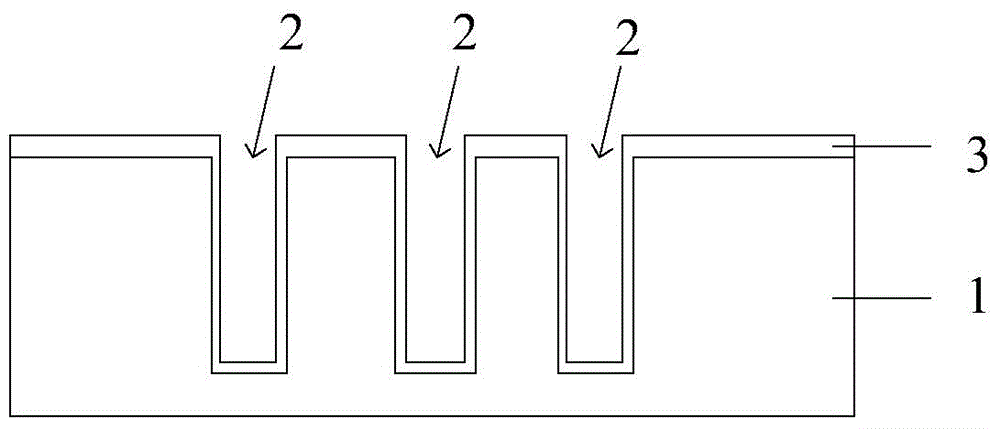

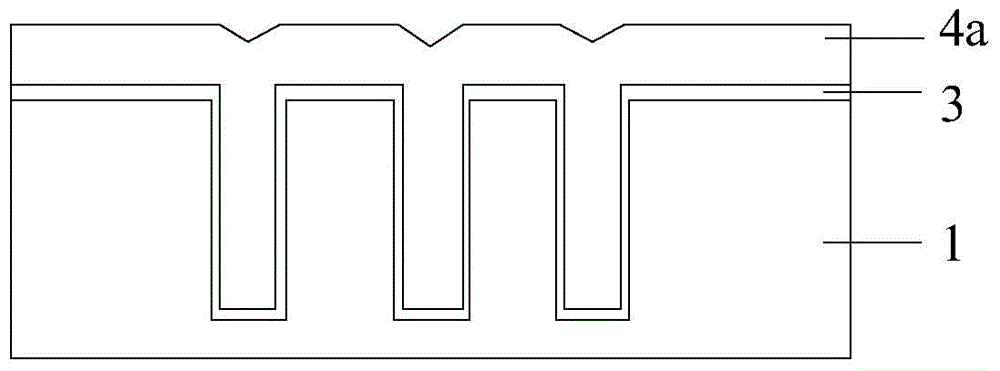

[0027] In the existing method, copper or tungsten is usually used for filling in the process of forming the through-silicon vias.

[0028] When copper filling is used, electroplating copper is usually used. With the decrease of the width of the through-hole and the increase of the depth of the through-hole in the through-silicon via, the bottom area of the through-hole decreases, and the bottom of the through-hole is concave, which leads to the increase of the resistance at the bottom of the through-hole, and even the appearance of a through-hole The bottom resistance is greater than the side resistance of the through hole. Therefore, during the copper electroplating process, the copper deposition rate on the side of the through hole is greater than the copper deposition rate at the bottom of the through hole, resulting in holes in the formed copper pillars.

[0029] When tungsten is used for filling, chemical vapor deposition of metal organic compounds is usually adopted, a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com