Integrated Circuit Reliability Analysis Test Structure and Test Method

A technology for analysis and testing of integrated circuits, applied in the field of reliability analysis and testing structures of integrated circuits, can solve problems such as structures that do not deliberately and accurately evaluate the reliability of side trench isolation, and affect the electrical characteristics of devices, so as to achieve accurate evaluation of reliability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

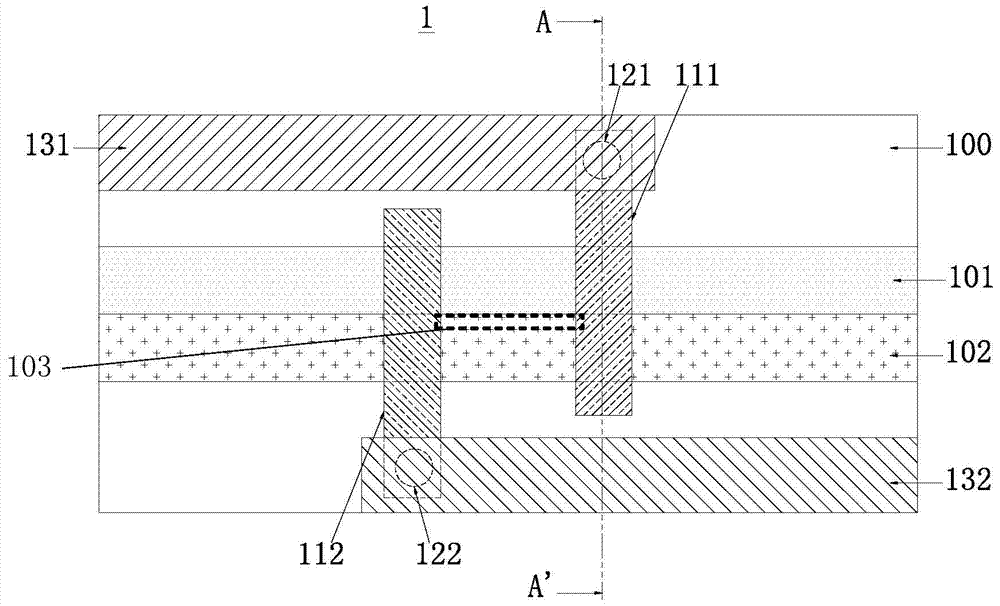

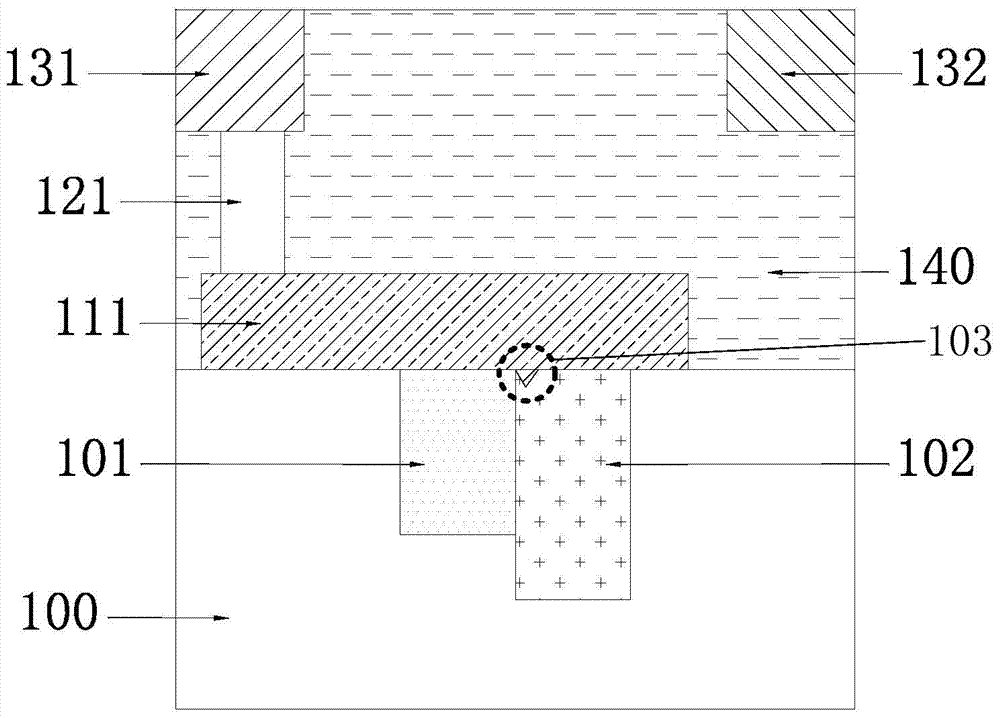

[0054] In the first embodiment, the test structure 1 includes a first gate structure and a second gate structure. Please refer to Figure 2-Figure 3 The reliability analysis and test structure of the integrated circuit is specifically described, where: figure 2 Is a top view of an integrated circuit reliability analysis test structure in an embodiment of the present invention, image 3 for figure 2 In the cross-sectional view along the cut line A-A', the dielectric 140 is common technical knowledge known in the art, so in order to clearly illustrate the structure of this embodiment, figure 2 The dielectric 140 is omitted in the image 3 Clearly shown in.

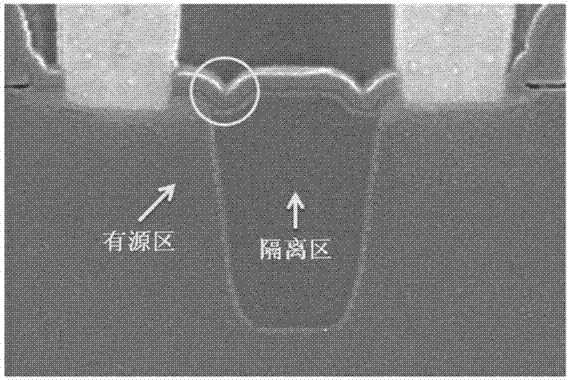

[0055] Such as figure 2 As shown, the substrate 100 includes an active region 101 and an isolation region 102, wherein the shape, size, number, and arrangement of the active region 101 and the isolation region 102 are not specifically limited, depending on the circuit design (Design) For example, in this embodiment, the acti...

no. 2 example

[0064] Please refer to Image 6 , Image 6 Is a top view of an integrated circuit reliability analysis test structure in another embodiment of the present invention, Figure 7 for Image 6 A cross-sectional view along the section line B-B'. In the figure, the same reference numerals indicate equivalent Figure 1-Figure 5 The label in. The second embodiment is based on the first embodiment. The difference is that the reliability analysis test structure 2 of the integrated circuit includes two first gate structures 111 and two second gate structures 112, The first gate structure 111 and the second gate structure 112 are arranged alternately.

[0065] Preferably, the first metal line structure 131 and the second metal line structure 132 are both a metal connection line, the first metal line structure 131 is perpendicular to the first gate structure 111, and the second metal line The structure 132 is perpendicular to the second gate structure 112, and the first metal line structure ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More