Multi-grid transistor and preparation method thereof

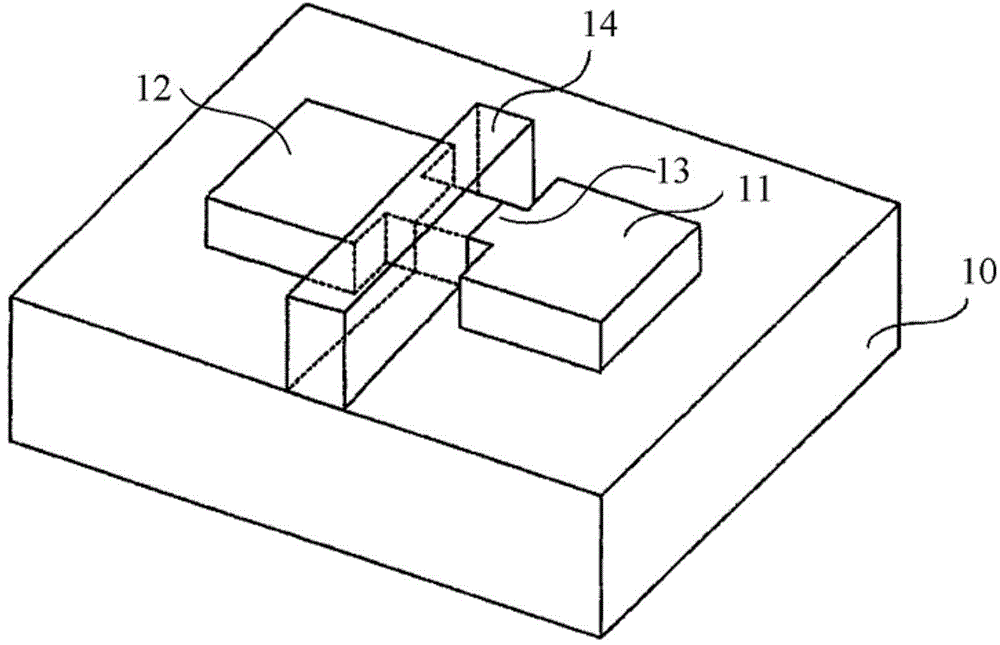

A transistor and multi-gate technology, applied in the field of multi-gate transistors and their preparation, can solve the problems of easy occurrence of abnormality, poor stability, damage of fins 13, etc., and achieve the effect of improving the reaction speed and avoiding easy damage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

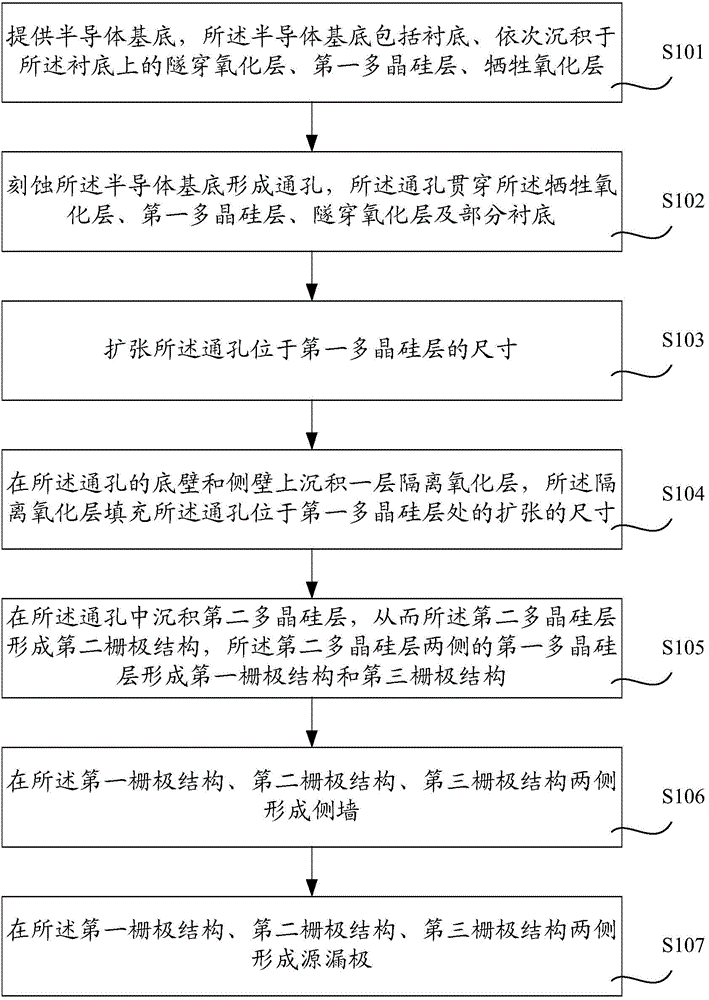

[0048] In combination with the above core ideas, the method for preparing a multi-gate transistor provided by the present invention includes:

[0049] Step S101, providing a semiconductor substrate, the semiconductor substrate comprising a substrate, a gate oxide layer deposited on the substrate in sequence, a first polysilicon layer, and a sacrificial oxide layer;

[0050] Step S102, etching the semiconductor substrate to form a through hole, the through hole passing through the sacrificial oxide layer, the first polysilicon layer, the gate oxide layer and part of the substrate;

[0051] Step S103, expanding the size of the through hole located in the first polysilicon layer;

[0052] Step S104, depositing an isolation oxide layer on the bottom wall and the side wall of the through hole, the isolation oxide layer filling the expanded size of the through hole at the first polysilicon layer;

[0053] Step S105, depositing a second polysilicon layer in the through hole, so that...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More