A three-dimensional stacked packaging structure and packaging method thereof

A technology of stacked packaging and packaging methods, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of packaging trends that do not conform to miniaturization, shrink packaging volume, and difficult processes, etc., to achieve control of warping problems, The effect of simplifying the process and reducing the production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

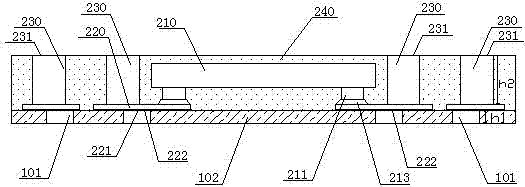

[0067] Example 1, see image 3

[0068] See image 3 , image 3 It is a schematic cross-sectional view of a package structure using micro bumps to form an electrical interconnection between a chip and a package body of the present invention.

[0069] by image 3 It can be seen that the structure of the package monomer of the present invention includes a chip package body and a lower package body. The lower package body is located below the chip package body and is closely connected with the chip package body through a packaging process.

[0070] The chip 210 of the chip package is located in the center of the entire chip package, and the wiring metal layer 220 is selectively distributed around the chip 210. There may be more than one chip 210, and their models may be the same or different, and they may be arranged as required. Using the chip flip-chip process, the chip 210 and the near-chip end of the rewiring metal layer 220 are flip-chip connected to the rewiring metal layer 220 t...

Embodiment 2

[0085] Example two, see Image 6

[0086] See Image 6 , Image 6 It is a schematic cross-sectional view of a package structure using wire bonding to form electrical interconnections between the chip and the package body of the present invention.

[0087] by Image 6 It can be seen that the structure of the package monomer of the present invention includes a chip package body and a lower package body, and the lower package body and the chip package body are tightly connected through a packaging process.

[0088] The chip 210 of the chip package is located in the center of the entire chip package, and the wiring metal layer 220 is selectively distributed around the chip 210. There may be more than one chip 210, and their models may be the same or different, and they may be arranged as required. Using a wire bonding process, the electrode of the chip 210 and the near-chip end of the rewiring metal layer 220 are connected by metal leads 280 to form an electrical interconnection. The m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More