Relaxation oscillator

A relaxation oscillator and oscillation circuit technology, applied in the direction of electric pulse generator circuit, differential amplifier to generate pulse, pulse technology, etc., can solve the problems of clock frequency reduction, transistor mobility decrease, increase, etc., to eliminate the influence and improve Frequency stability, effect of reducing temperature sensitivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

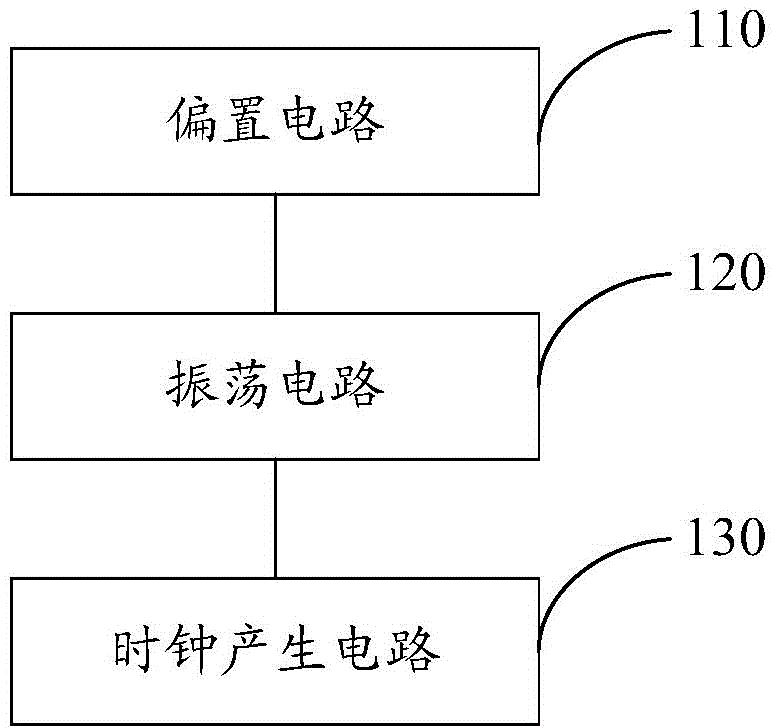

[0041] refer to image 3 , which shows a structural block diagram of an embodiment of a relaxation oscillator in the present invention, which may specifically include:

[0042] A bias circuit 110, configured to generate a bias current, and provide a charging current for the oscillator circuit through the bias current;

[0043] The oscillation circuit 120 is connected to the bias circuit, and is used to integrate the charging current with a capacitor to generate an integrated voltage, generate a reset pulse according to the integrated voltage, and input the reset pulse to the clock generation circuit; as well as

[0044] A clock generating circuit 130, connected to the oscillating circuit, is used to generate a clock signal through the reset pulse, and control switching of switches in the oscillating circuit through the clock signal, so that the oscillating circuit is alternately charged or discharge.

[0045] The relaxation oscillator of the present invention adopts the met...

Embodiment 2

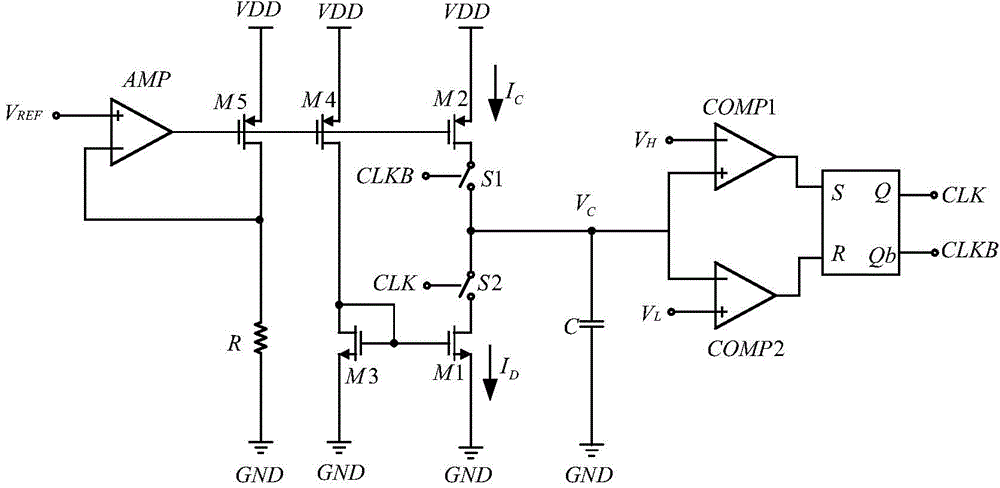

[0047] In order to illustrate the relaxation oscillator proposed by the present invention more clearly, the circuit structures of the bias circuit, the oscillation circuit, and the clock generation circuit will be introduced in detail below.

example 1

[0049] refer to Figure 4 , shows a schematic circuit diagram of a bias circuit of the present invention, the bias circuit may specifically include: a first NMOS transistor M1, a second NMOS transistor M2, a third PMOS transistor M3, a fourth PMOS transistor M4, a first a resistor R1, a second resistor R2, and a power supply VDD;

[0050] Wherein, the gate of M1 is connected to the source of M2, the source of M1 is grounded, the gate of M2 is connected to the drain of M1 and the drain of M3, and the drain of M2 is connected to the drain and gate of M4;

[0051] M3 and M4 form a mirror transistor of a current mirror, the gate of M3 and the gate of M4 are interconnected and connected to the drain of M4, and the source of M3 and the source of M4 are both connected to the power supply VDD;

[0052] R1 and R2 are connected in series, one end of R1 is connected to the source of M2 and the gate of M1, the other end of R1 is connected to one end of R2, and the other end of R2 is grou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More