Patents

Literature

171results about "Pulse generation by differential amplifiers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

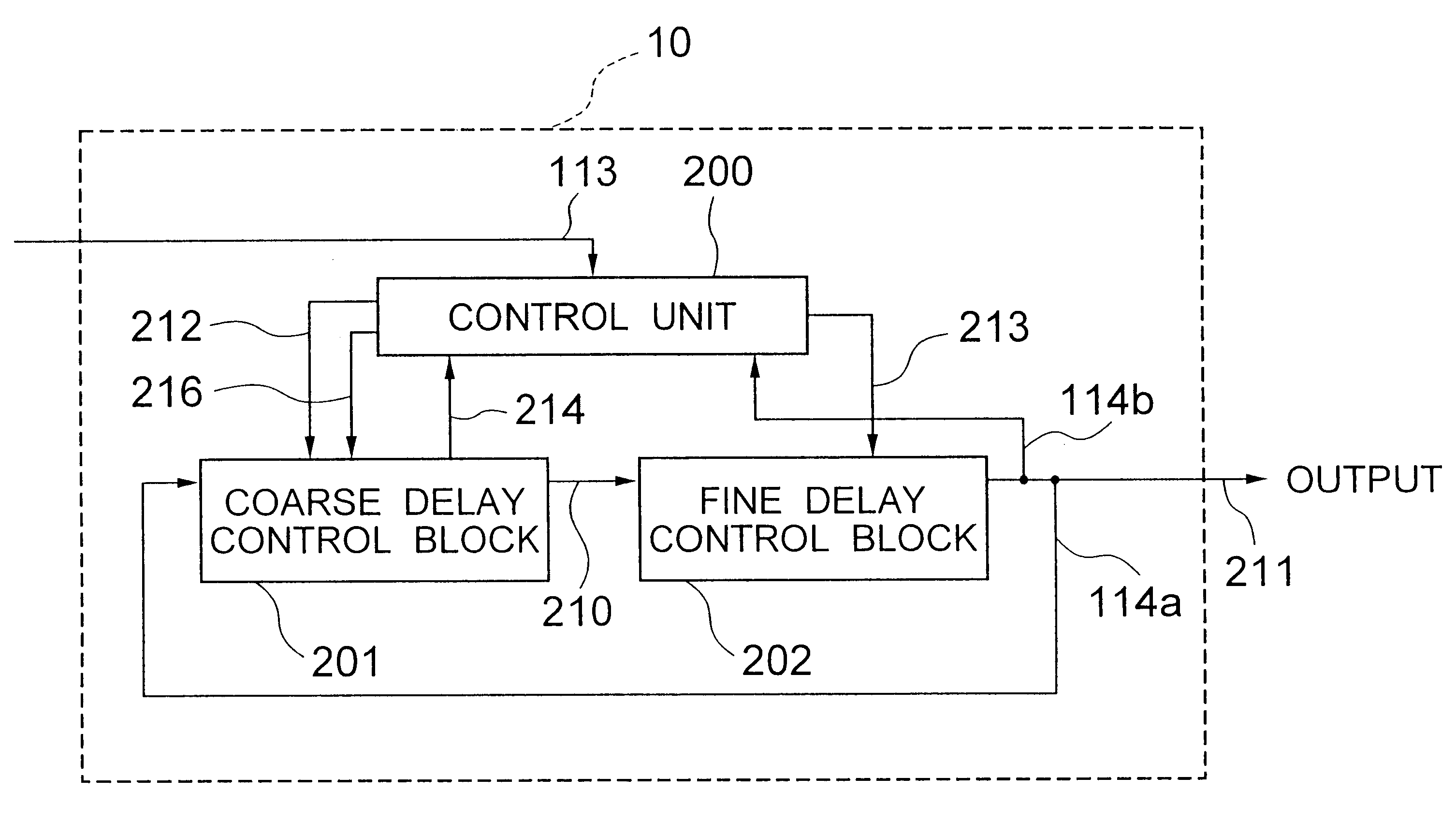

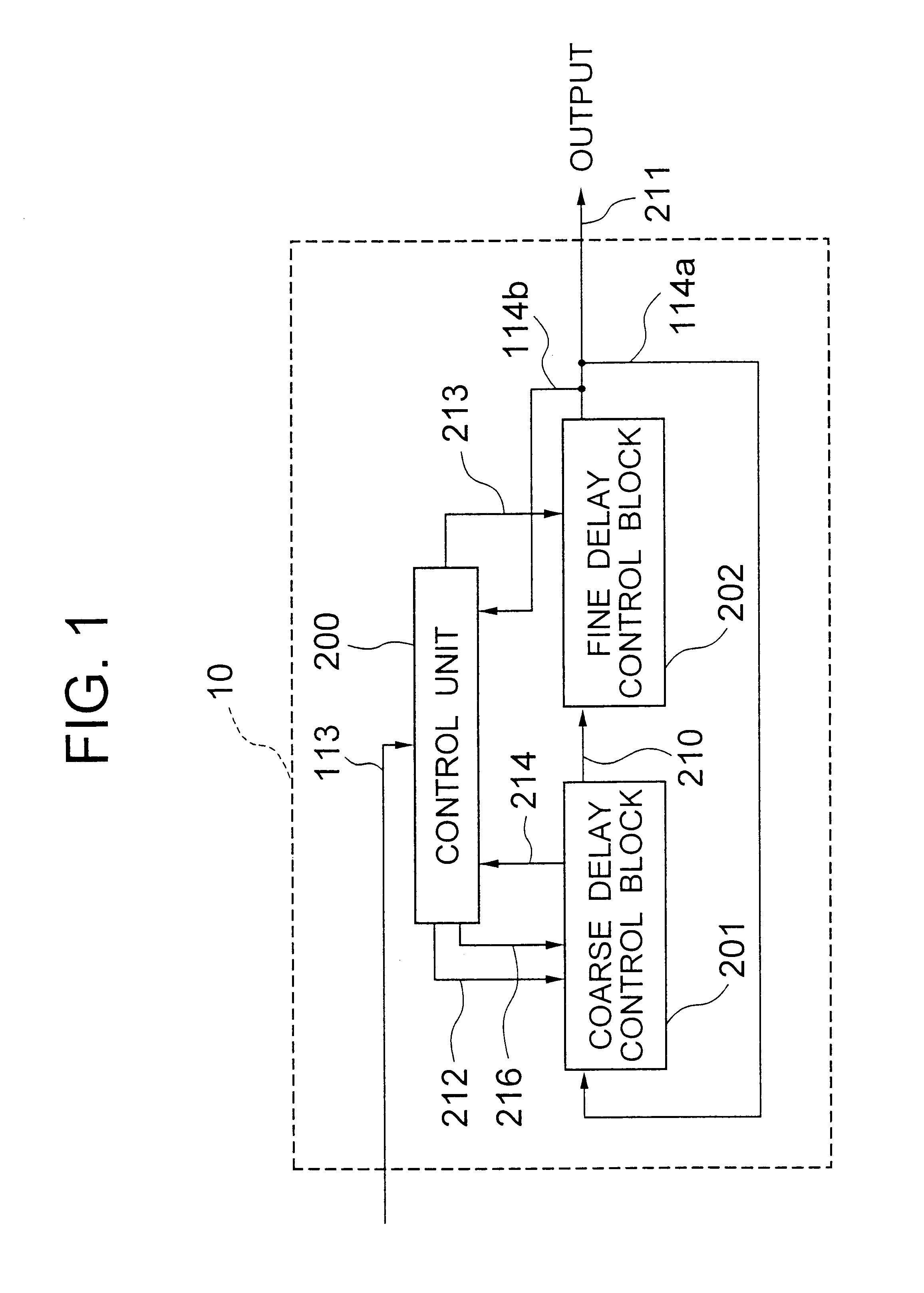

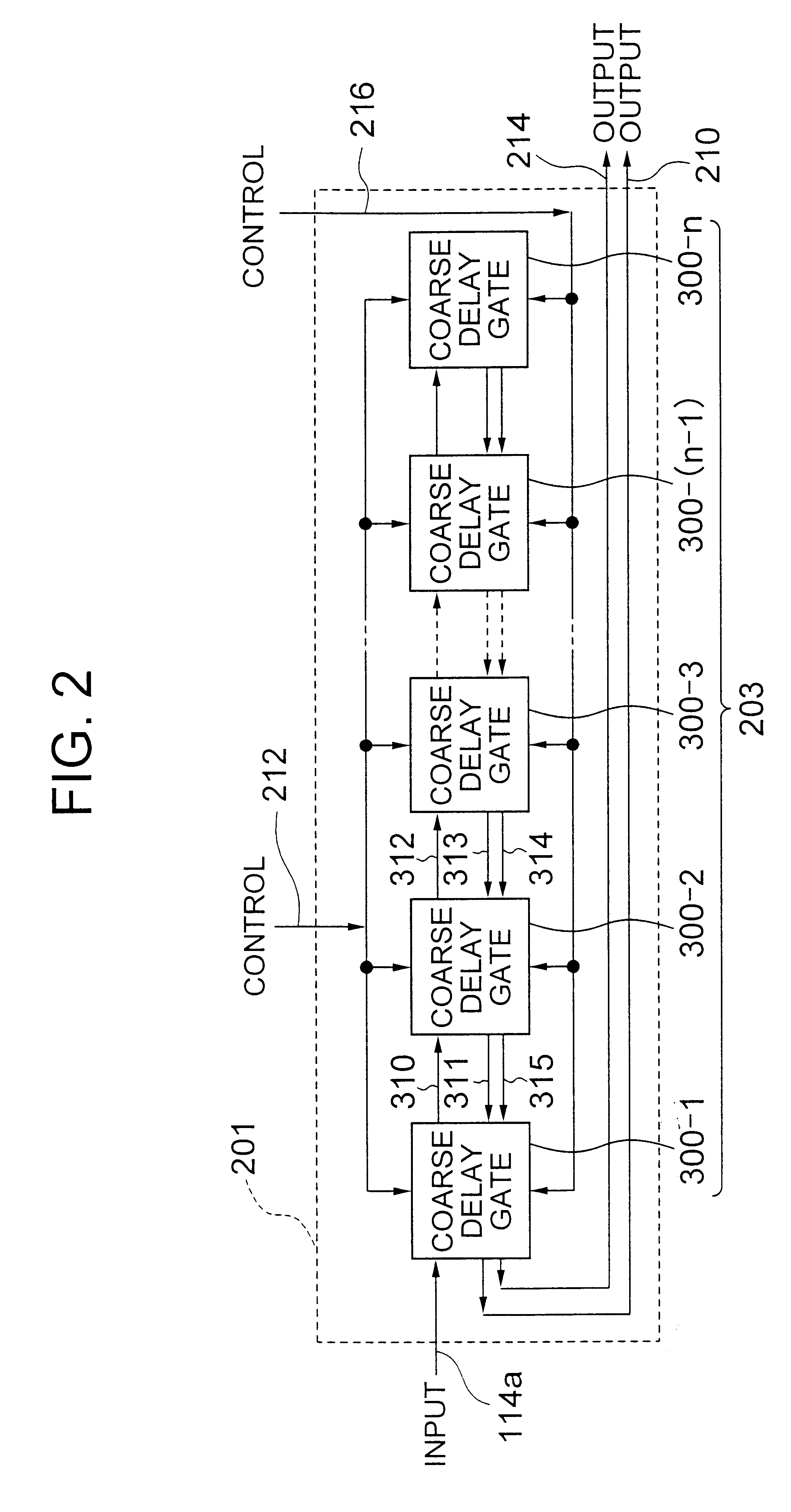

Ring oscillator having variable coarse and fine delays

A ring oscillator includes a coarse delay control block including a plurality of coarse delay gates, and a fine delay control block including a plurality of fine delay gates. The total delay of the fine delay control block is larger than a single delay step of the coarse delay control block, whereby variations of the delay step do not cause an adverse effect on the jitter characteristic of a PLL circuit having the ring oscillator. In a normal operation, the coarse delay control block increments the delay step after the total of the delay steps of the fine delay control block exceeds the delay step of the coarse delay control block.

Owner:RENESAS ELECTRONICS CORP

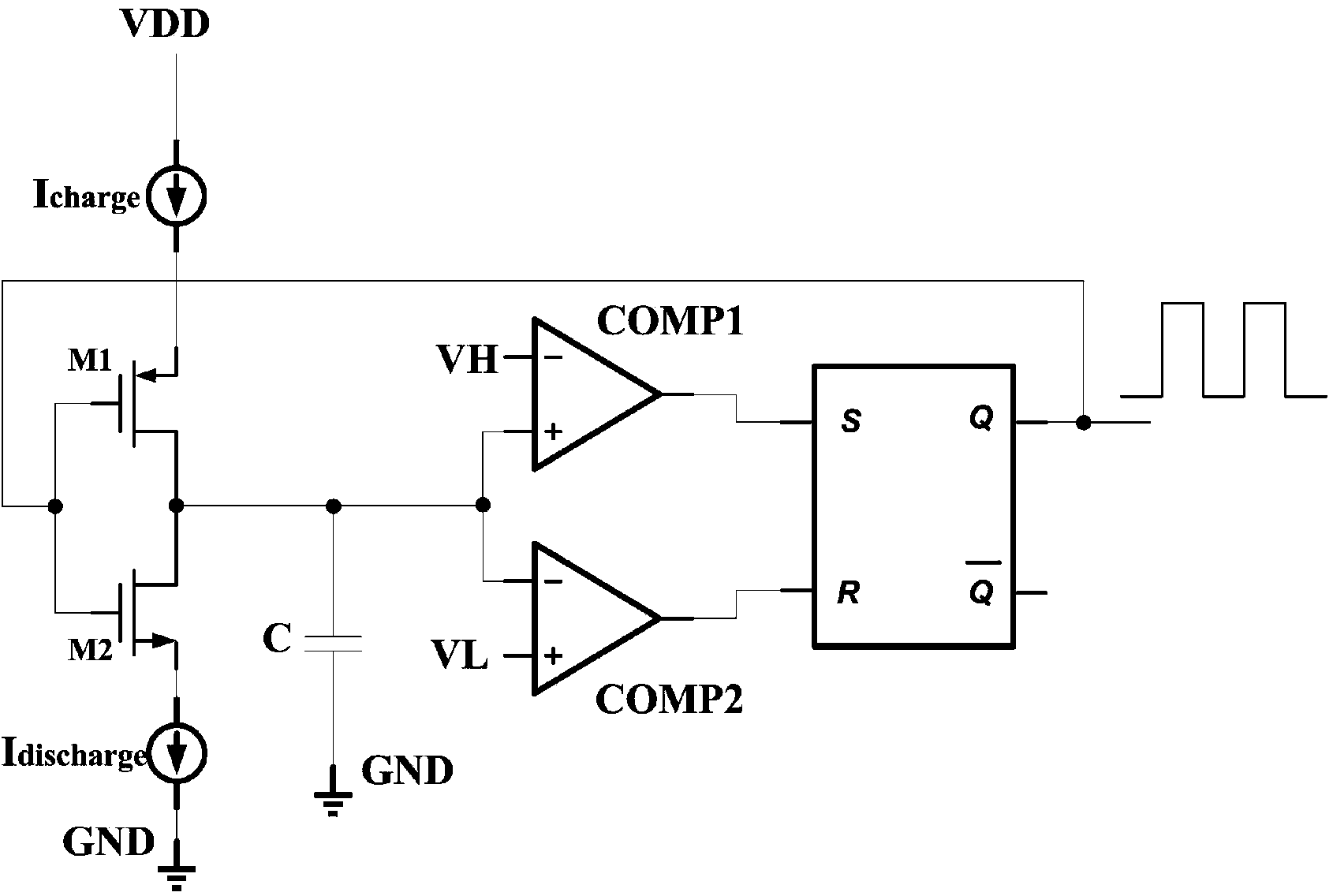

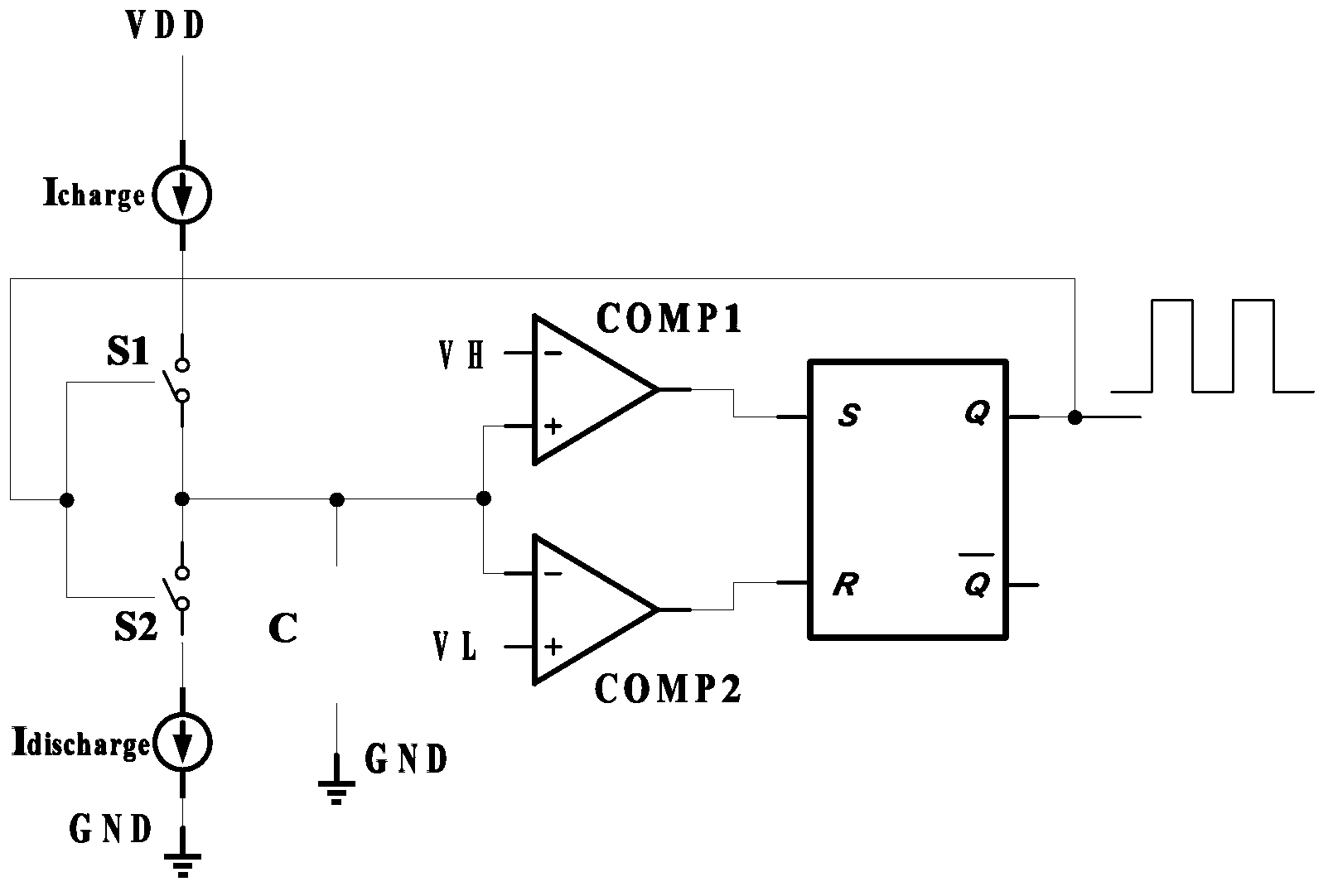

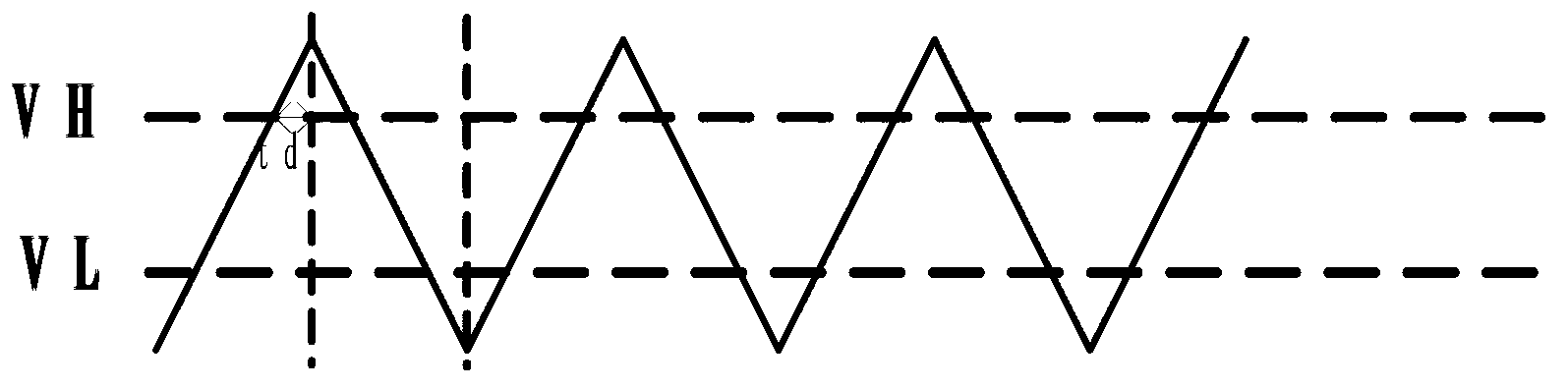

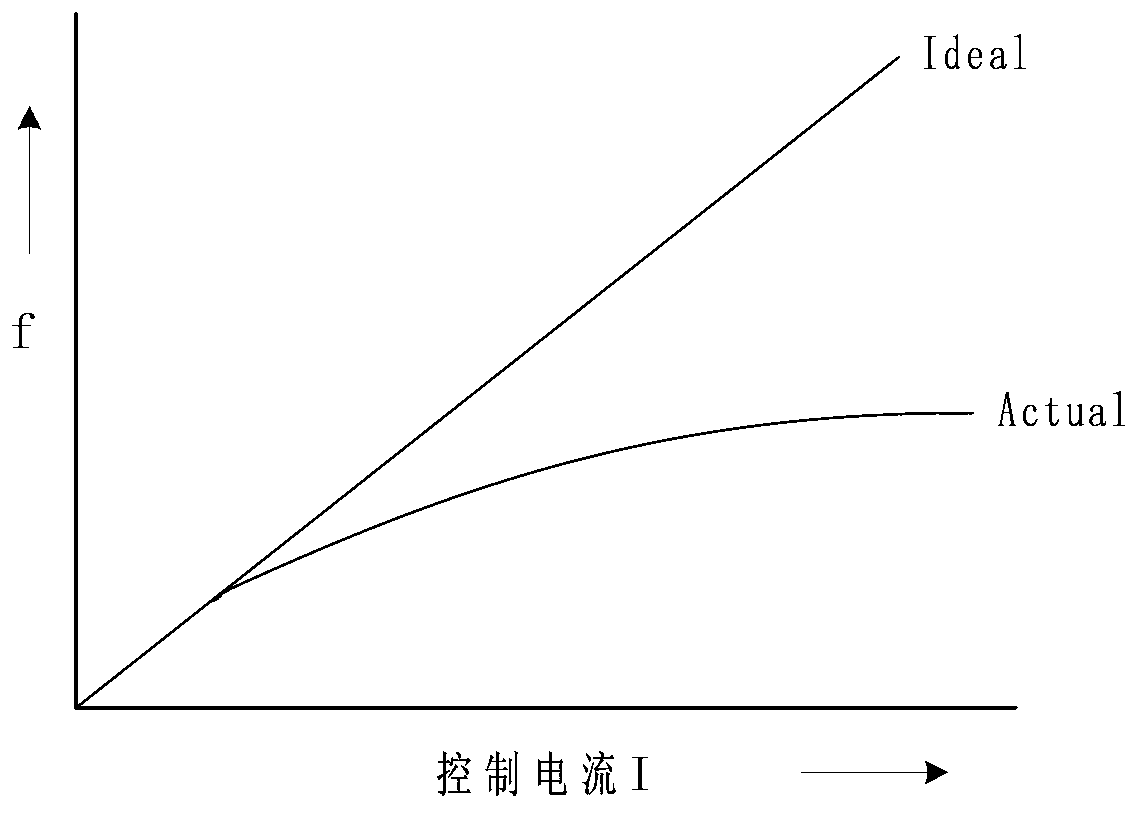

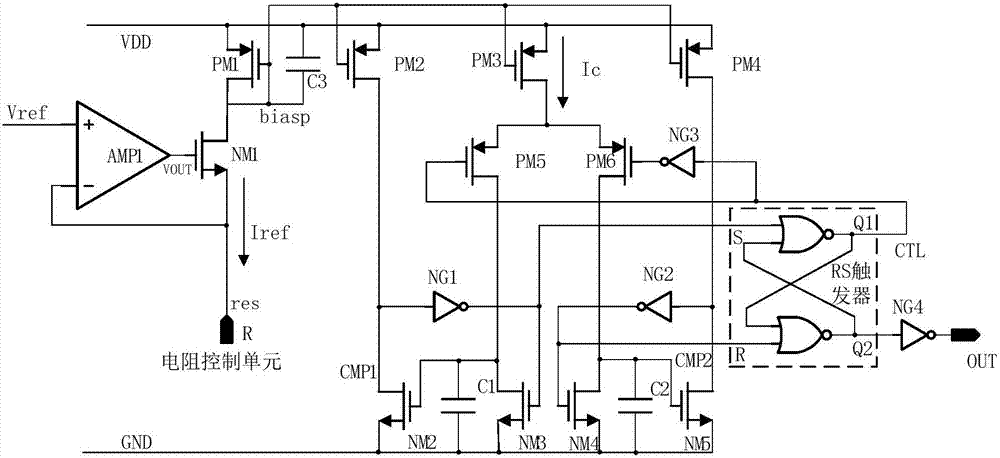

High-linearity relaxation oscillator

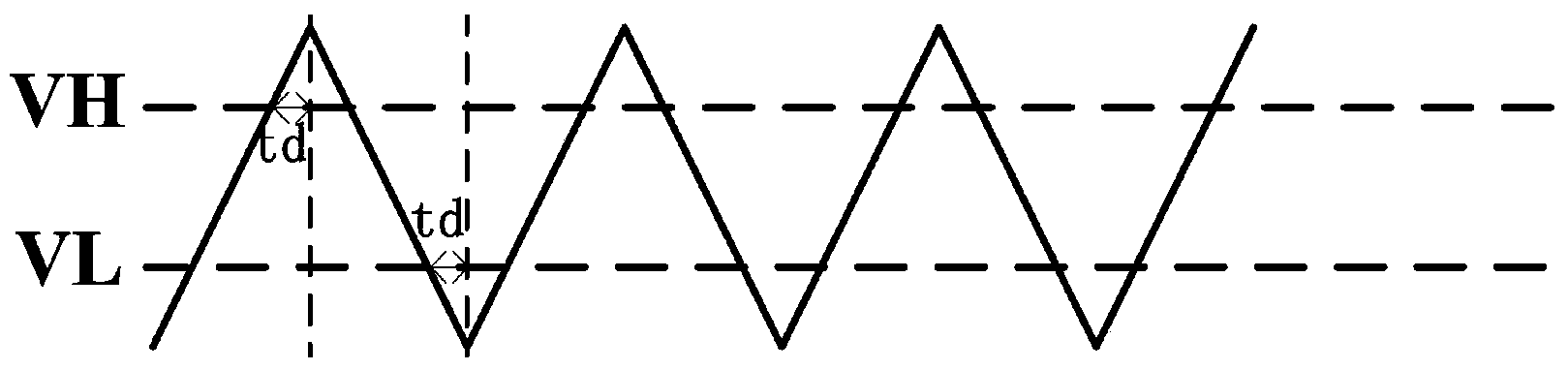

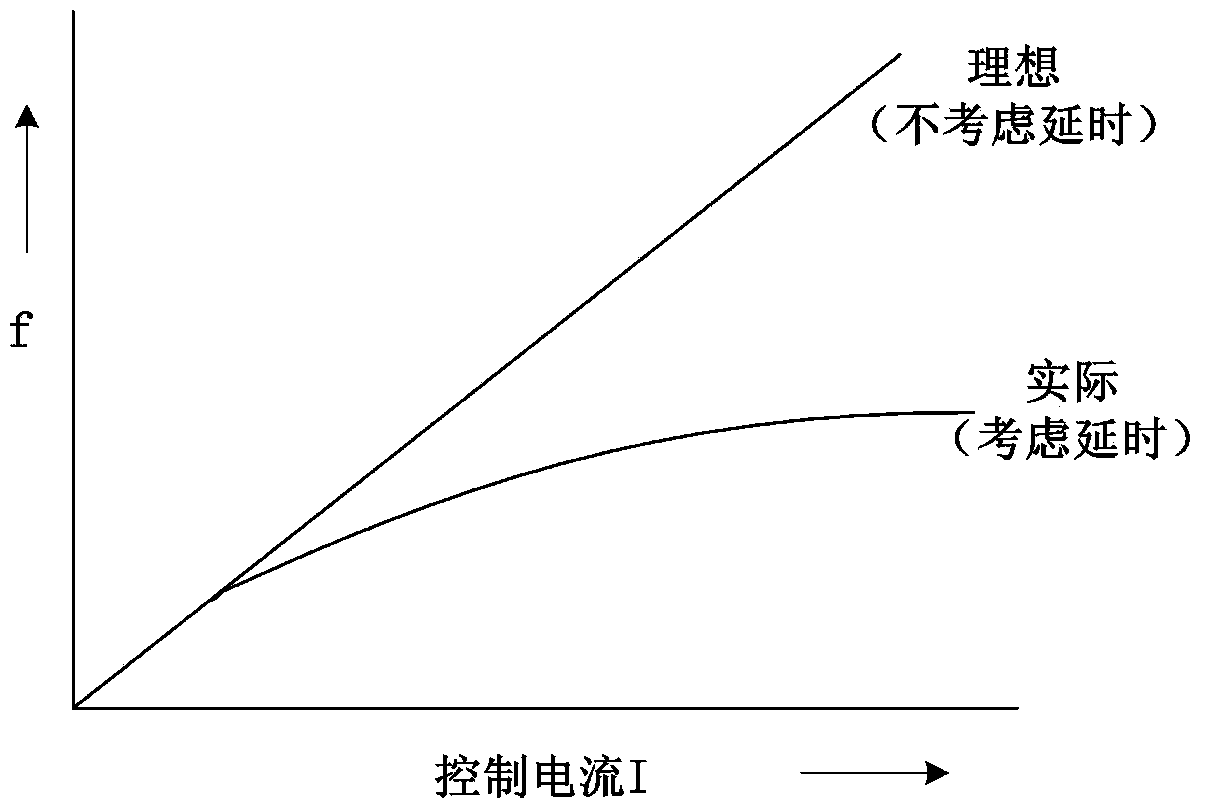

ActiveCN103546123AImprove linearityLong cyclePulse generation by differential amplifiersTransmission gateCapacitor voltage

The invention provides a relaxation oscillator of which the linearity is significantly improved. The relaxation oscillator comprises an oscillating circuit, a reference level self-regulating circuit and a transmission gate selective signal generating circuit. Capacitor voltage overshoot caused by delay of a control circuit is worked out by detecting the voltage peak of charge and discharge capacitors in the oscillating circuit, and accordingly the reference level of comparators in the oscillating circuit is reduced by a corresponding quantity to serve as a new reference level so that the oscillation amplitude of the charge and discharge capacitors can be just a theoretical value. According to the high-linearity relaxation oscillator, when the new reference level is larger than zero, influence, brought by the capacitor voltage overshoot caused by delay of the control circuit, of the charge and discharge capacitors on output frequency is eliminated, and the linearity of a frequency-control circuit of the relaxation oscillator is significantly improved. The transmission gate selective signal generating circuit provides the initial reference level for the comparators by controlling transmission gates and transmits the new reference level to the reverse phase ends of the comparators when the new reference level is generated, and therefore the initial reference level can be isolated from the reverse phase ends of the comparators.

Owner:SOUTHEAST UNIV

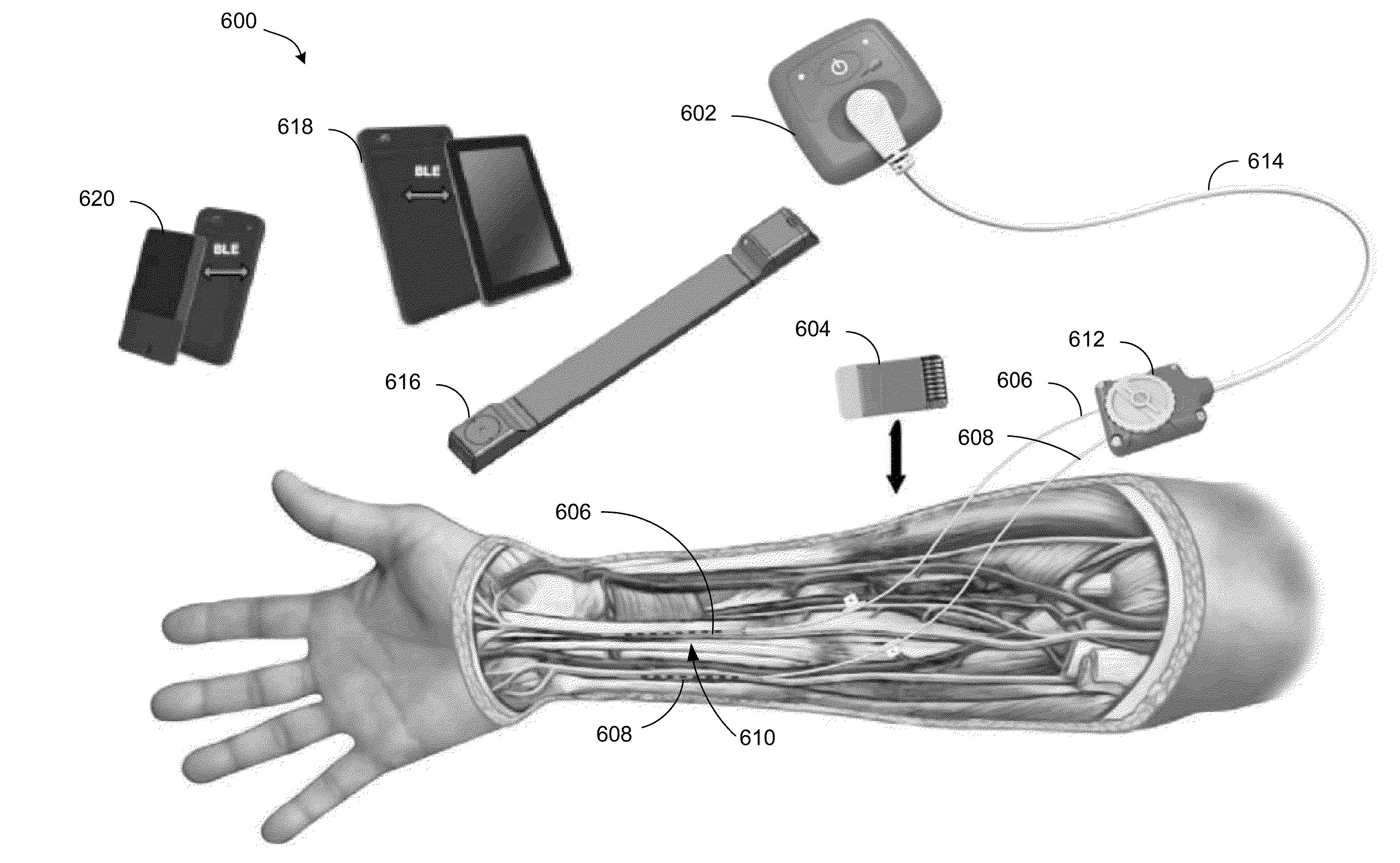

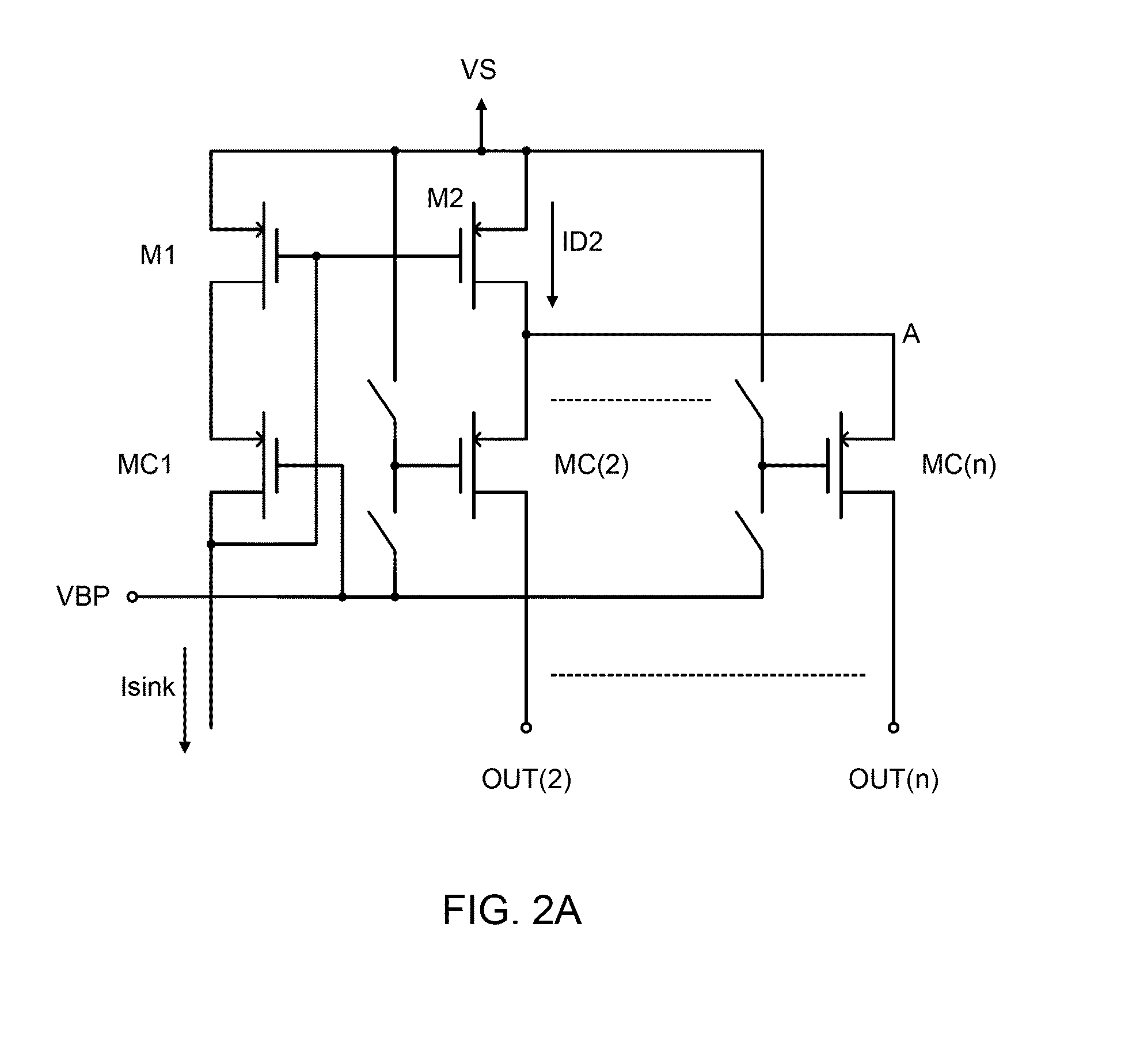

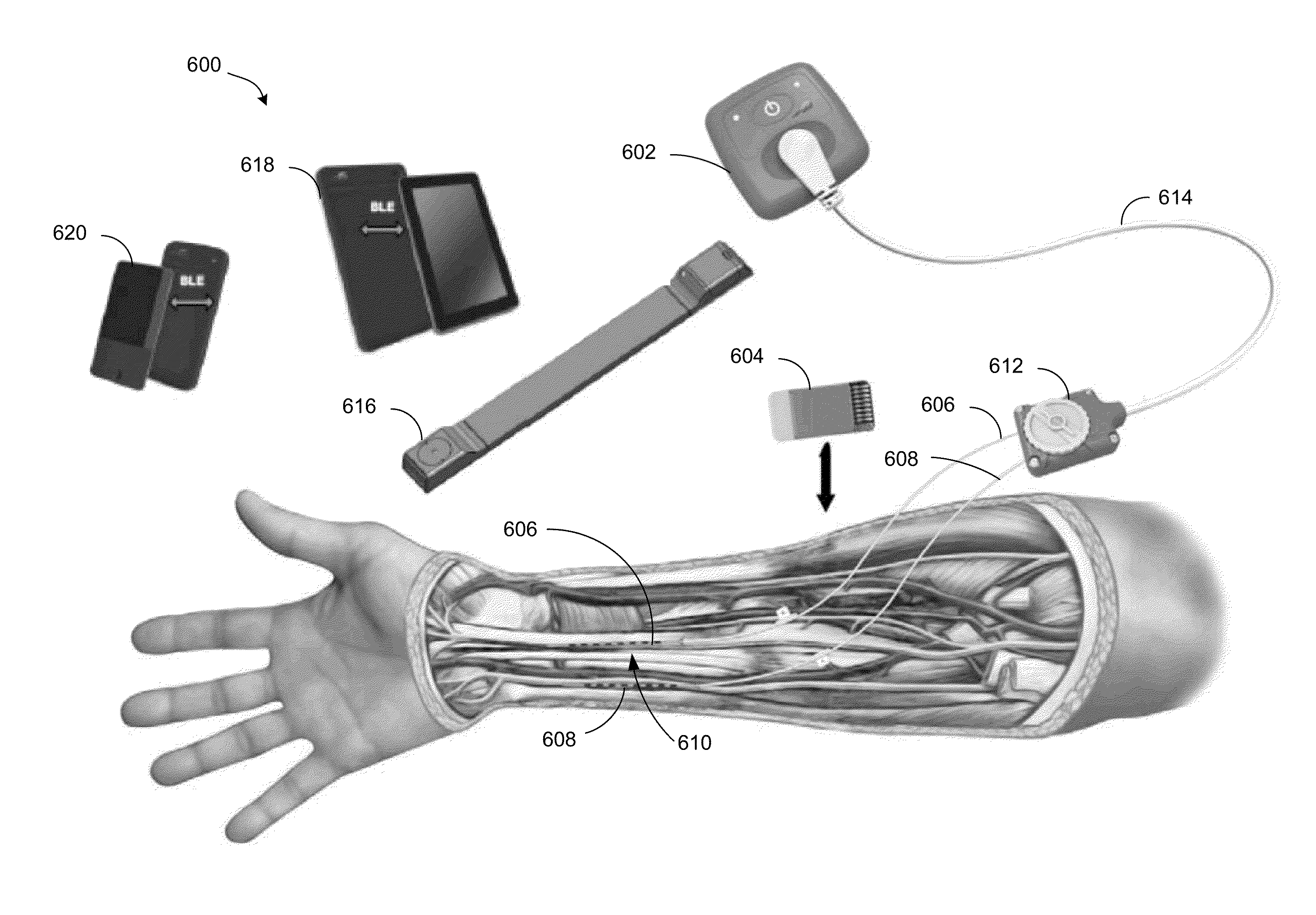

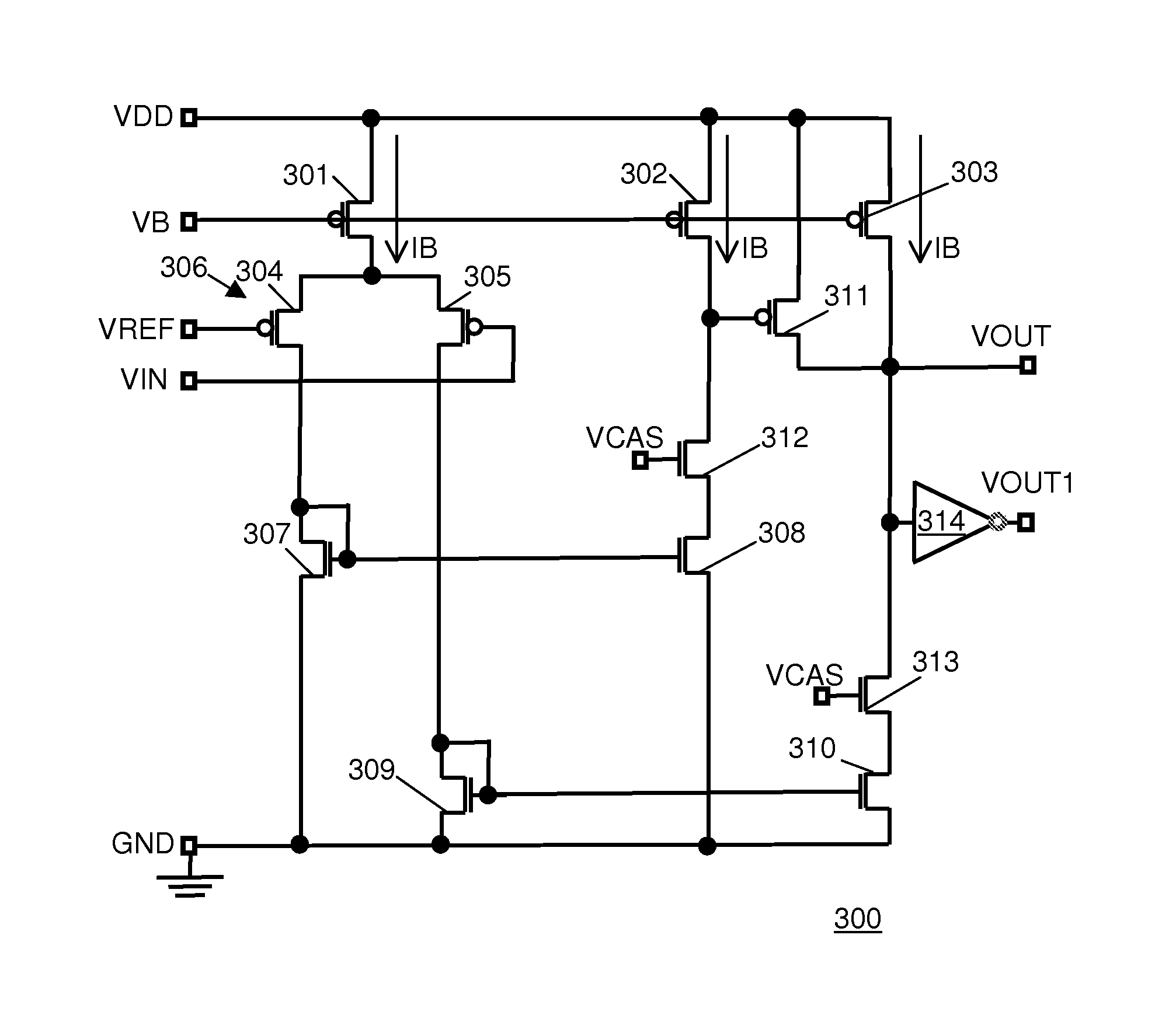

Current sensing multiple output current stimulators

A multiple output current stimulator circuit with fast turn on time is described. At least one pair of input side and output side transistors is arranged in a current mirror connected to a supply transistor by cascode coupling. The output side transistor supplies stimulation current to an electrode in contact with tissue. An operational amplifier connected to a reference voltage and to the output side transistor drives the supply transistor to maintain the voltage at the output side transistor equal to the reference voltage. The at least one pair of transistors includes multiple pairs of transistors whose output side transistors drive respective electrodes with stimulation currents. The stimulator determines the initiation and duration of stimulation current pulses supplied to each electrode. At circuit activation, large currents are generated which discharge capacitances in the output side transistors causing rapid output side transistor turn on.

Owner:ALFRED E MANN FOUND FOR SCI RES

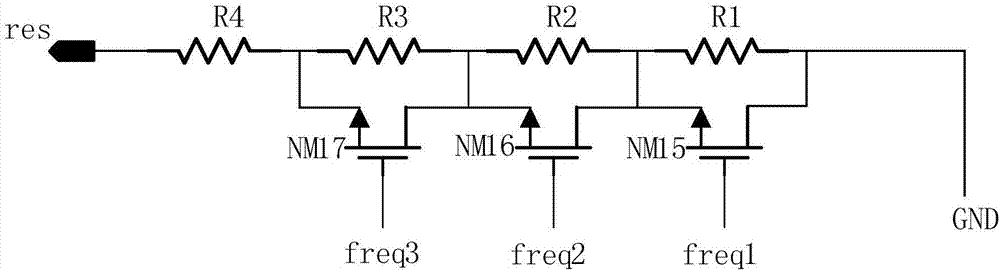

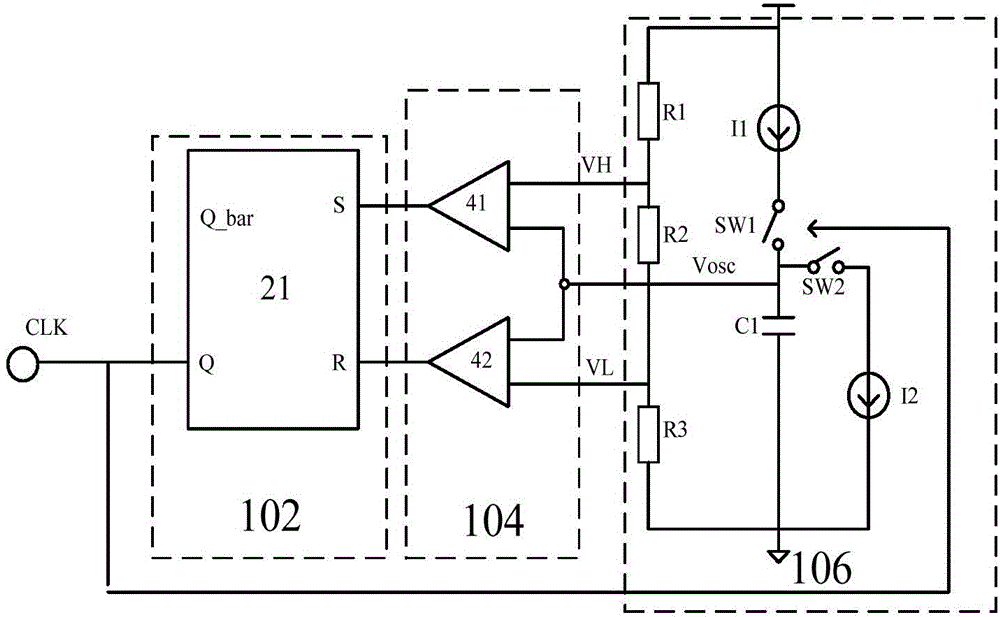

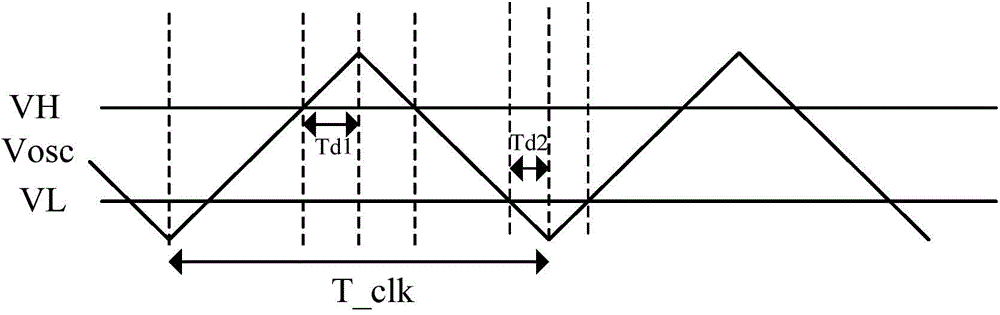

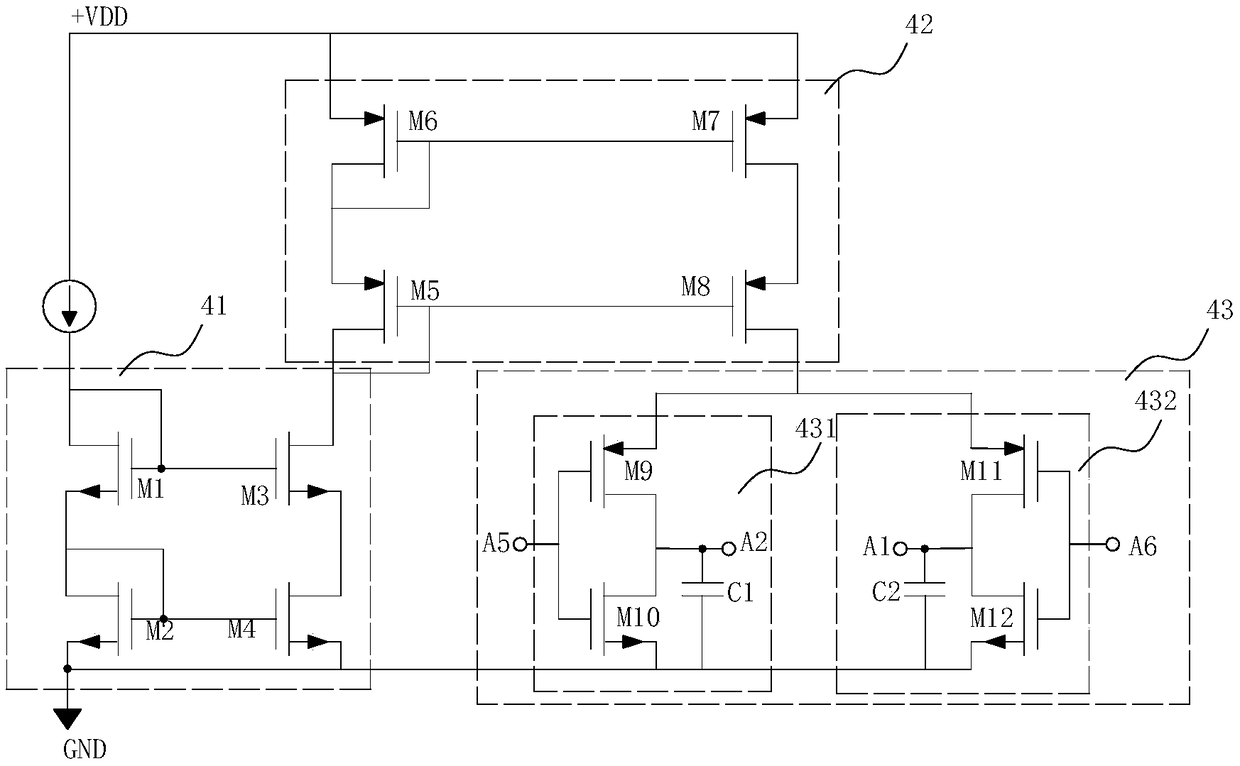

Relaxation oscillator for increasing frequency-control current linearity

ActiveCN103312298AHigh frequencyImprove frequency-control current linearityPulse generation by differential amplifiersFloating chargeControl signal

The invention discloses a relaxation oscillator for increasing frequency-control current linearity. The relaxation oscillator comprises a charge and discharge circuit, a control circuit and a floating charge and discharge capacitor arranged between the charge and discharge circuit and the control circuit. The control circuit detects voltage of the floating charge and discharge capacitor and outputs a control signal. The output signal of the oscillator is determined by only the charge process of the floating charge and discharge capacitor, so that complete-period delay of the oscillator is decreased and frequency-control current linearity of the oscillator is increased. The floating charge and discharge capacitor is formed by parallelly connecting two equal capacitors C1 and C2, and two pole plates of the capacitors C1 and C2 are cross-connected with each other; two ends of the floating charge and discharge capacitor are symmetrical, so that the influence of micro stray capacitance at two ends of the floating charge and discharge capacitor upon the output of the oscillator is decreased.

Owner:SOUTHEAST UNIV

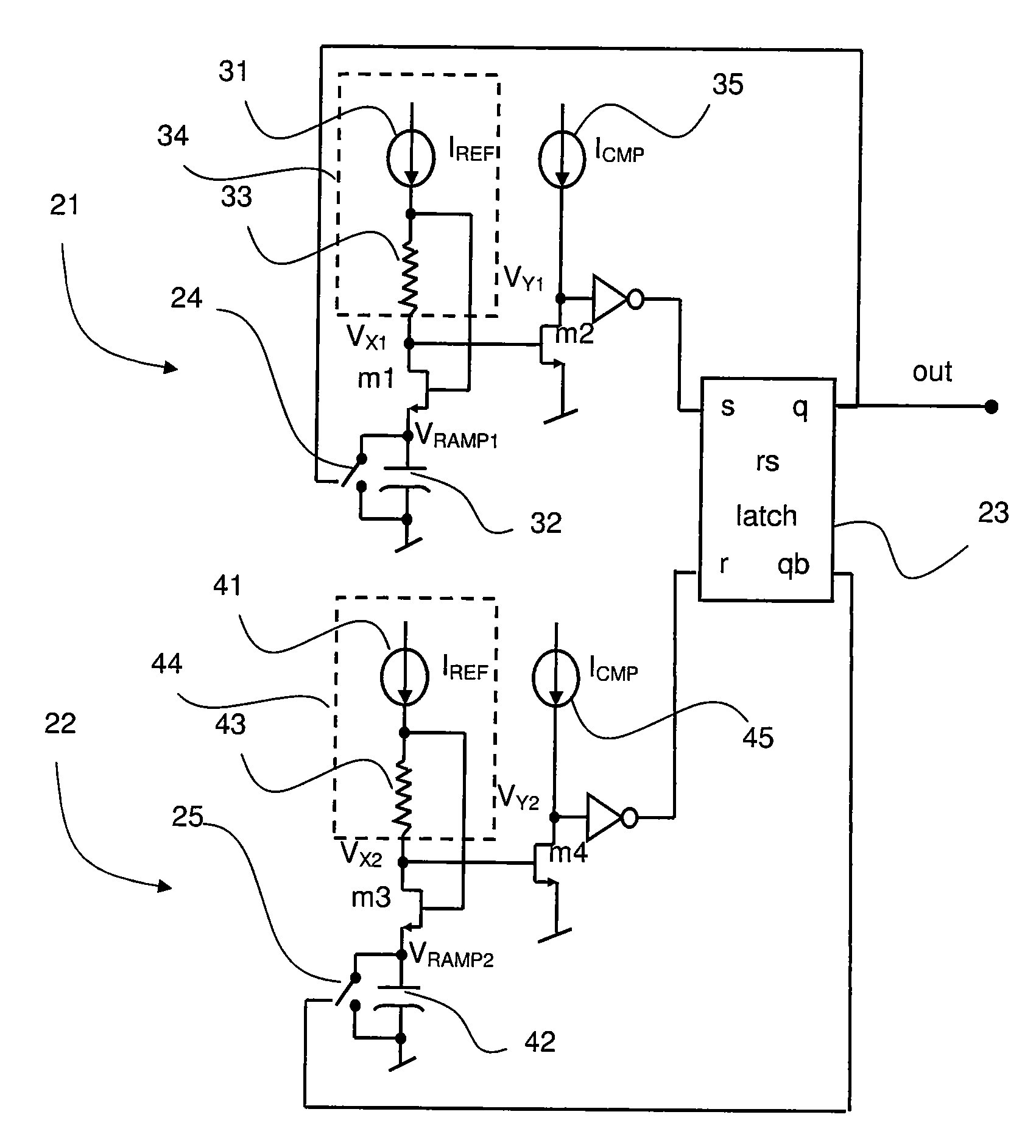

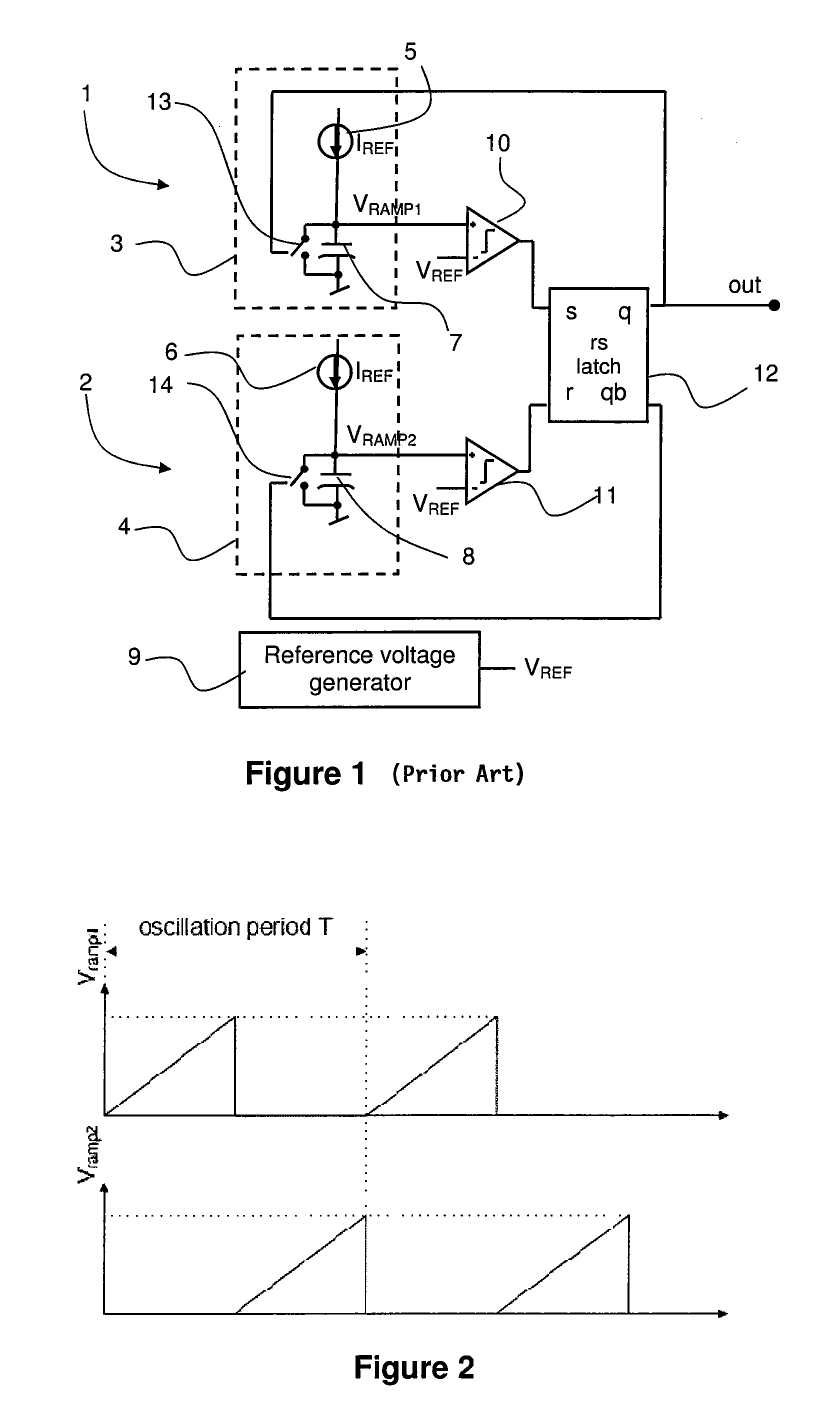

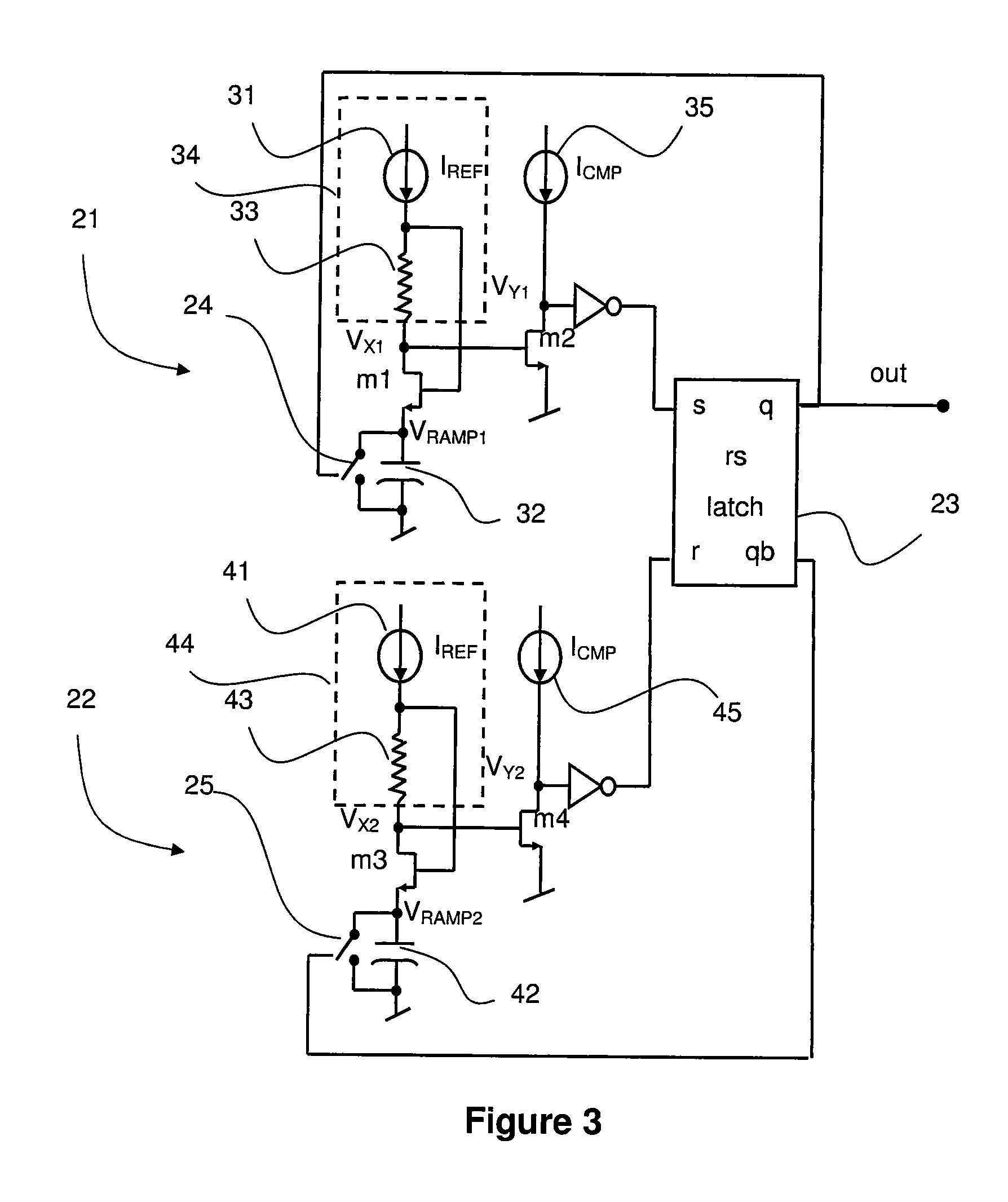

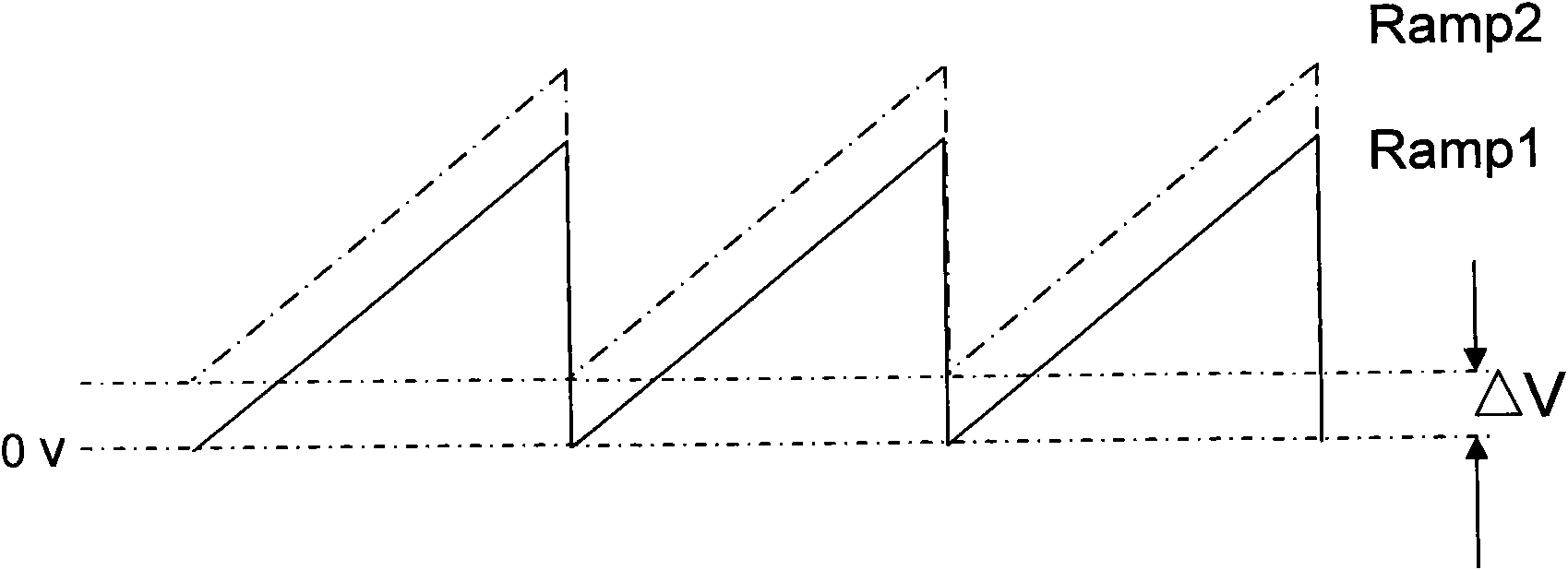

Low-power relaxation oscillator

ActiveUS20100066457A1Reduce current consumptionTotal current dropPulse generation by bipolar transistorsPulse generation by differential amplifiersVoltage referenceRelaxation oscillator

The low-power relaxation oscillator comprises a first module (21) having a ramp generator formed by a reference current source (31) and a storage capacitor (32) defining a ramp voltage (Vramp1), and a voltage comparator (m1, m2) for comparing the ramp voltage with a reference voltage, a second module (22, 41, 42, Vramp2, m3, m4) similar to the first module and an asynchronous flip-flop (23) receiving the output signal of the comparator of the first module at a first input (s) and the output signal of the comparator of the second module at a second input (r). For each module a generator of said reference voltage is configured by adding a reference resistance (33, 43) between the reference current source and the storage capacitor. Thus, the generation of the reference voltage and the ramp voltage is conducted on the very same current branch. This enables the electrical power consumption of the oscillator to be reduced.

Owner:EM MICROELECTRONIC-MARIN

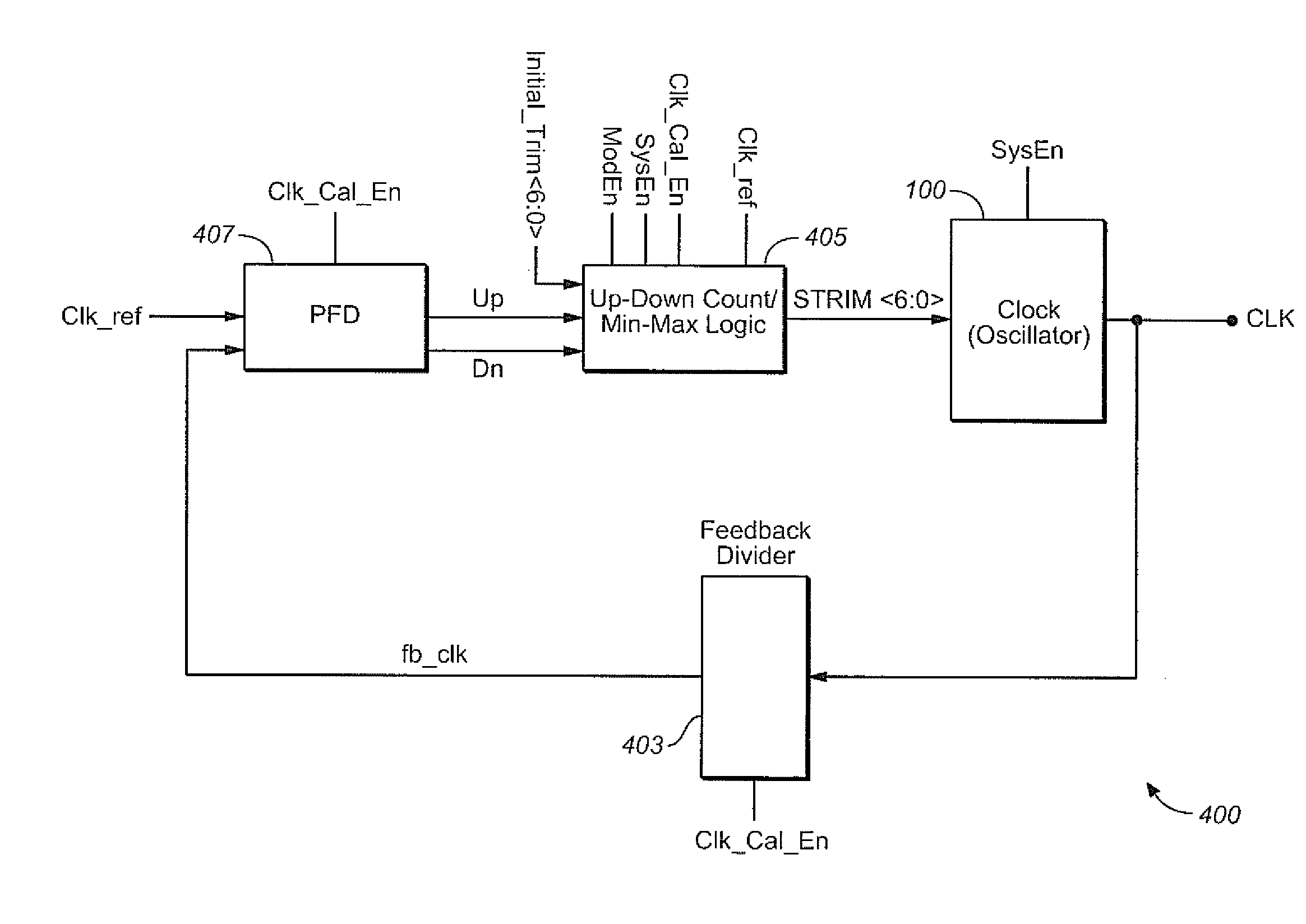

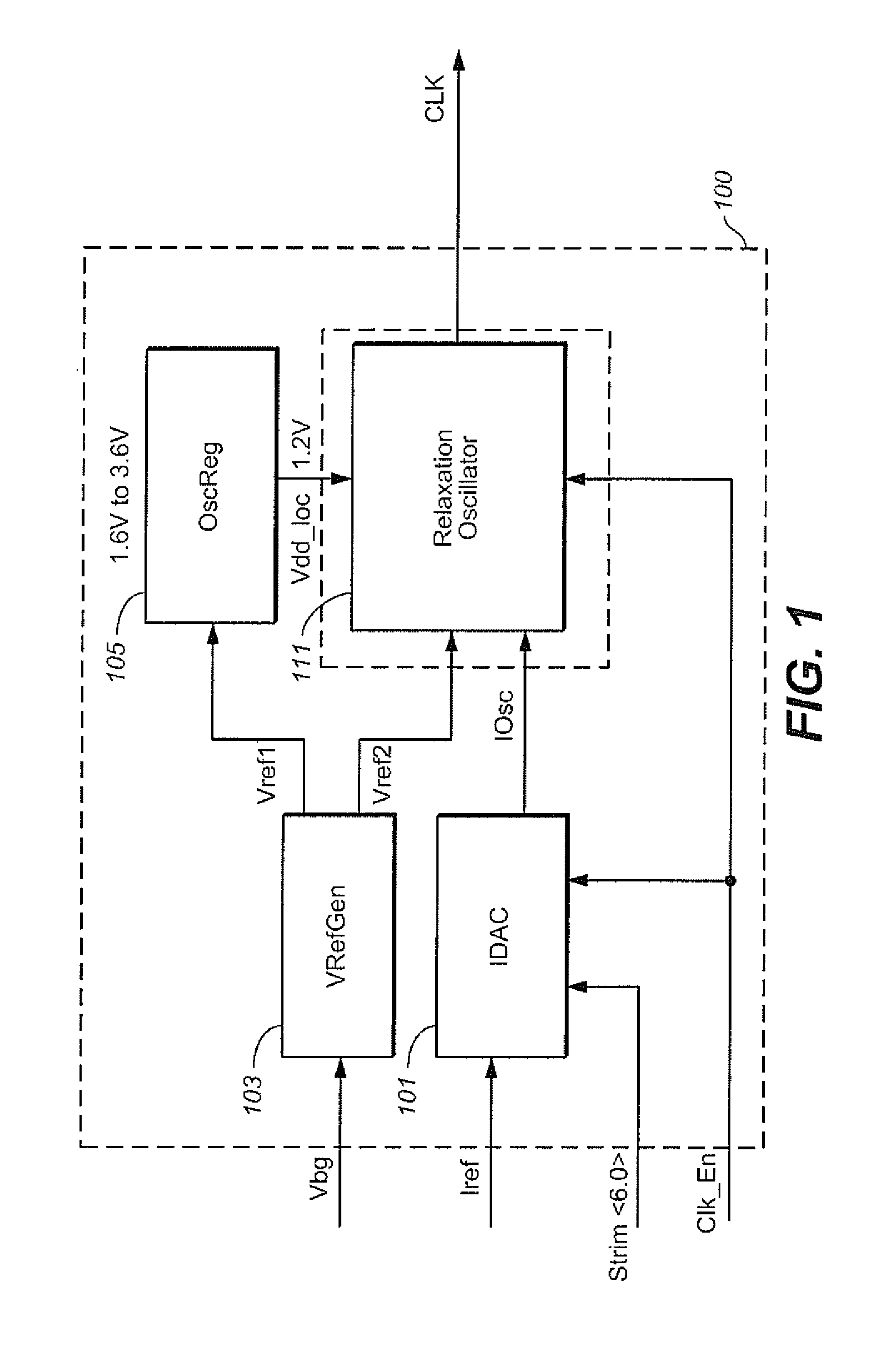

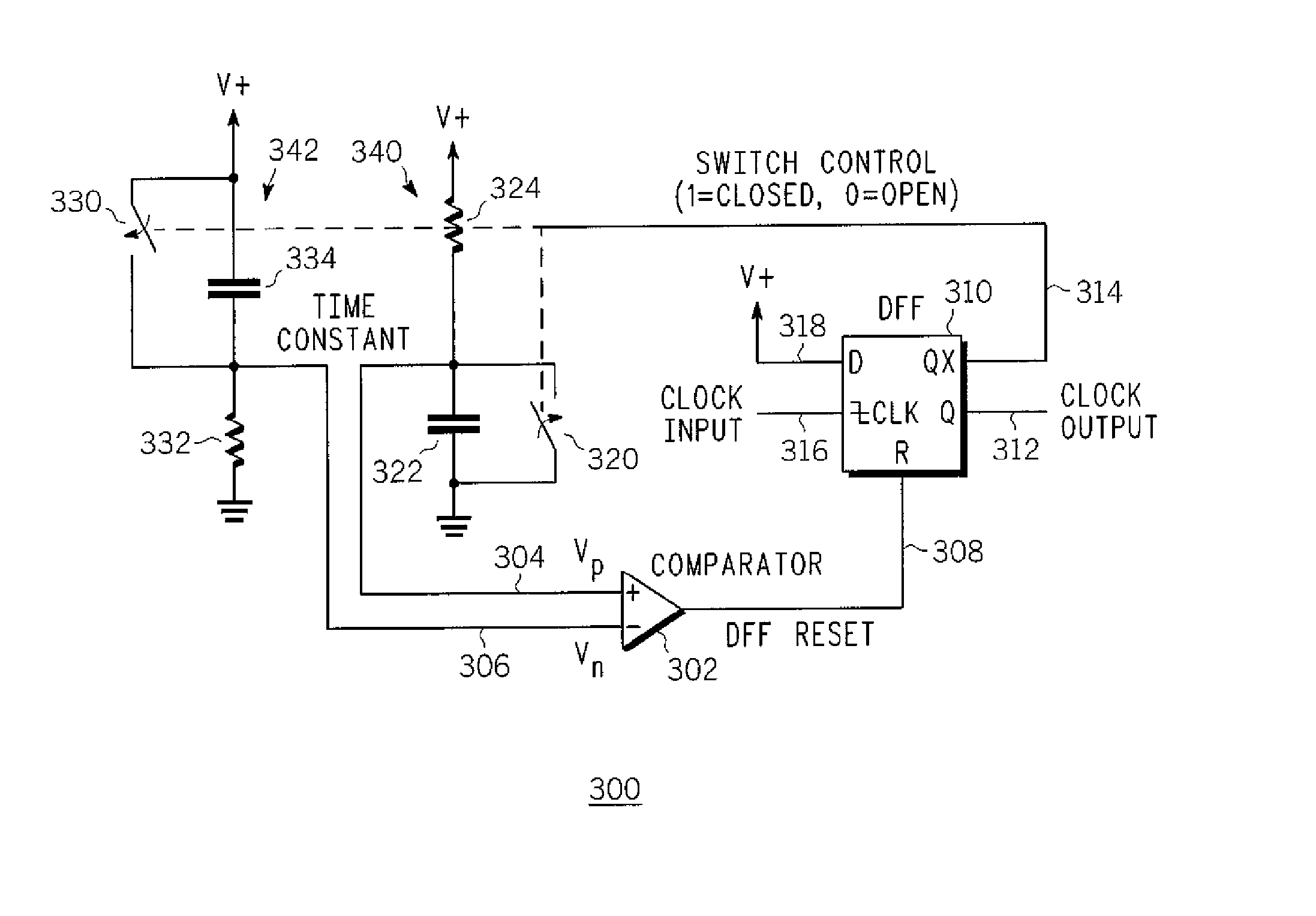

Self-calibrating relaxation oscillator based clock source

ActiveUS8085099B2Pulse automatic controlPulse generation by differential amplifiersClock rateEngineering

A technique and corresponding circuitry are presented for a process independent, self-calibrating relaxation based clock source. The technique and circuitry presented here can reduce the time and cost needed for calibration significantly. The relaxation based clock source produces a clock signal whose frequency is dependent upon a trim value. Starting from an initial trim value, the clock signal is generated, its frequency is compared with a reference clock frequency value, and the trim value is correspondingly adjusted up or down a bit at a time. After this process has continued for a while, min-max logic is used to determine the maximum and minimum trim values and, based on these, the final trim value for the clock is set. This calibration process can also be used to extract whether, and by how much, the implementation on silicon of a particular chip lies in the fast or slow process corners.

Owner:SANDISK TECH LLC

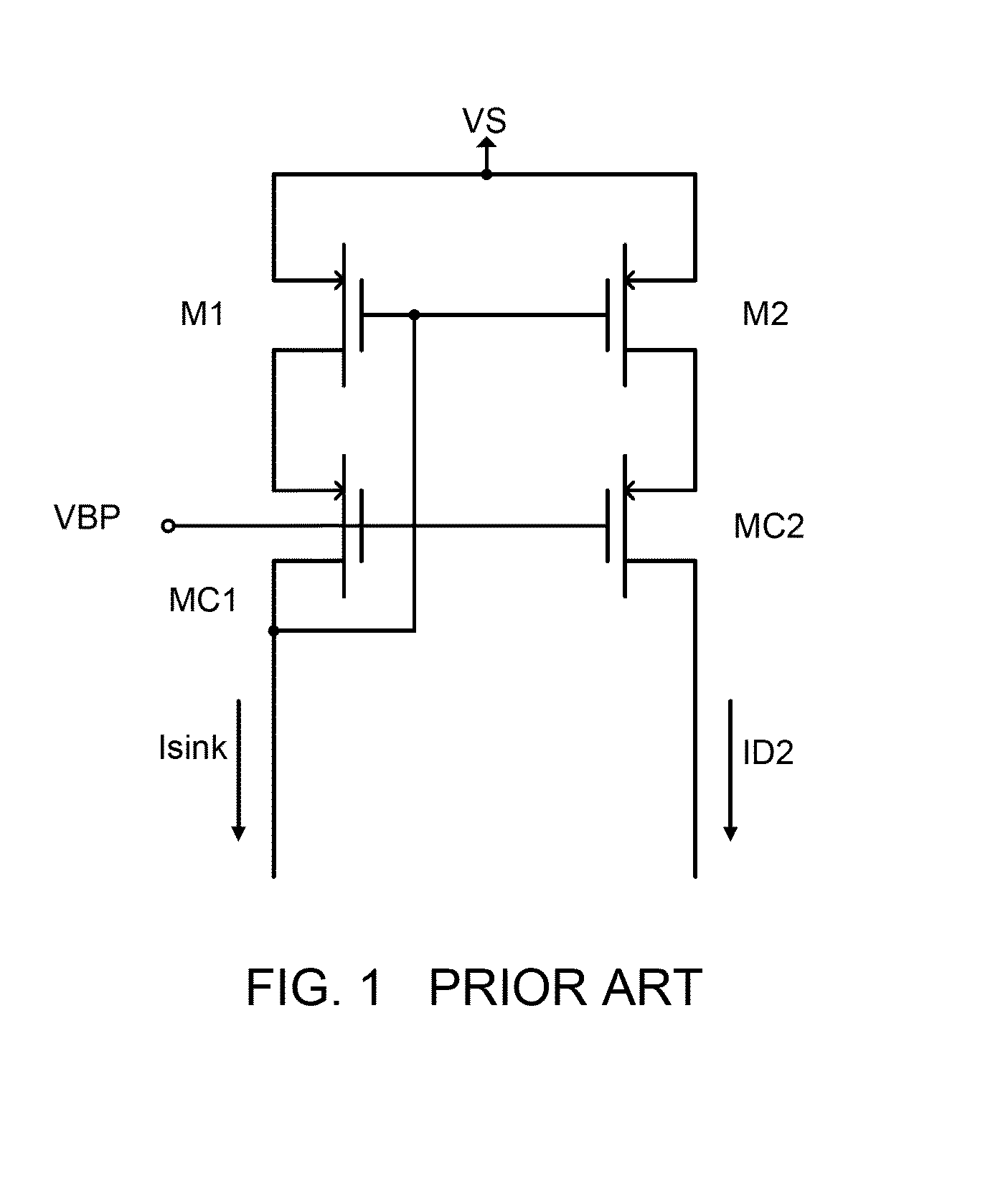

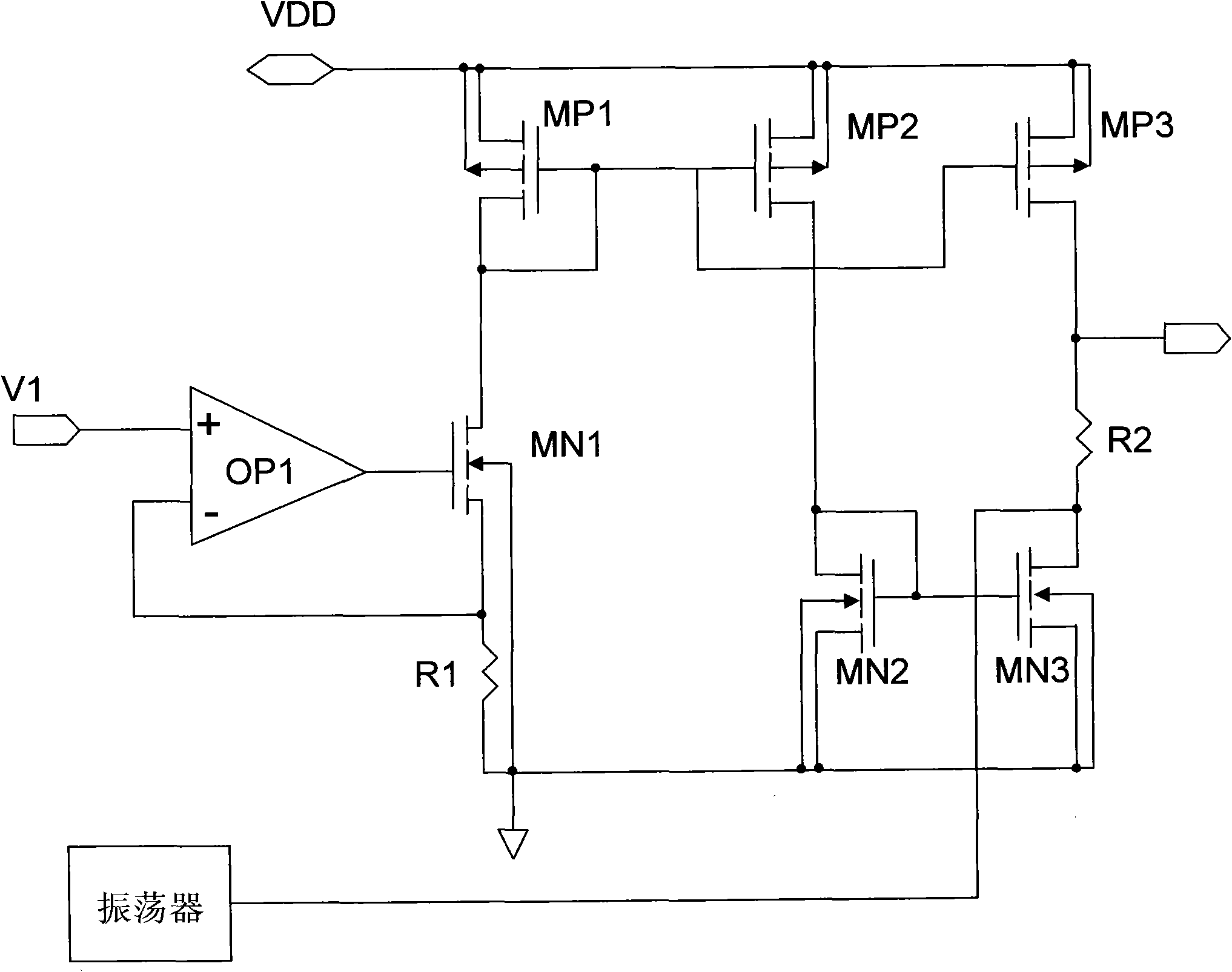

Multi-input comparator and power switching circuit

ActiveCN101847981ASimple designDc-dc conversionPulse generation by differential amplifiersMulti inputPower switching

The invention provides a multi-input comparator comprising a first differential transistor, a second differential transistor, a first resistor and a second resistor, wherein the grid electrode of the first differential transistor is used as the first voltage input end of the multi-input comparator; the first voltage input end receives first voltage; the second differential transistor forming a differential transistor pair with the first differential transistor; the grid electrode of the second differential transistor is used as the second voltage input end of the multi-input comparator; the second voltage input end receives second voltage; one end of the first resistor is connected with the source electrode of the first differential transistor; one end of the second resistor is connected with the source electrode of the second differential transistor; the other end of the first resistor is connected with the other end of the second resistor, wherein a connected node of the first resistor and the first differential transistor is used as the current input end of the multi-input comparator and the current input end is connected with an injection current source; or the connected node of the second resistor and the second differential transistor is used as the current input end of the multi-input comparator, and the current input end is connected with an extraction current source.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

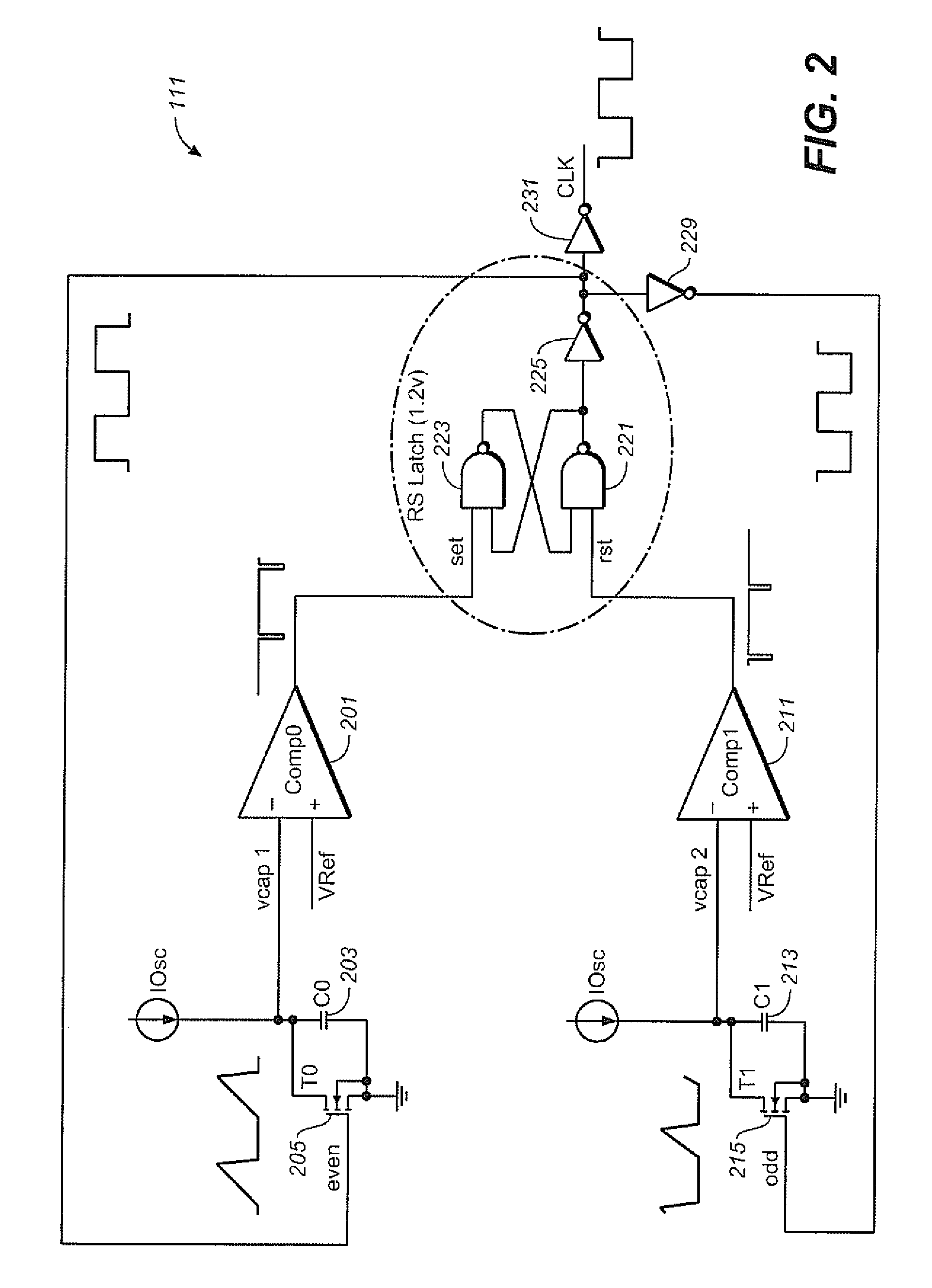

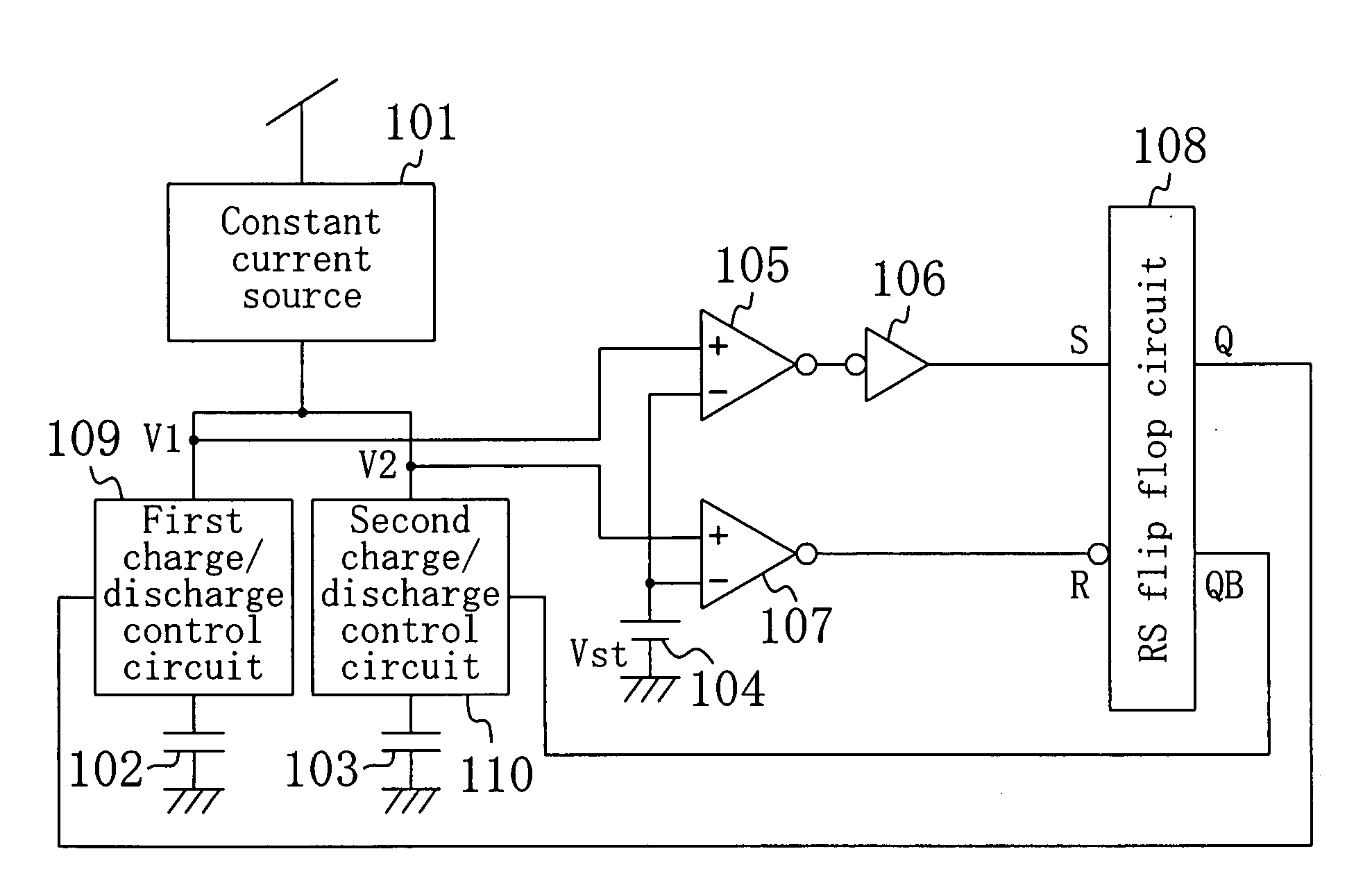

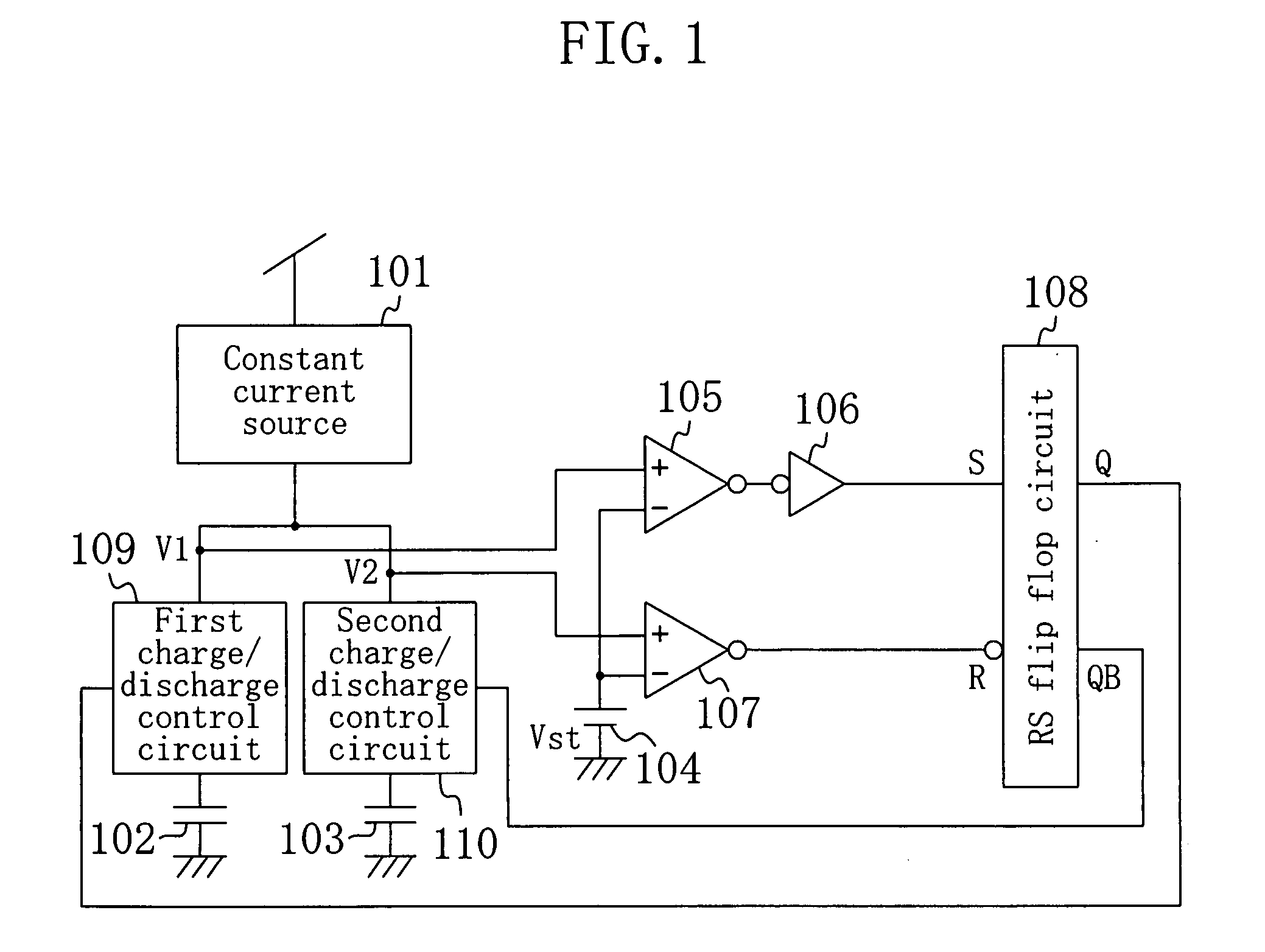

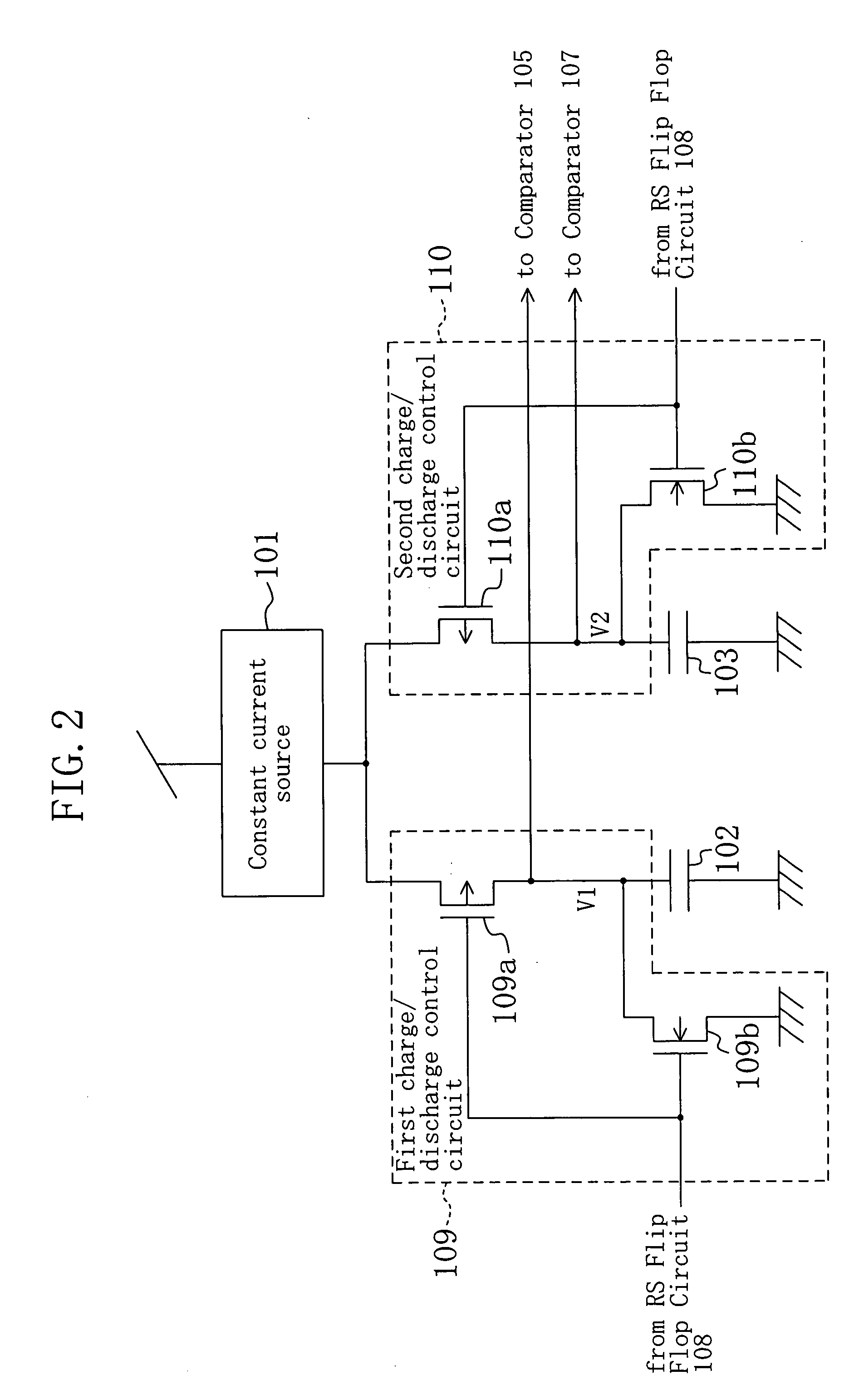

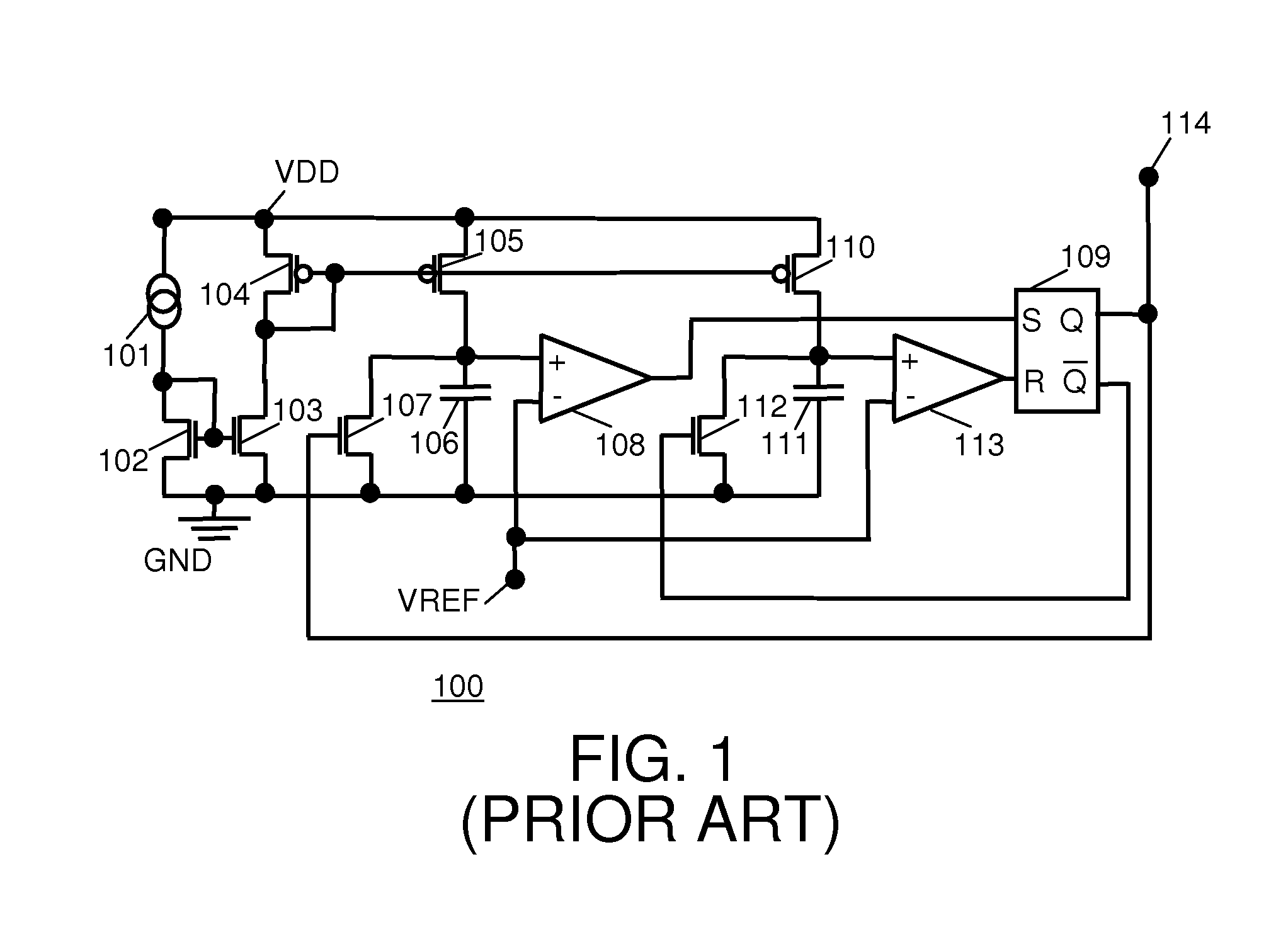

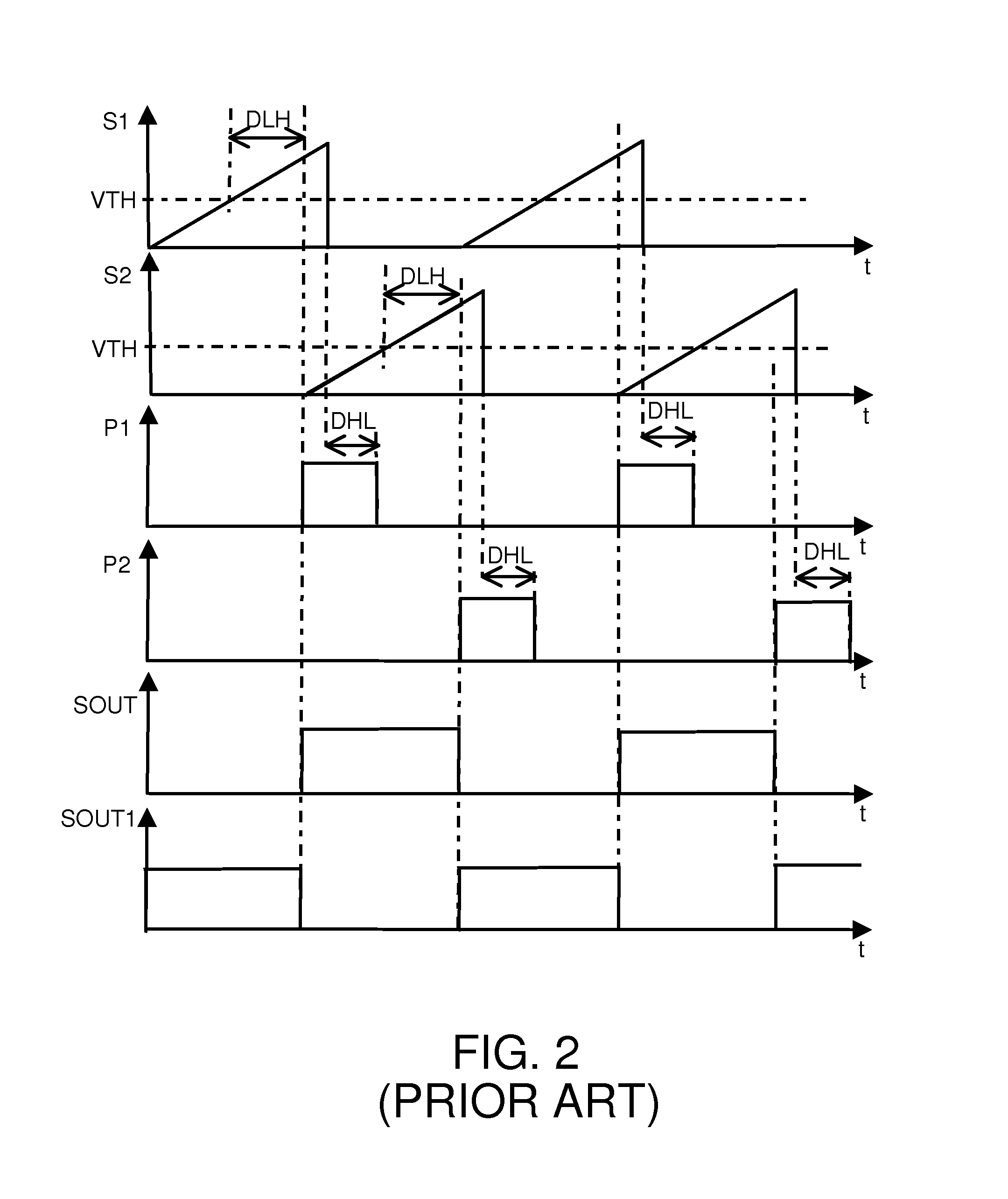

Oscillation circuit

InactiveUS20070182499A1Pulse generation by differential amplifiersOscillations generatorsEngineeringVoltage reference

A first comparator outputs a first signal indicative that a voltage determined according to the amount of charge stored in a first capacitor has reached a first reference voltage. A second comparator outputs a second signal indicative that a voltage determined according to the amount of charge stored in a second capacitor has reached a second reference voltage. An RS flip flop circuit is shifted to a set state by one of the first signal and the second signal and shifted to a reset state by the other signal. When the RS flip flop circuit is in the set state, the first capacitor is in a charge state, and the second capacitor is in a discharge state. When the RS flip flop circuit is in the reset state, the first capacitor is in a discharge state, and the second capacitor is in a charge state.

Owner:PANASONIC CORP

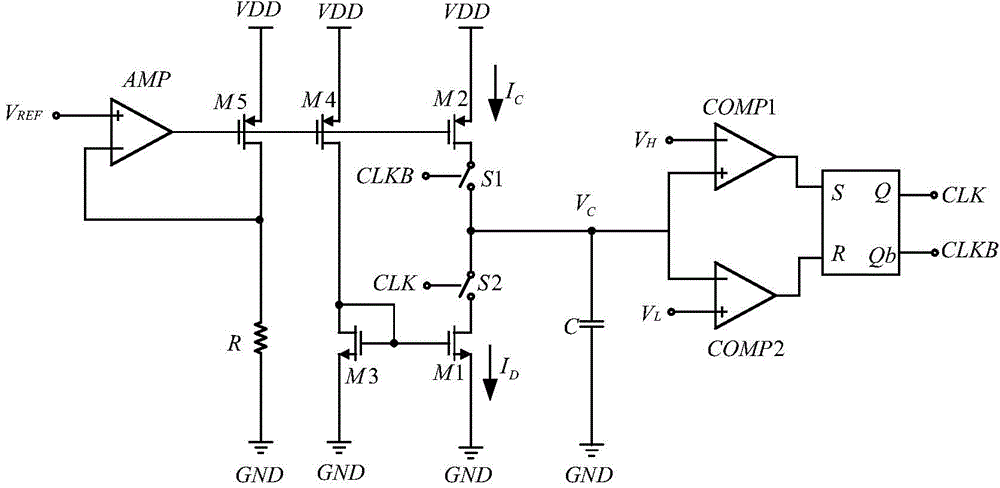

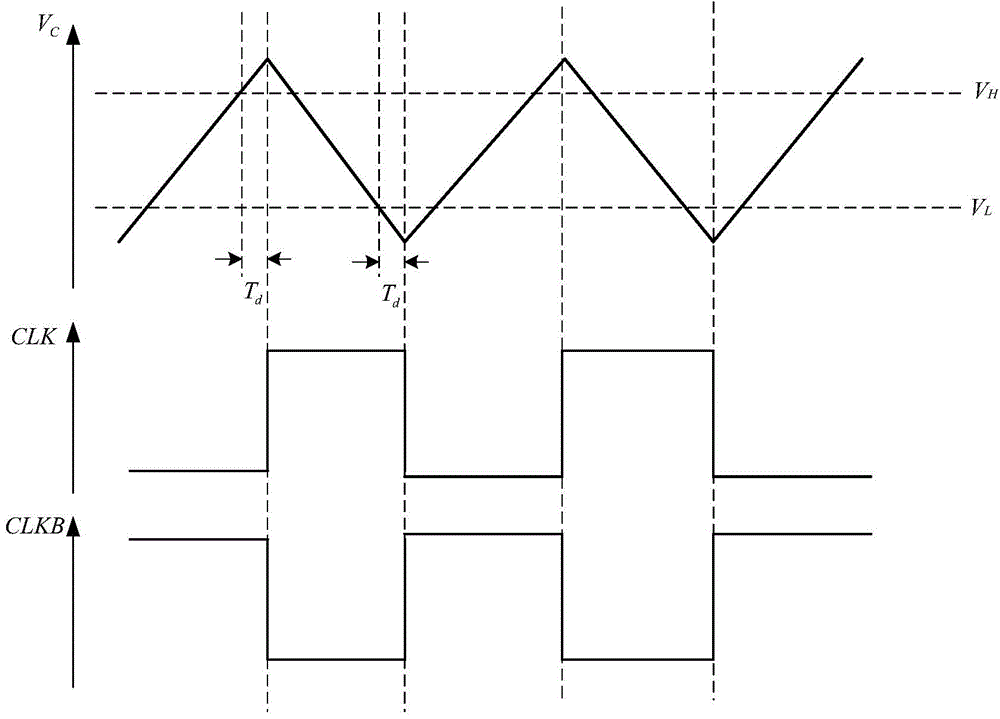

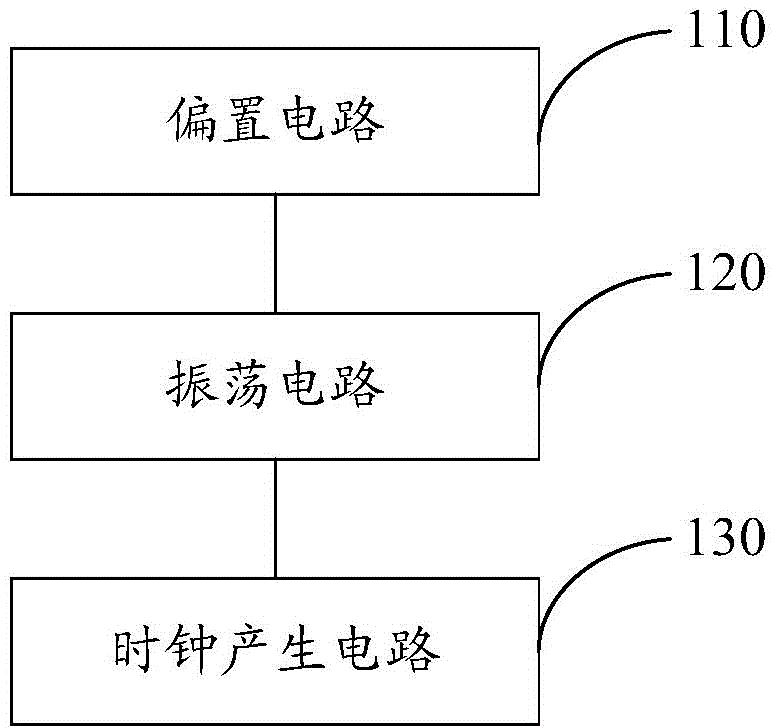

Relaxation oscillator

ActiveCN104579254AImprove frequency stabilityEliminate the effects ofPulse generation by differential amplifiersCapacitancePower flow

The invention provides a relaxation oscillator. The relaxation oscillator comprises a biasing circuit, an oscillation circuit and a clock generation circuit, wherein the biasing circuit is used for producing biasing current and providing charging current for the oscillation circuit through the biasing current; the oscillation circuit is connected with the biasing circuit and is used for integrating the charging current by using a capacitor so as to produce integrator voltage; reset pulse is produced according to the integrator voltage and is input into the clock generation circuit; the clock generation circuit is connected with the oscillation circuit and is used for producing a clock signal through the reset pulse and controlling the switching of a switch in the oscillation circuit through the clock signal, so that the oscillation circuit can alternately charge or discharge. According to the relaxation oscillator, the frequency stability of the relaxation oscillator can be improved.

Owner:GIGADEVICE SEMICON (BEIJING) INC

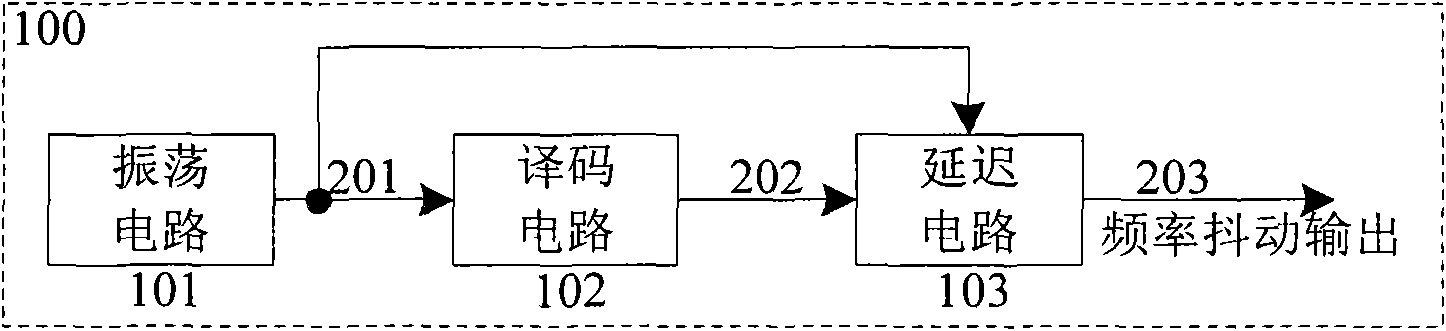

Frequency dithering circuit and frequency dithering method as well as application thereof in switch power supply

InactiveCN101635504AAverage noise reductionLow costDc-dc conversionPulse generation by differential amplifiersDelayed timeSignal delay

The invention provides a frequency dithering circuit and a frequency dithering method. The frequency dithering circuit comprises an oscillatory circuit, a decoding circuit and a delay circuit, wherein the oscillatory circuit generates an oscillatory frequency output signal; the oscillatory frequency output signal controls the decoding circuit to generate a plurality of pulse output signals; and the delay circuit generates a frequency dithering output signal when the oscillatory frequency output signal passes by the delay circuit; the frequency dithering output signal delays for a period of time compared with the oscillatory frequency output signal; and the pulse output signals control the delay time of the oscillatory frequency output signal. The invention applied in a switch power supply can reduce the EMI average noise of the switch power supply and has energy spectrum density planarization.

Owner:HANGZHOU SILAN MICROELECTRONICS

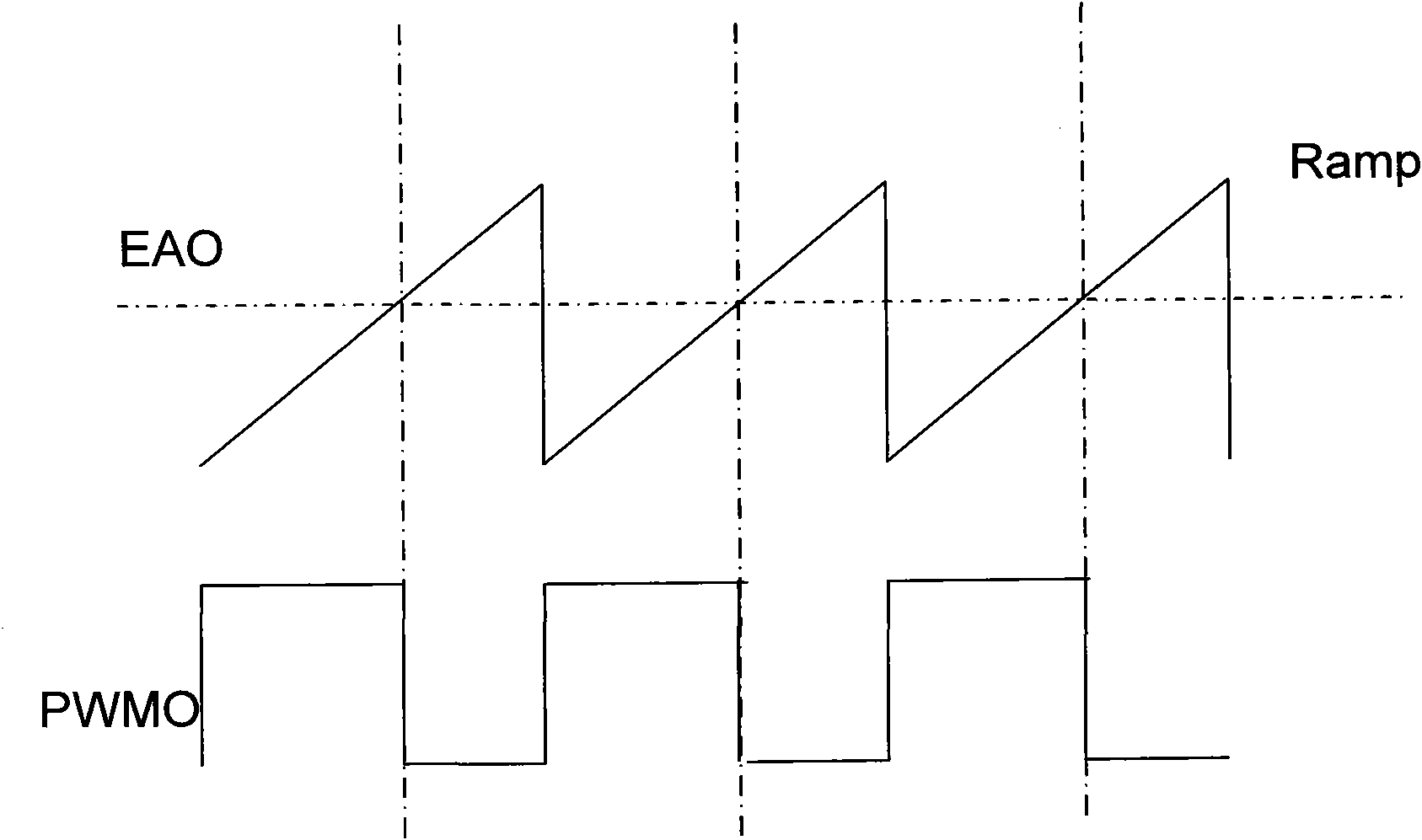

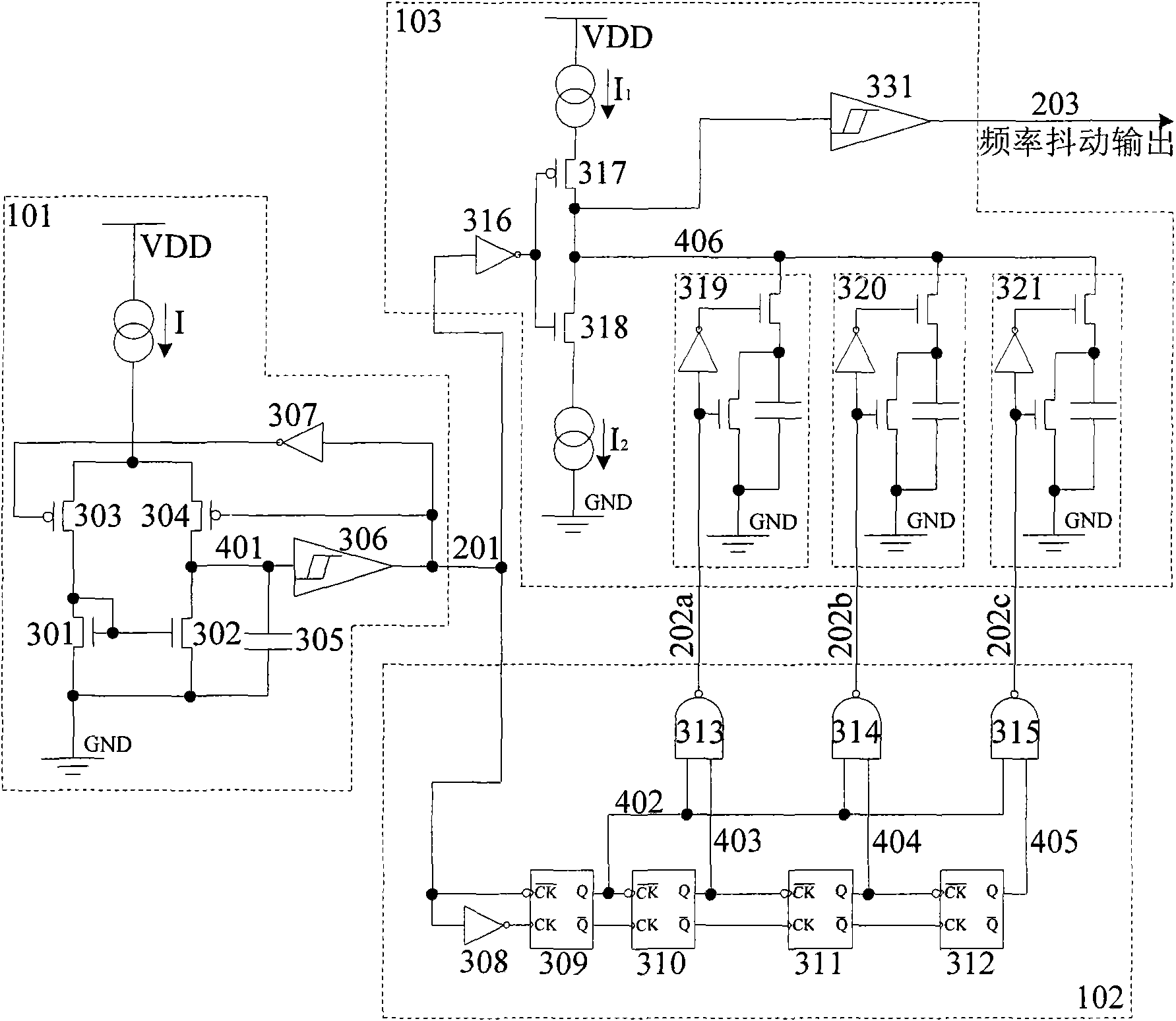

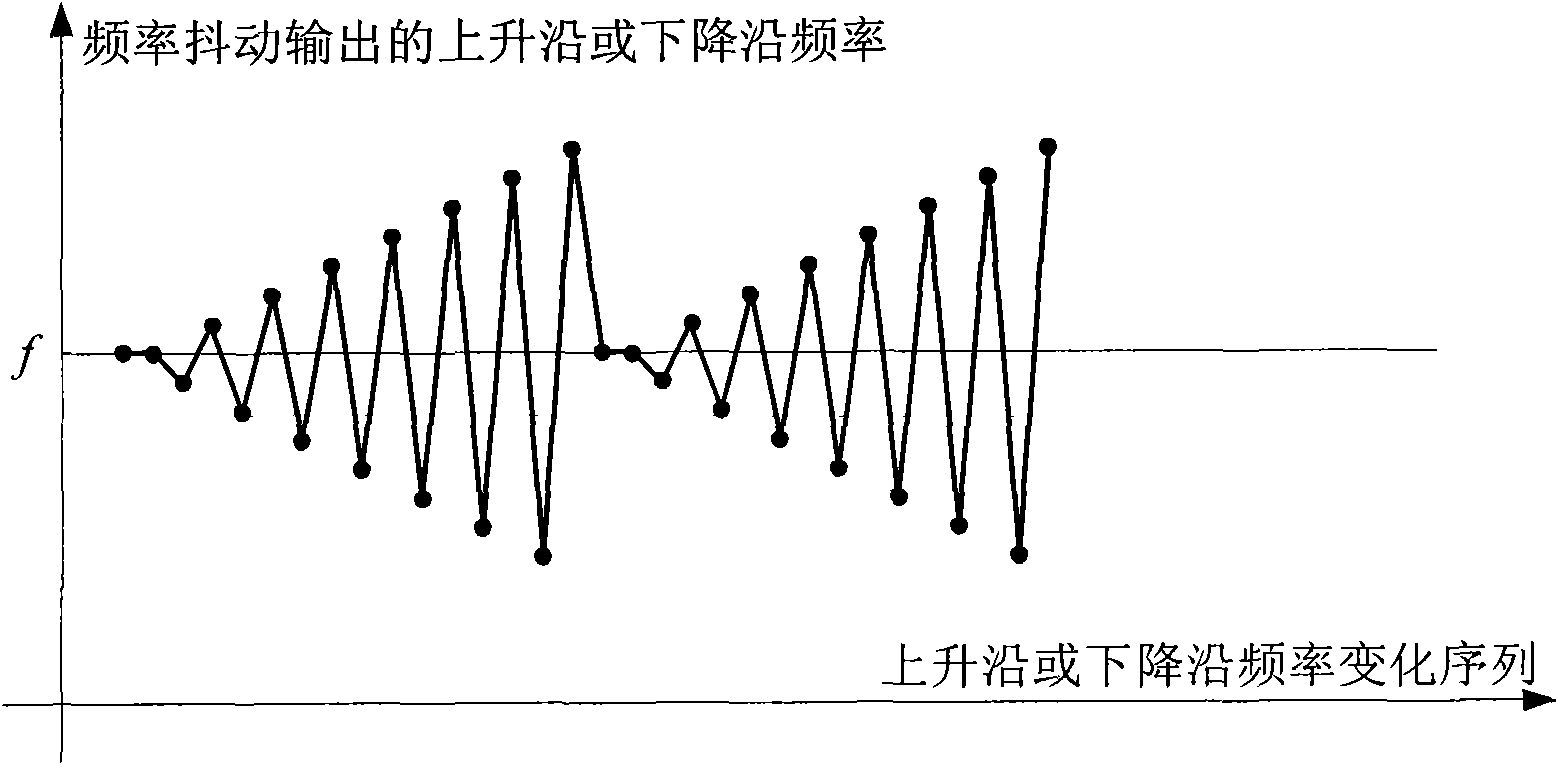

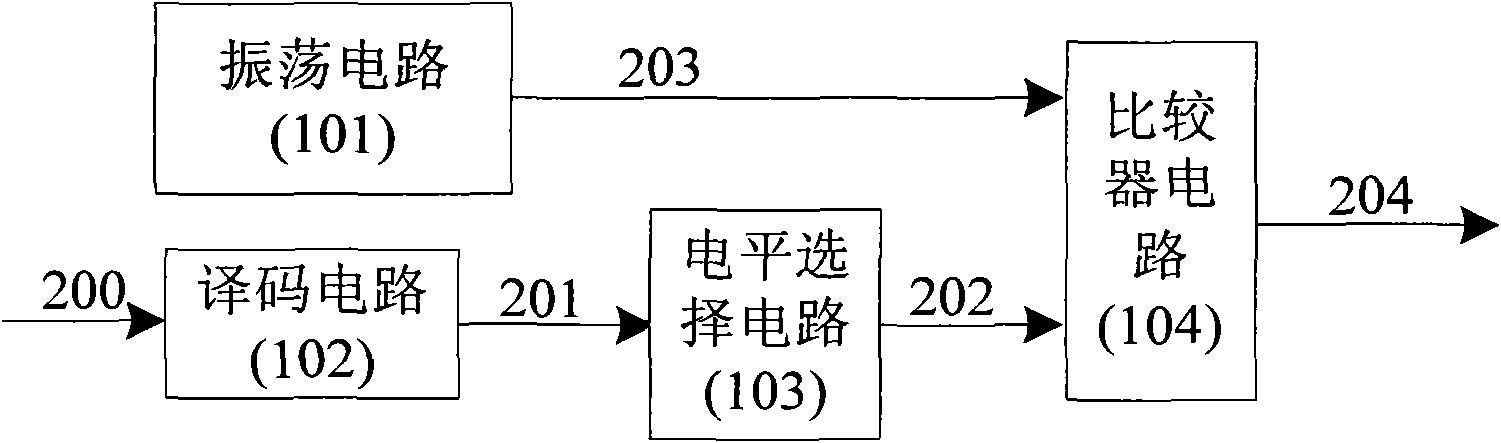

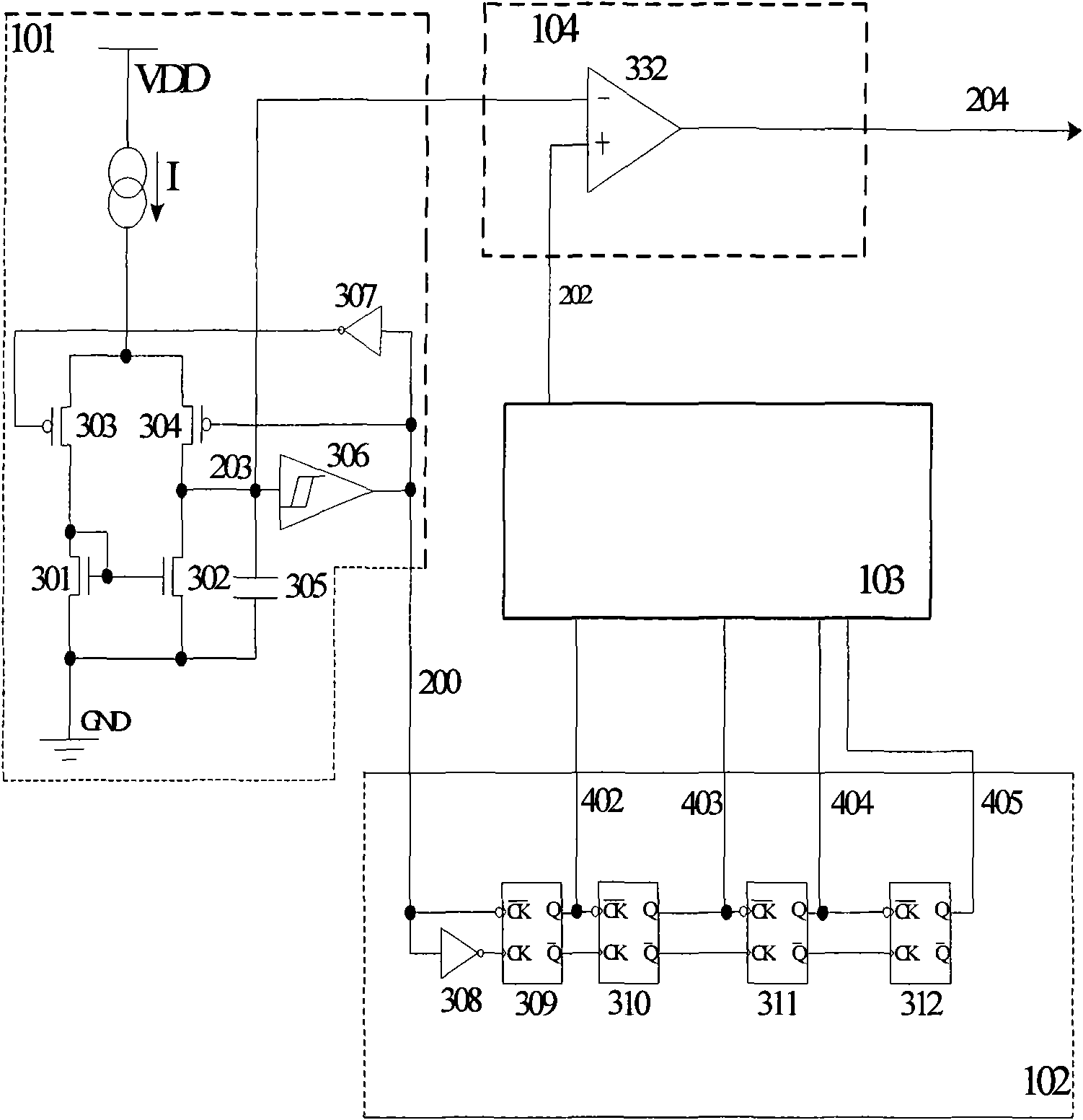

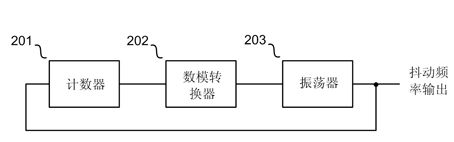

Frequency jitter circuit and frequency jitter generating method

ActiveCN101888176AAverage noise reductionDensity flatteningPulse generation by differential amplifiersPower conversion systemsComparators circuitsSwitching frequency

The invention provides a frequency jitter circuit, comprising an oscillating circuit, a decoding circuit, a level selecting circuit and a comparator circuit, wherein the oscillating circuit is used for generating a sawtooth signal; an oscillation frequency signal is input into the decoding circuit and controls the decoding circuit to generate a plurality of pulse signals; the pulse signals control the level selecting circuit to generate an output level signal which varies along with variation of a pulse output signal; the comparator circuit is used for comparing the sawtooth signal of the oscillation frequency and the output level signal and generating a frequency jitter signal; and the duty ratio of the frequency jitter signal and the edge of turn-on / turn-off vary along with variation of the output level signal. The invention also provides a method for generating frequency jitter. The frequency jitter circuit provided by the invention has the advantages of simple lines and easy realization. Meanwhile, frequency jitter ensures the switching frequency to be in a wide frequency range, ensures the EMI energy measured by EMI equipment to be diffused beyond the bandwidth, reduces the average EMI noises and flattens the energy spectrum density of the EMI noises.

Owner:HANGZHOU SILAN MICROELECTRONICS

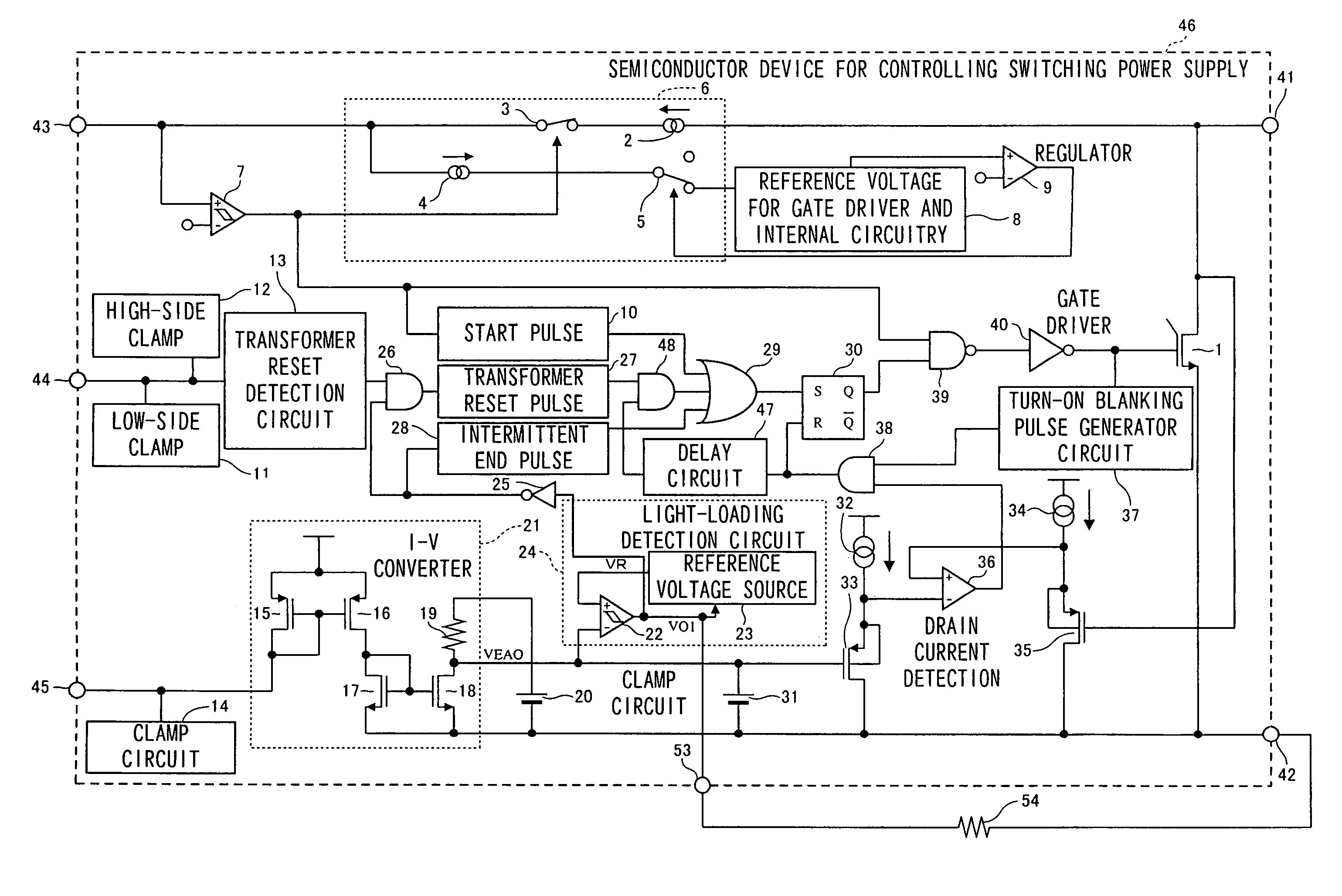

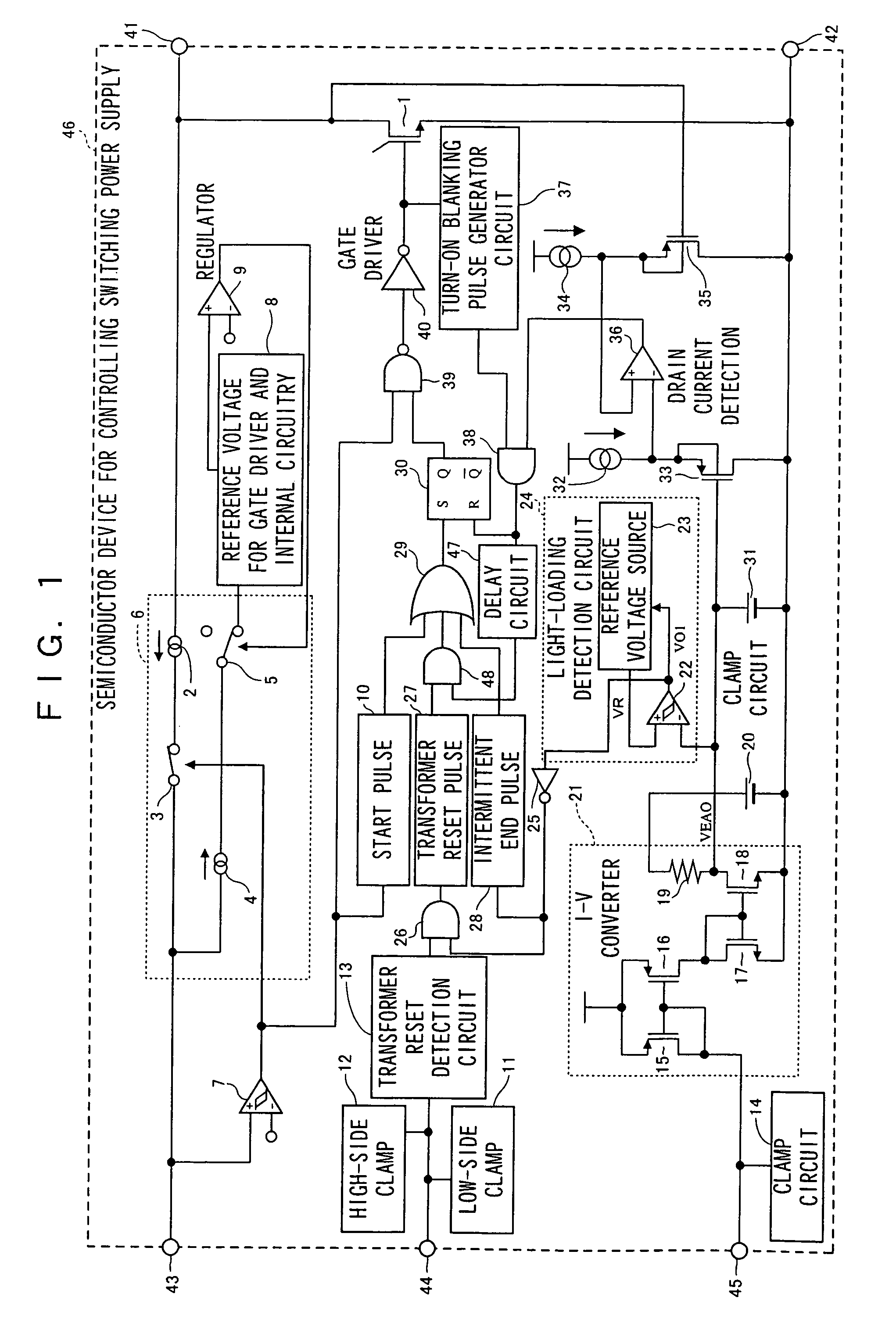

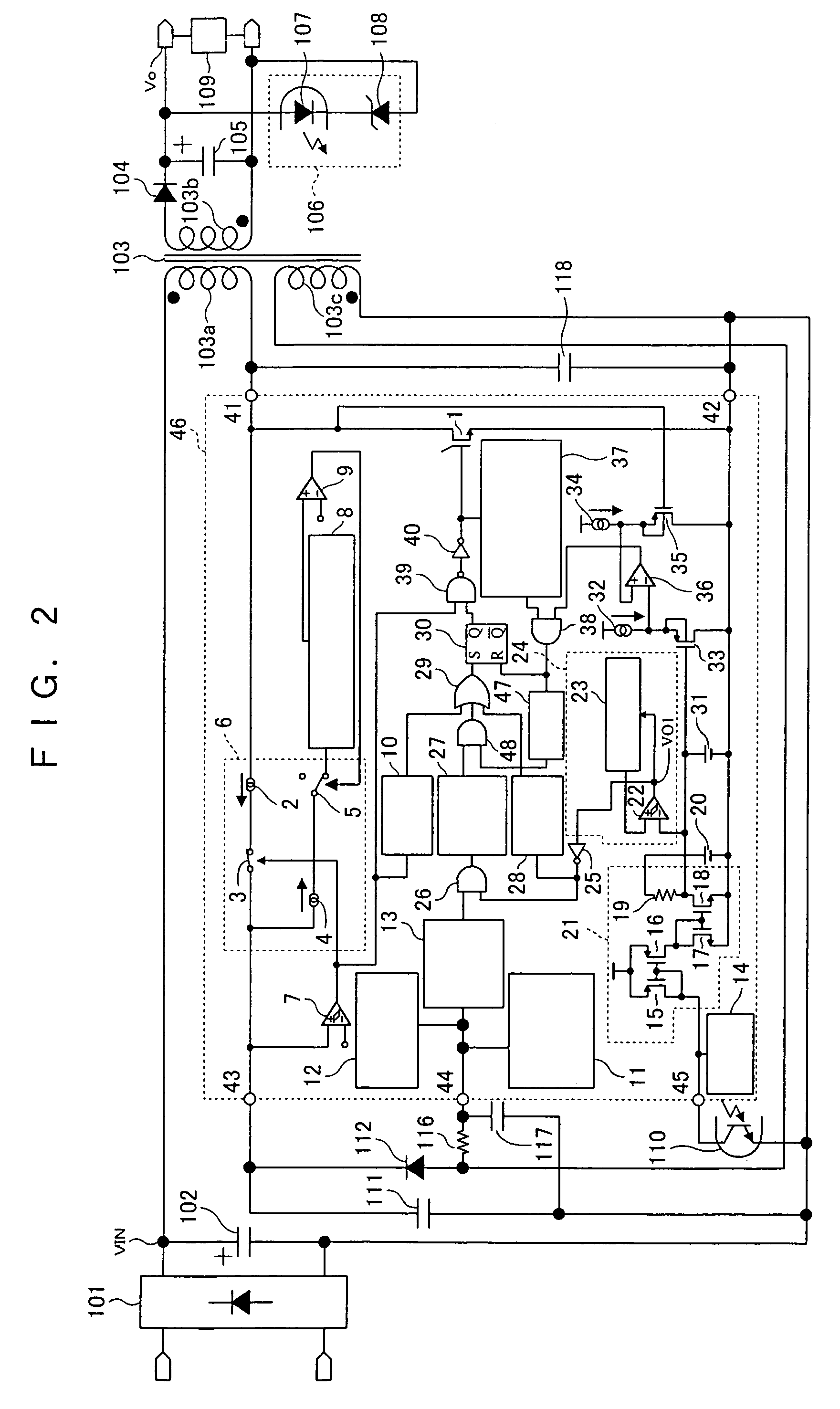

Semiconductor device for controlling switching power supply

InactiveUS7208985B2Reduce switching lossesImprove power efficiencyWater/sewage treatmentApparatus with intermediate ac conversionPower semiconductor deviceTransformer

In a semiconductor device for controlling switching power supply of this invention, having a switching element and switching operation control circuit, after receiving a current detection signal when switching is turned off, a fixed delay time is applied to the current detection signal by a delay circuit so that switching turn-on control by a transformer reset pulse signal obtained based on a signal from the tertiary windings of the transformer is not accepted within a blanking time corresponding to the delay time. Thus, the switching by the switching element is halted.

Owner:COLLABO INNOVATIONS INC

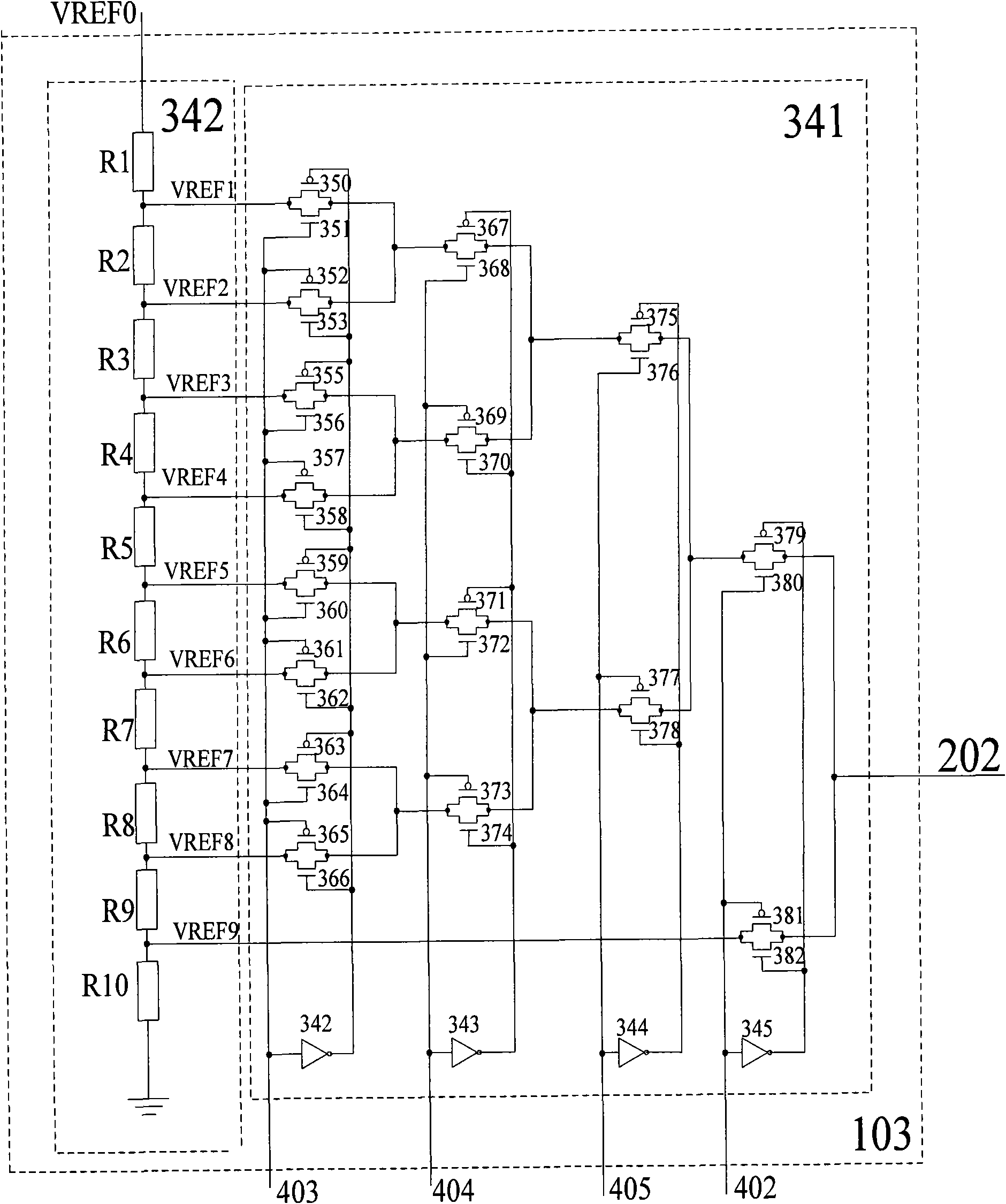

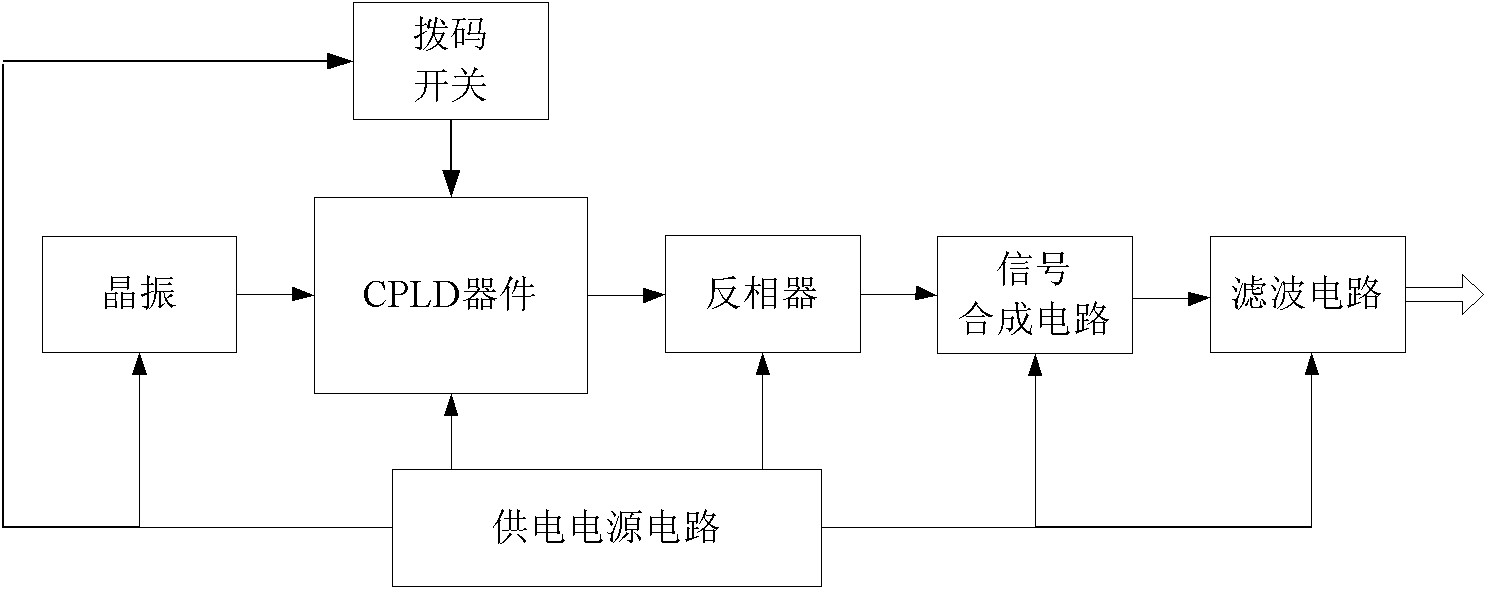

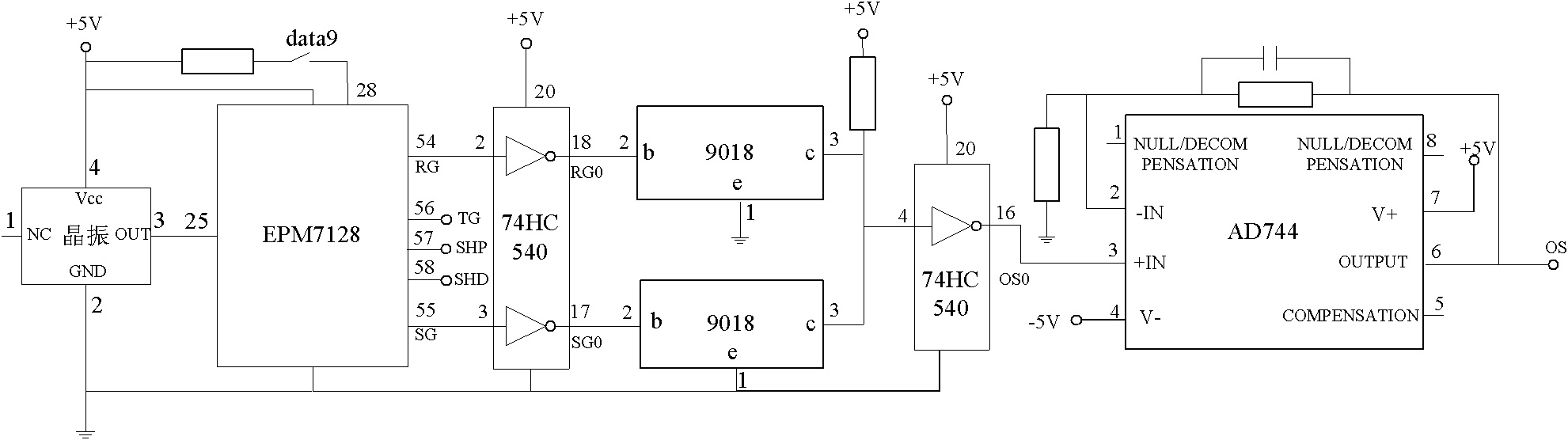

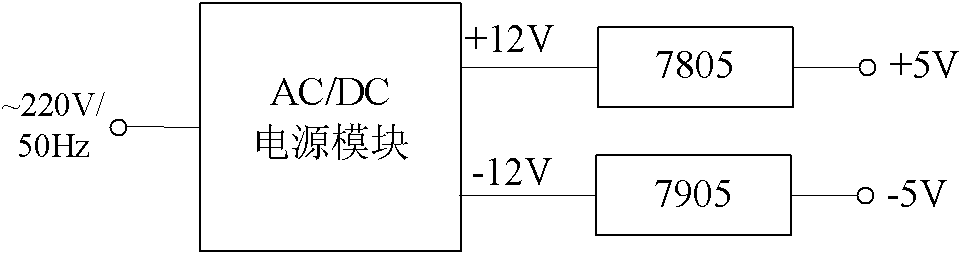

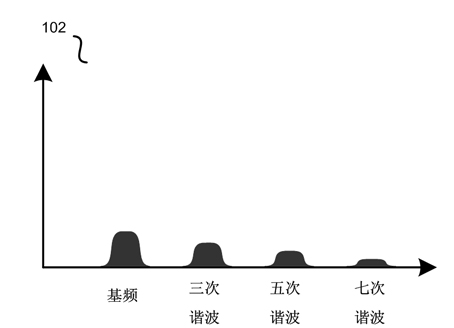

Analogue signal generator for TDI (Transport Driver Interface) CCD (Charge Coupled Device)

InactiveCN102545841AEasy to operateEasy to useElectrical measurement instrument detailsPulse generation by differential amplifiersSignal processing circuitsTransport Driver Interface

The invention relates to an analogue signal generator for a TDI (Transport Driver Interface) CCD (Charge Coupled Device), which is used for generating analogue signals of output signals of the TDI CCD and overcoming the defect that the TDI CCD is not suitable for repeatedly testing in a process of debugging and developing a signal processing circuit of the TDI CCD. The analogue signal generator specially comprises a timing sequence generation circuit, a signal combination circuit, a filtering circuit and a power supply circuit. The timing sequence generation circuit generates a logic signal pulse, the analogue signals of the output signals of the TDI CCD are preliminarily obtained through the signal combination circuit, and then the analogue signals of the output signals of the TDI CCD are finally obtained after passing through the filtering circuit. According to the analogue signal generator for the TDI CCD provided by the invention, the analogue signals of the output signals of the TDI CCD under different integration time are simulated by adjusting the period of the analogue signals, so as to replace the output signals of the TDI CCD to be used for the development of the signal processing circuit of the TDI CCD.

Owner:BEIJING UNIV OF TECH

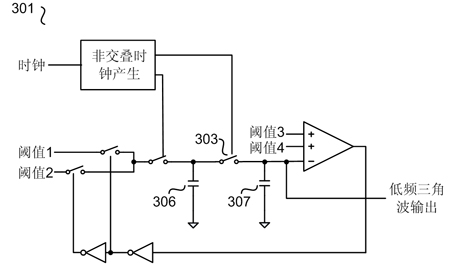

Frequency jittering circuit

ActiveCN102025265AImprove stabilityHigh frequency jitter accuracyPulse generation by differential amplifiersPower conversion systemsSystem stabilityTriangular wave

The invention provides a frequency jittering circuit, which comprises a feedback voltage processing circuit, a differential triangular wave generating circuit, a differential converting single-end circuit and a voltage-controlled oscillator which are in circuit connection, wherein the input end of the feedback voltage processing circuit is connected with feedback voltage, and the output end of the feedback voltage processing circuit is connected with the differential triangular wave generating circuit, the differential converting single-end circuit and the voltage-controlled oscillator; the output end of the differential triangular wave generating circuit is connected with the differential converting single-end circuit the output end of which is connected with the voltage-controlled oscillator; and the output end of the voltage-controlled oscillator is connected with the differential triangular wave generating circuit, and is used for outputting a clock signal. The frequency jitteringcircuit has the advantages of good system stability and high frequency jittering accuracy.

Owner:灿芯创智微电子技术(北京)有限公司

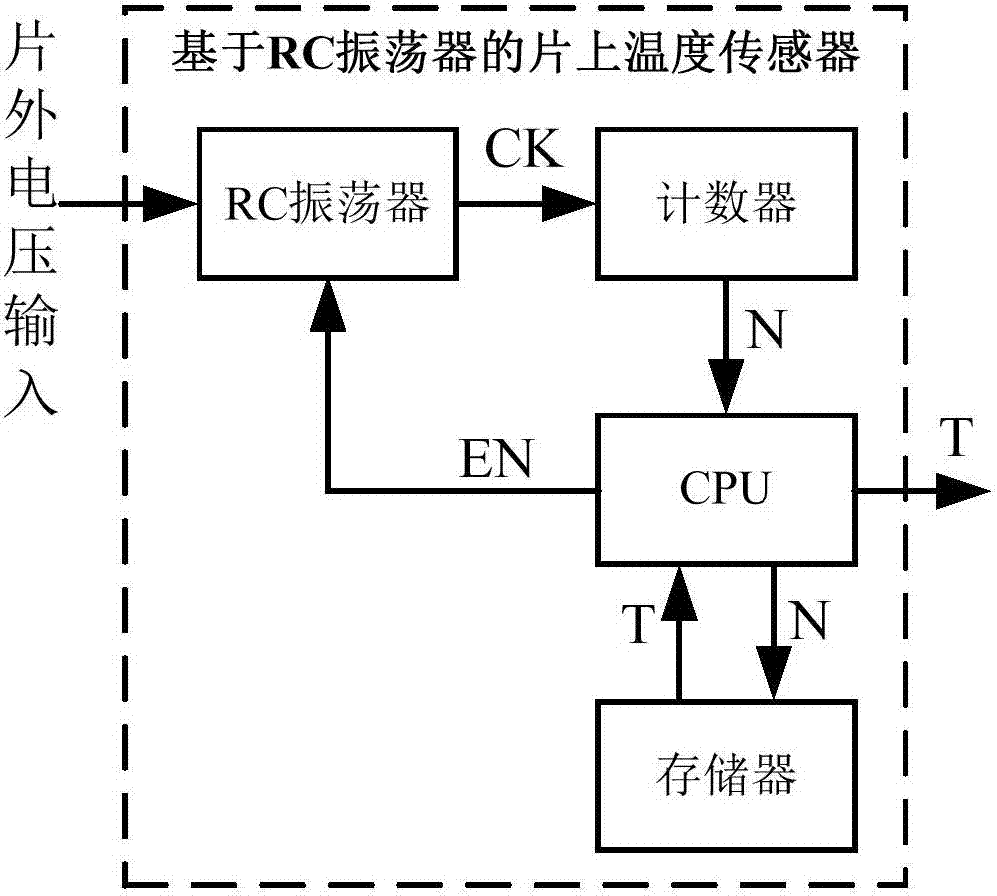

On-chip temperature sensor based on RC oscillator, and temperature detection method of on-chip temperature sensor

ActiveCN107014507AStable bisap bias voltageLower latencyThermometers using electric/magnetic elementsUsing electrical meansClock rateWorking temperature

The invention discloses an on-chip temperature sensor based on an RC oscillator, and a temperature detection method of the on-chip temperature sensor. The temperature sensor comprises the RC oscillator, a counter, a CPU, and a storage unit, wherein the RC oscillator is used for generating a clock signal, and the output frequency of the clock signal changes with temperature. The counter is used for counting the number of pulses of the clock signal in a certain gate time period, and calculates the frequency of the clock signal outputted by the RC oscillator. The storage unit is used for storing a frequency-temperature look-up table in advance. The CPU is used for obtaining the temperature value corresponding to a current clock signal frequency according to the obtained clock signal frequency through a table look-up method. Compared with the prior art, the temperature sensor enables the temperature change to be reflected by the change of the frequency of the clock signal outputted by the oscillator through the working temperature characteristics of the RC oscillator, and the CPU can obtain the current temperature of the core of a chip through reading the frequency count value. Therefore, there is no need to set an additional chip in the temperature sensor, thereby greatly reducing the chip area occupied by the temperature sensor. Meanwhile, the temperature sensor can meet the various types of clock control application demands.

Owner:SAGE MICROELECTRONICS CORP

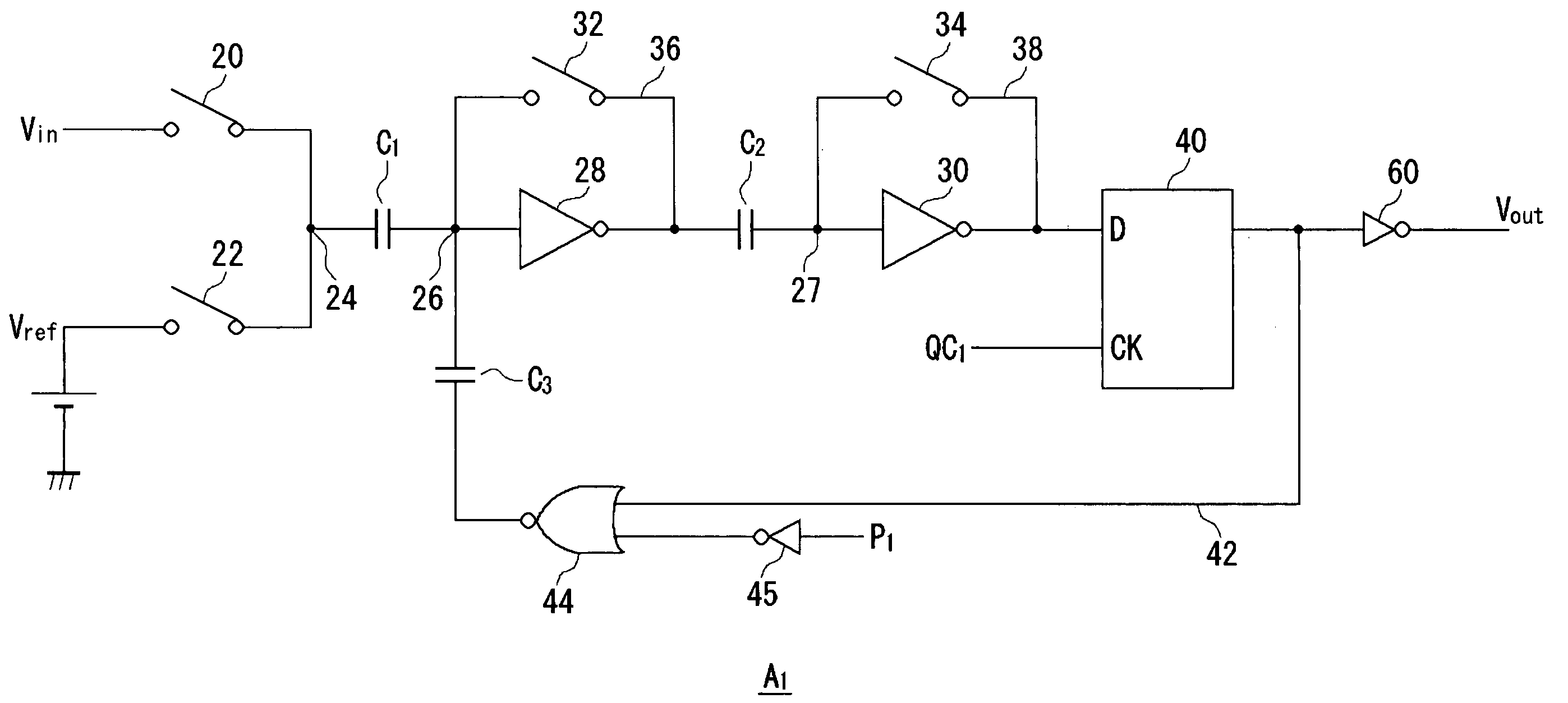

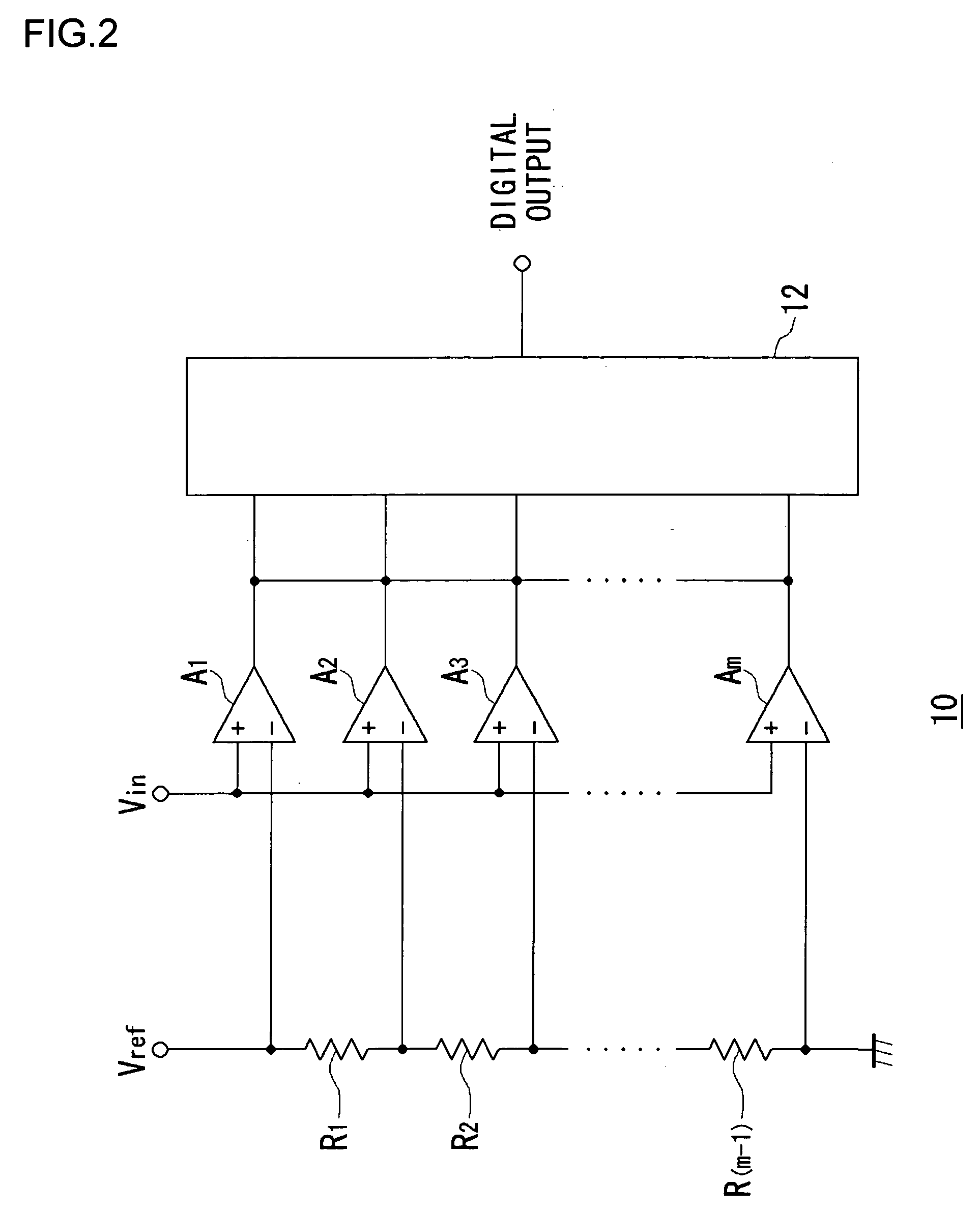

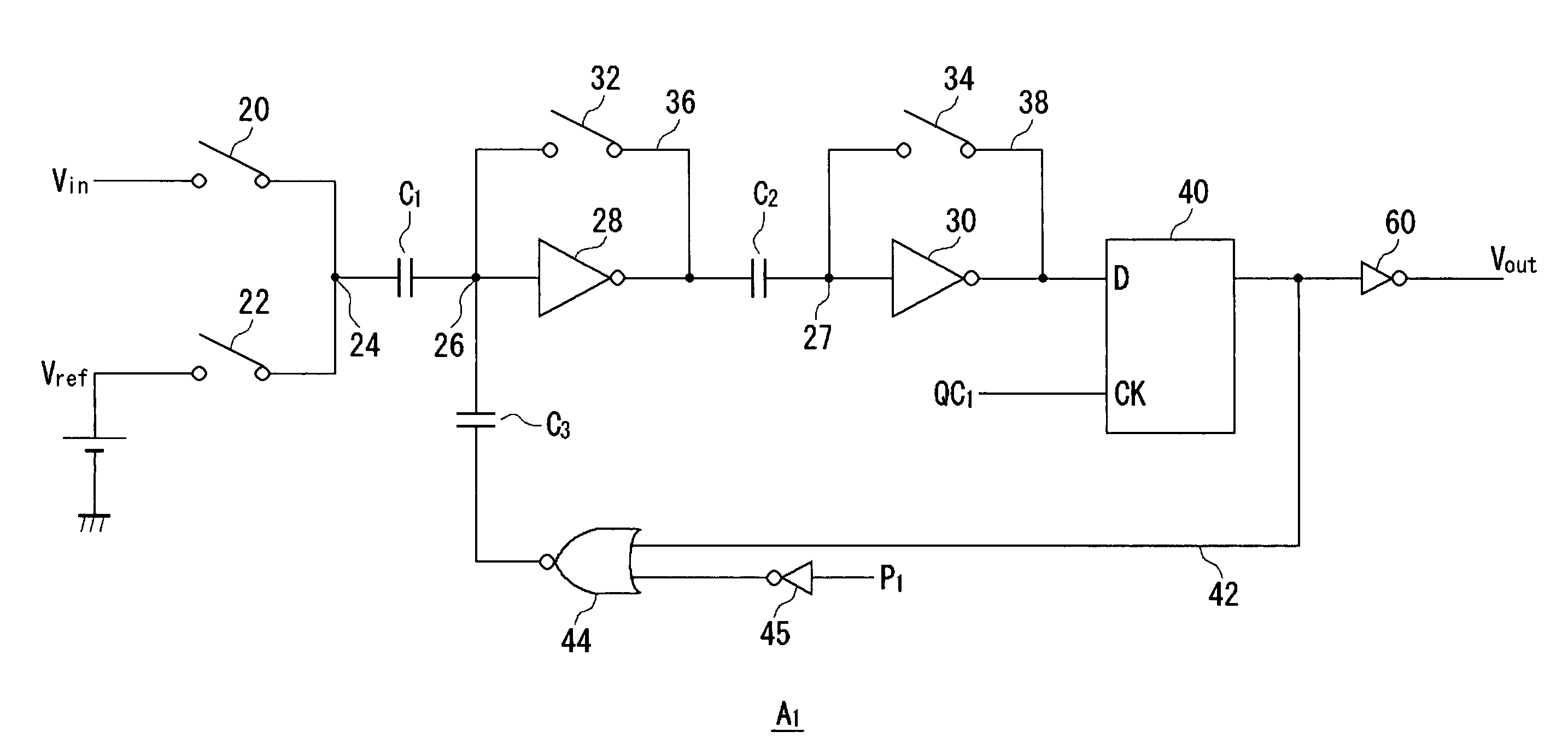

Comparator and AD conversion circuit having hysteresis circuit

InactiveUS20050184762A1Simple configurationImprove stabilityTelevision system detailsMultiple input and output pulse circuitsHysteresisVoltage reference

A comparator is provided, which compares an input voltage and a reference voltage by using a plurality of inverting circuits connected in series. The comparator includes a first inverting circuit, a second inverting circuit, a feedback path, and a capacitor arranged on the feedback path. The first inverting circuit inverts a difference between the input voltage and the reference voltage for output. The second inverting circuit further inverts the output of the first inverting circuit for output. The feedback path feeds back the output of the second inverting circuit to the input side of the first inverting circuit. The capacitor causes hysteresis such that an increasing threshold and a decreasing threshold of the second inverting circuit corresponding to an increase and a decrease of the input voltage have a difference therebetween.

Owner:ROHM CO LTD

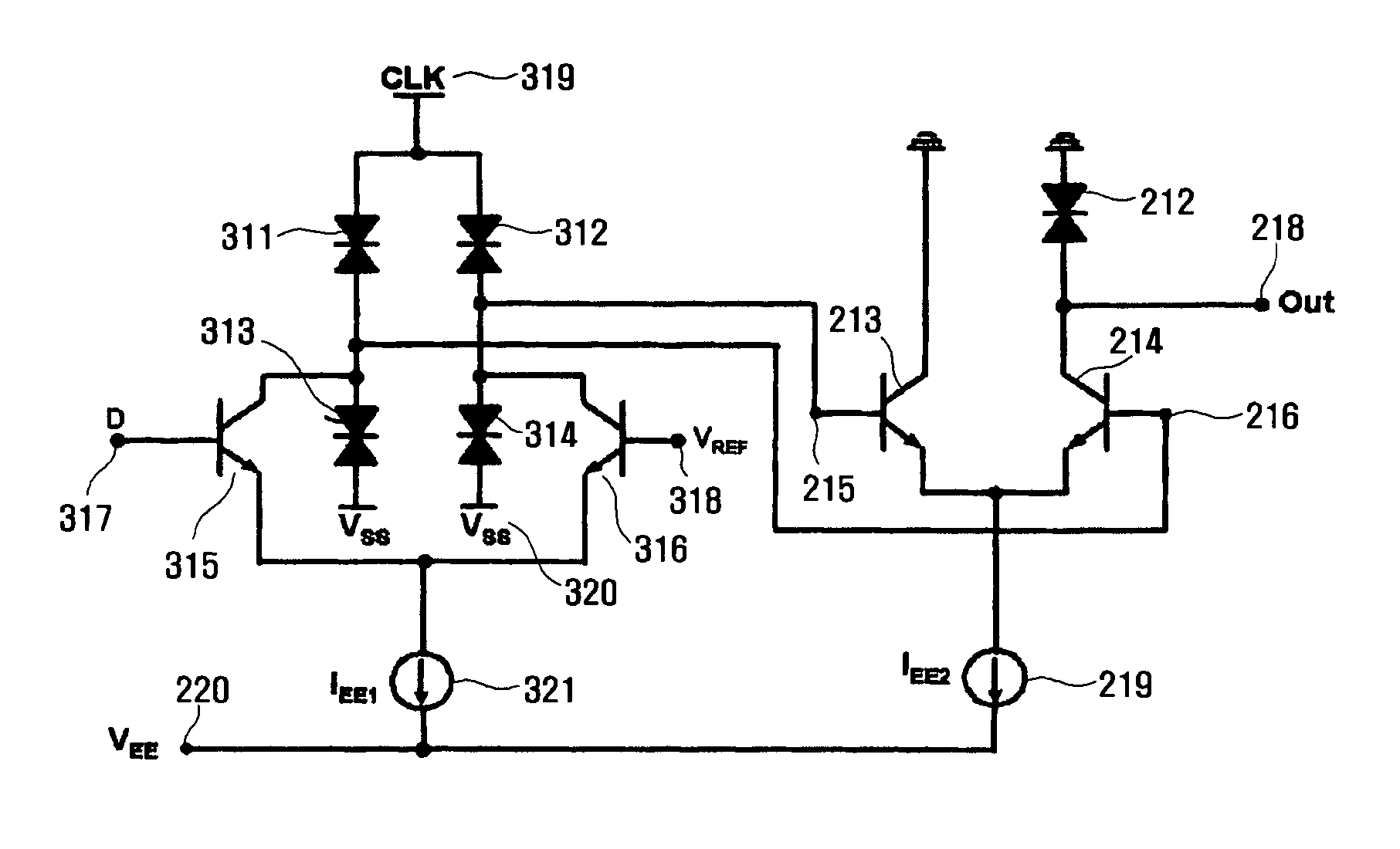

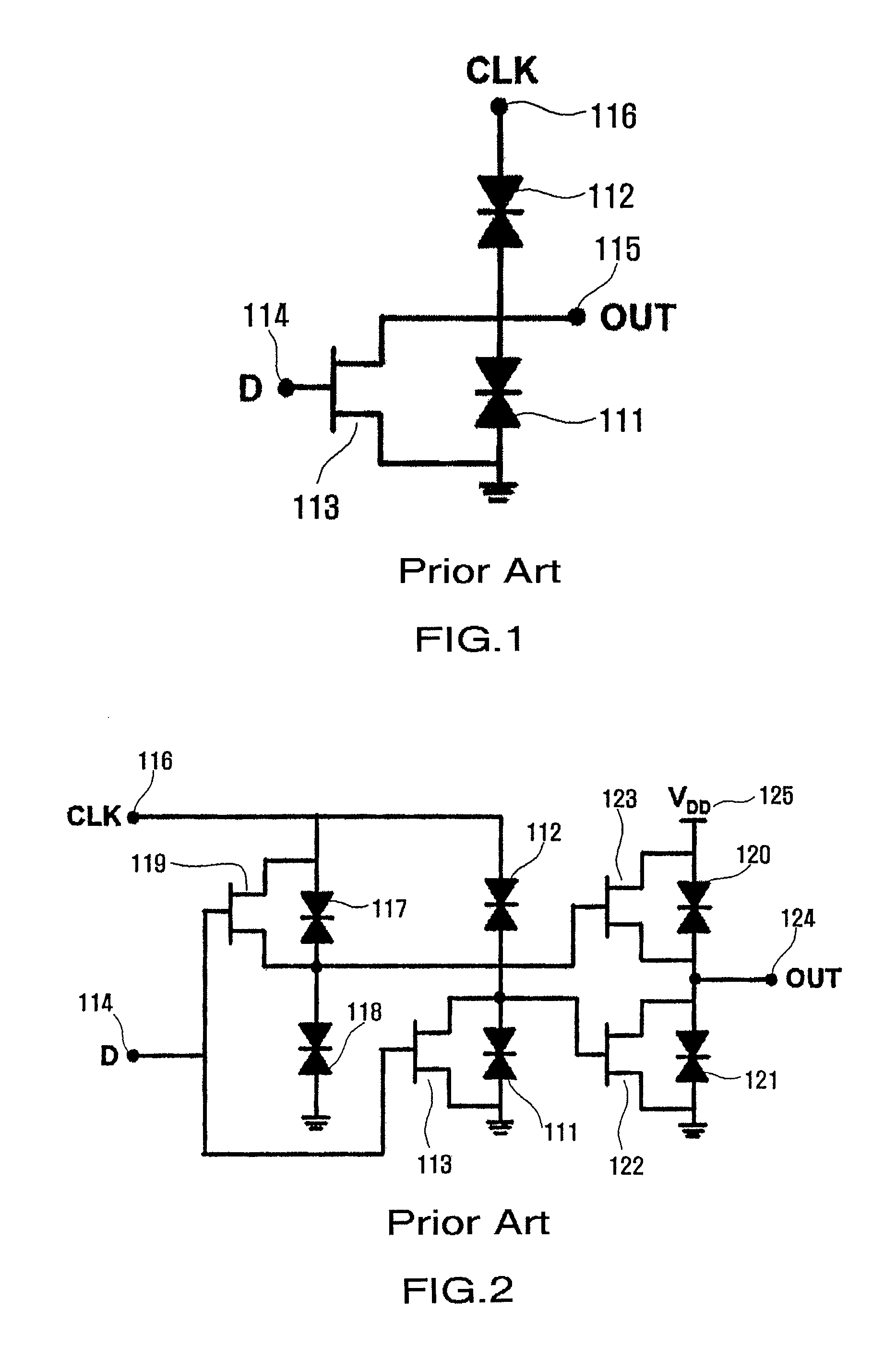

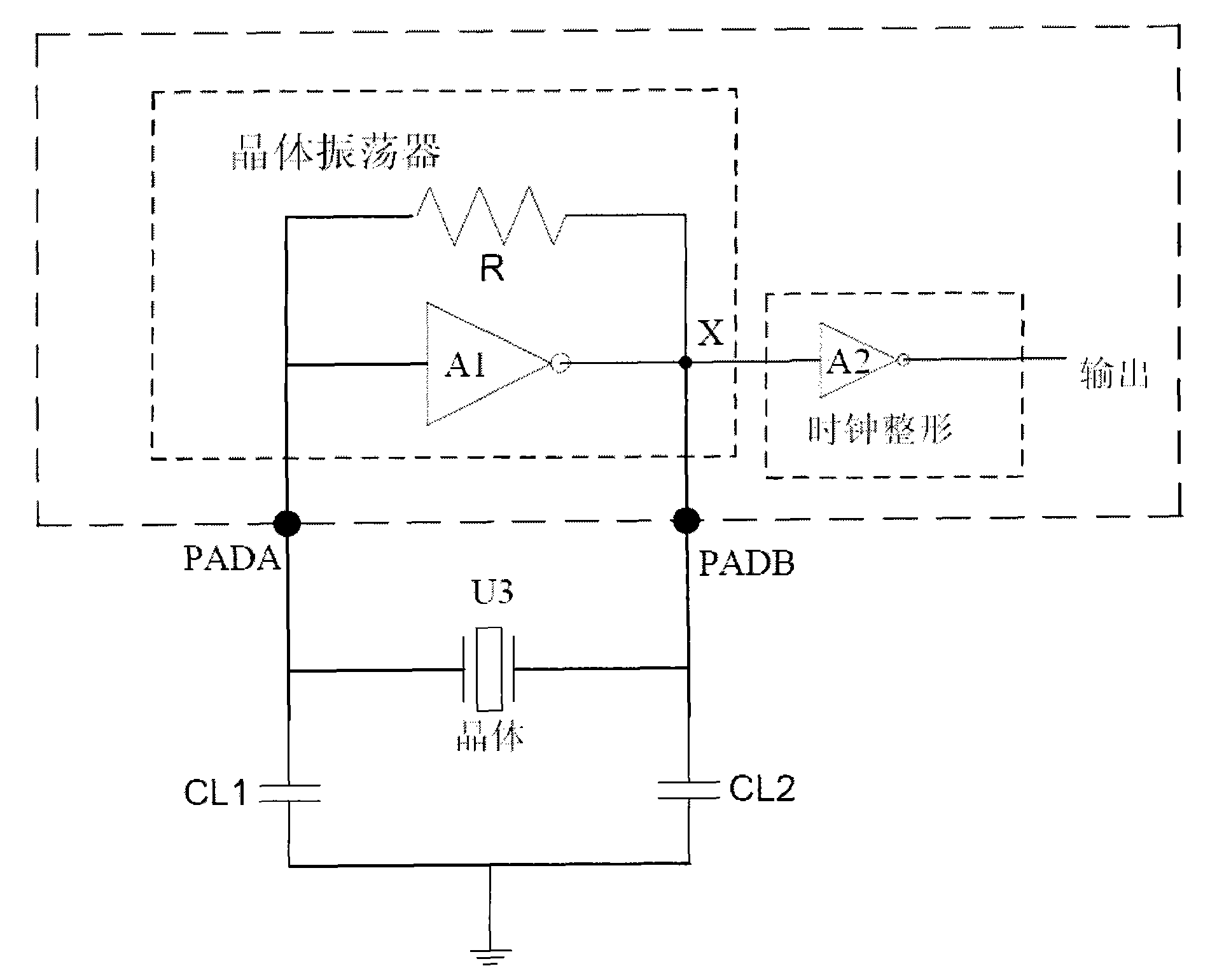

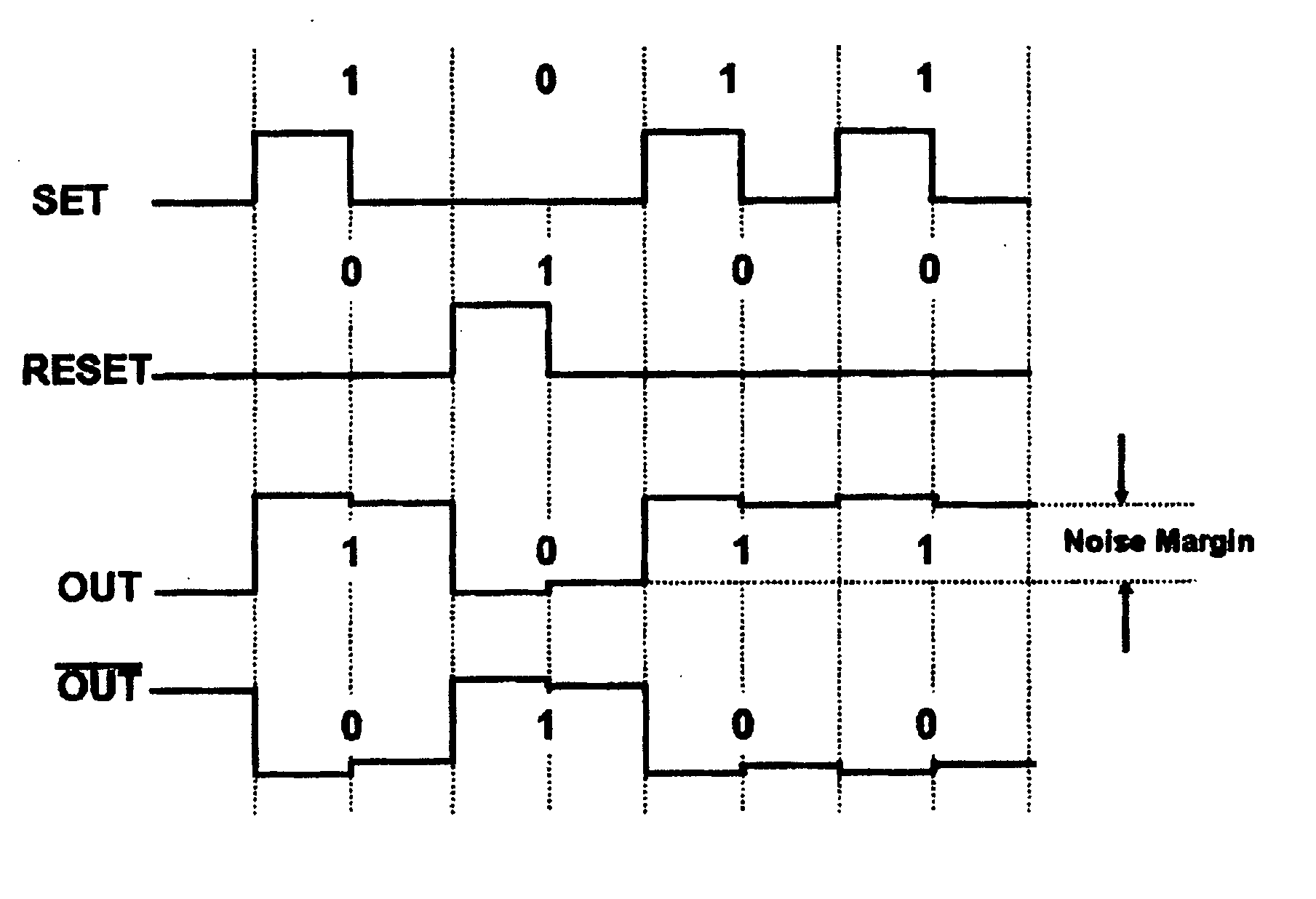

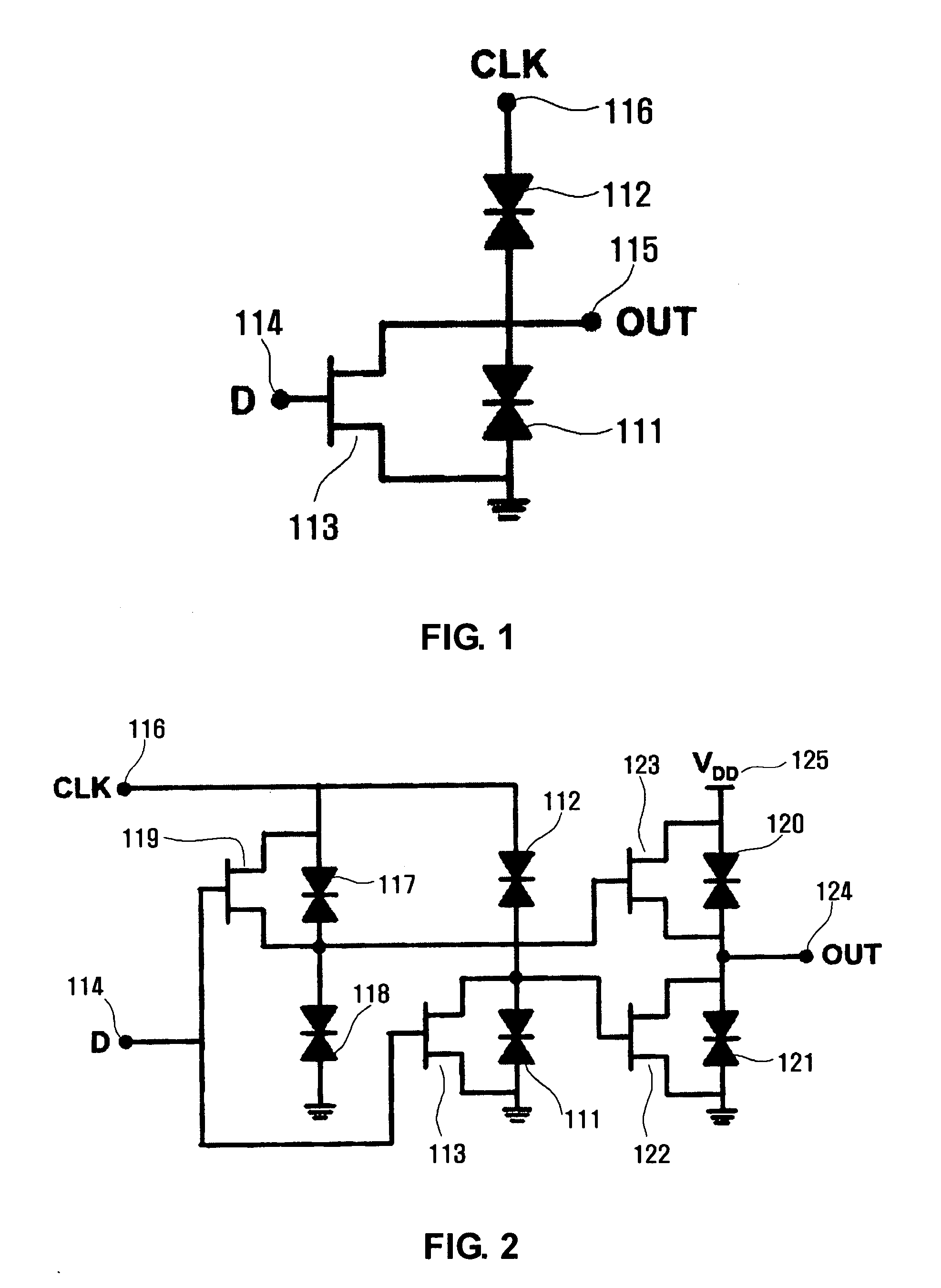

SET/RESET latch circuit, Schmitt trigger circuit, and MOBILE based D-type flip flop circuit and frequency divider circuit thereof

InactiveUS7573310B2Easy to useHigh speedLogic circuits characterised by logic functionDiodeSchmitt triggerEngineering

The present invention relates to a SET / RESET latch circuit a Schmitt trigger circuit, and a MOBILE based D-type flip flop circuit and frequency divider circuit using the SET / RESET latch circuit and Schmitt trigger circuit. The SET / RESET latch circuit is configured with CML-type transistors and negative differential resistance diodes. The SET / RESET latch circuit can be applied to very high speed digital circuits.

Owner:KOREA ADVANCED INST OF SCI & TECH

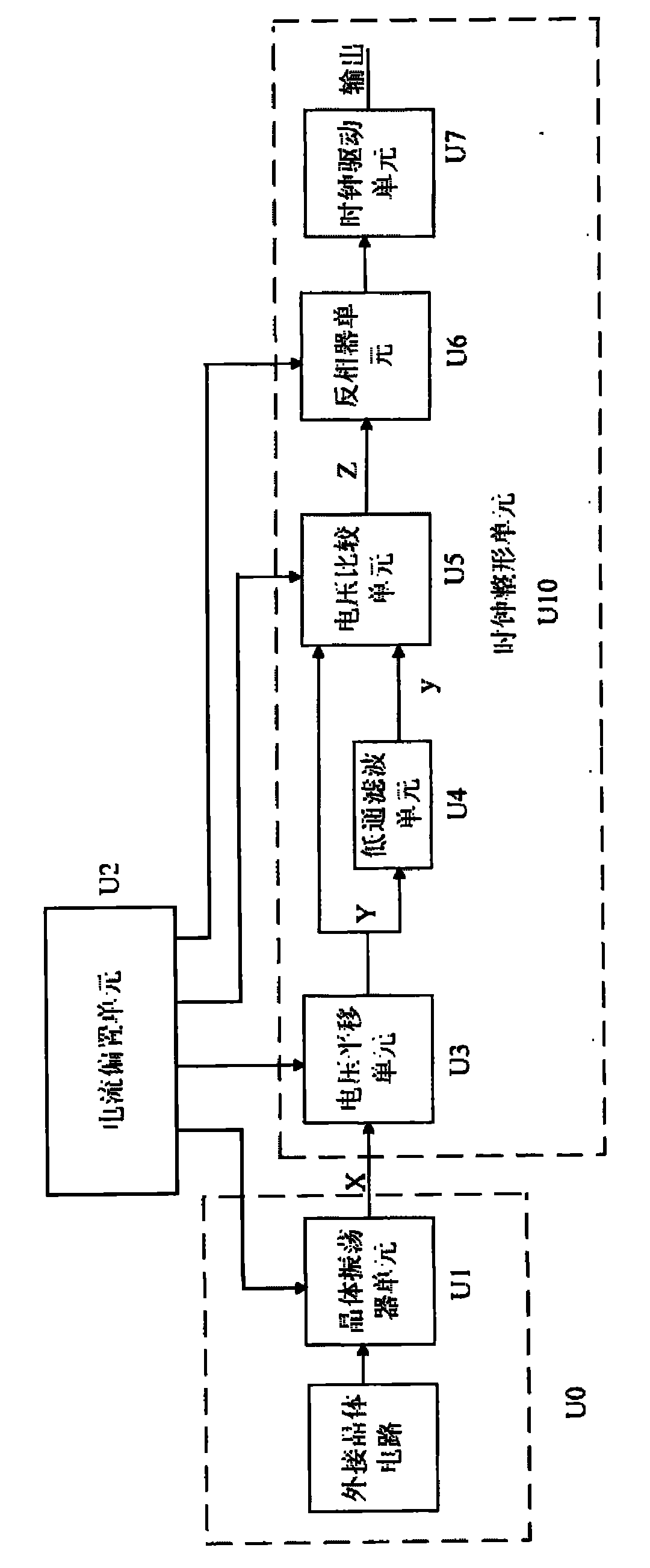

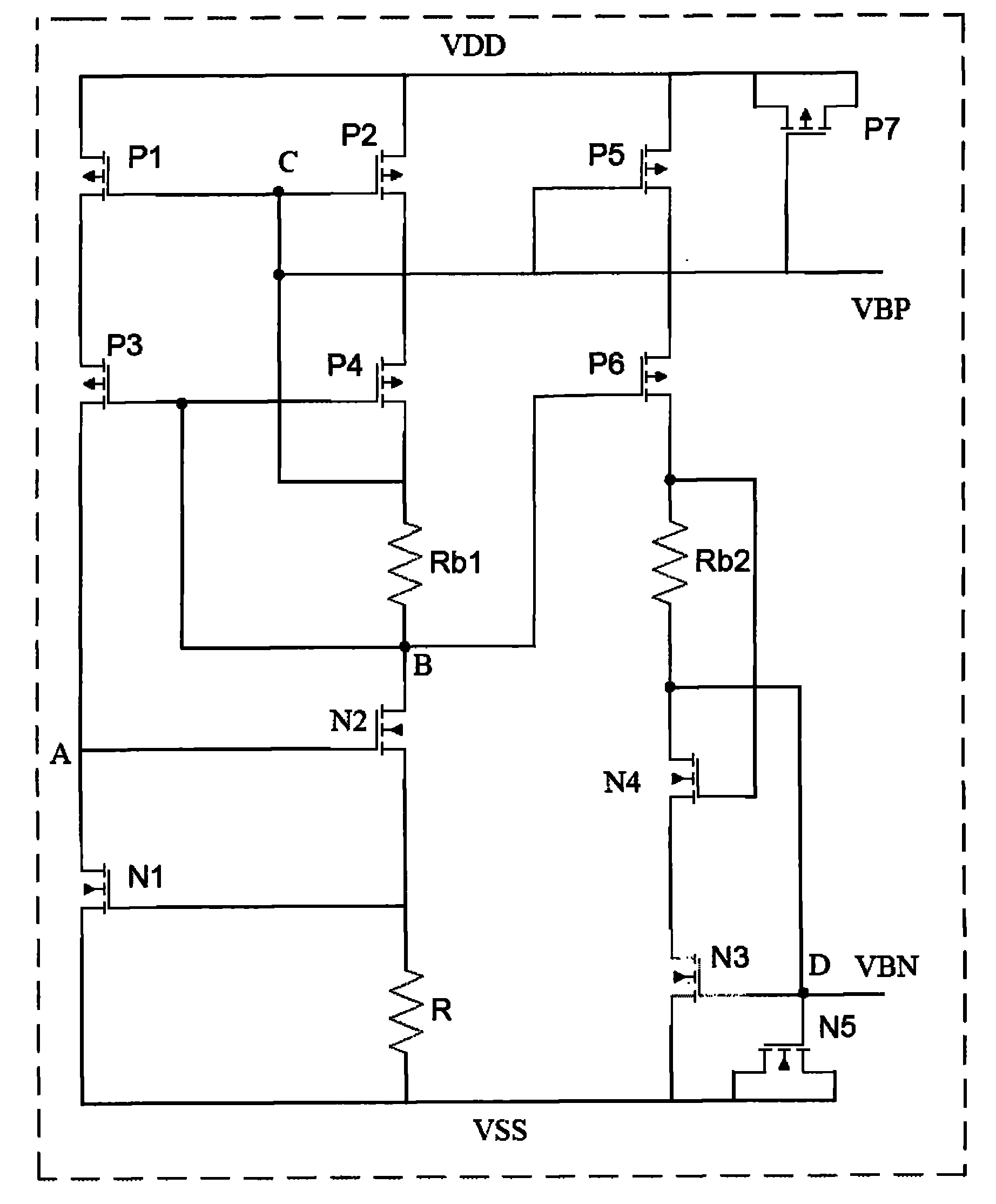

Clock signal generating circuit

InactiveCN102098027AReduce power consumptionPulse generation by differential amplifiersPower flowEngineering

The invention provides a clock signal generating circuit which comprises a crystal oscillation unit and a clock shaping unit, wherein the crystal oscillation unit generates an initial clock signal, and the clock shaping unit is used for shaping the initial clock signal and then outputting a standard clock signal. The clock signal generating circuit also comprises a current bias unit connected with the crystal oscillation unit and the clock shaping unit, wherein the crystal oscillation unit and the clock shaping unit mirror the bias current of the current bias unit, and the mirror current is used as a working current, so that the currents of the crystal oscillation unit and the clock shaping unit can be controlled and regulated by controlling the current of the current bias unit.

Owner:VIMICRO CORP

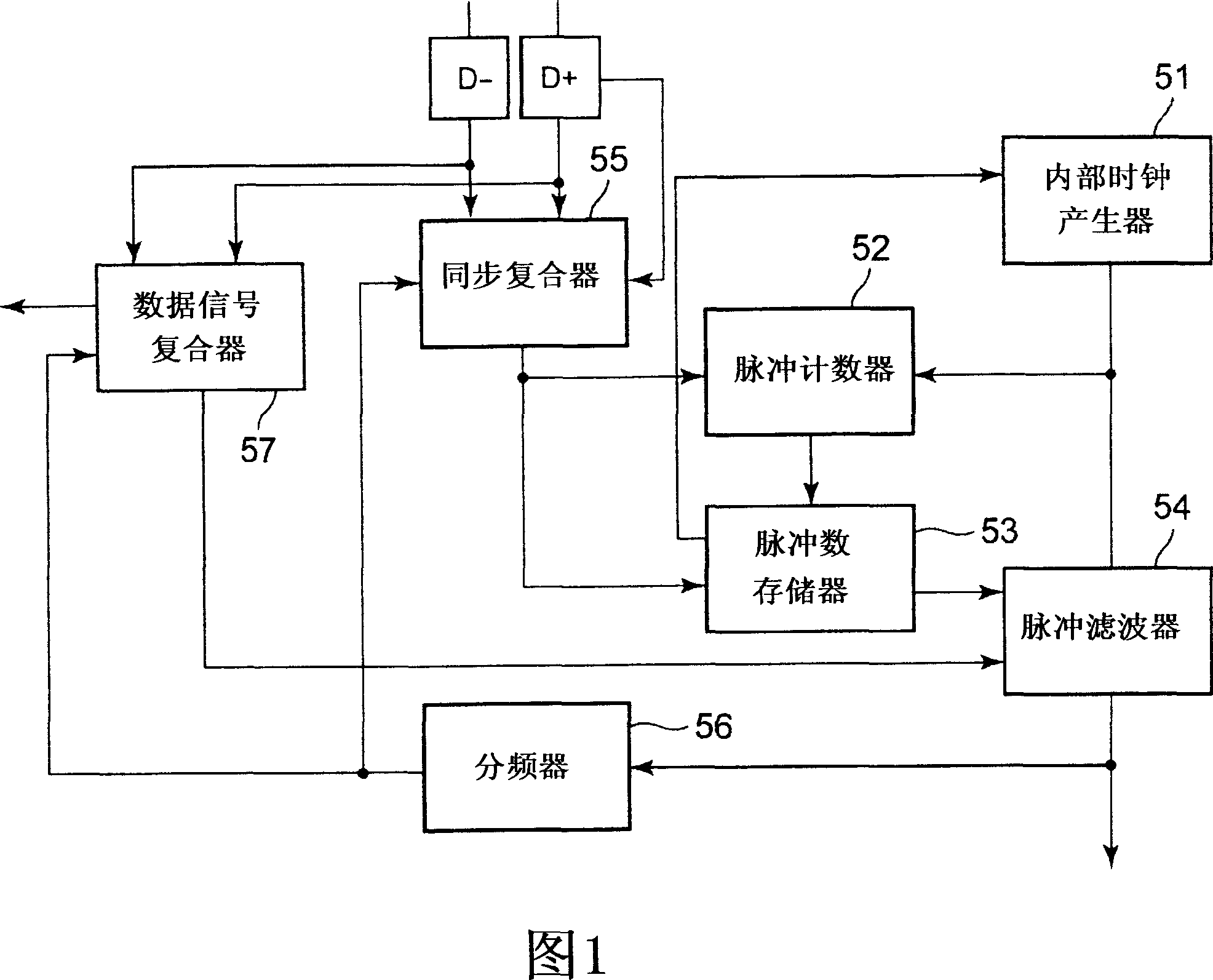

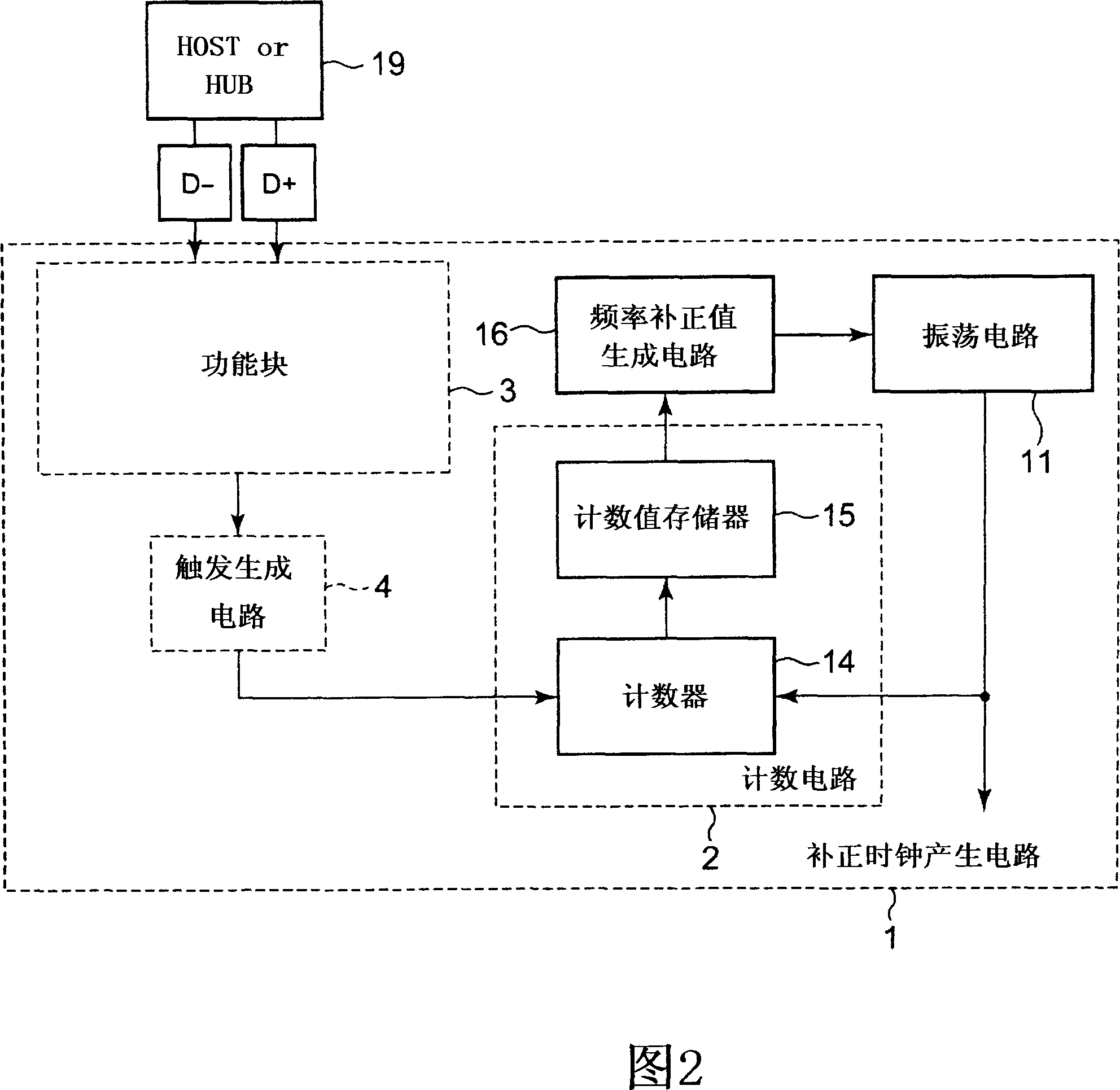

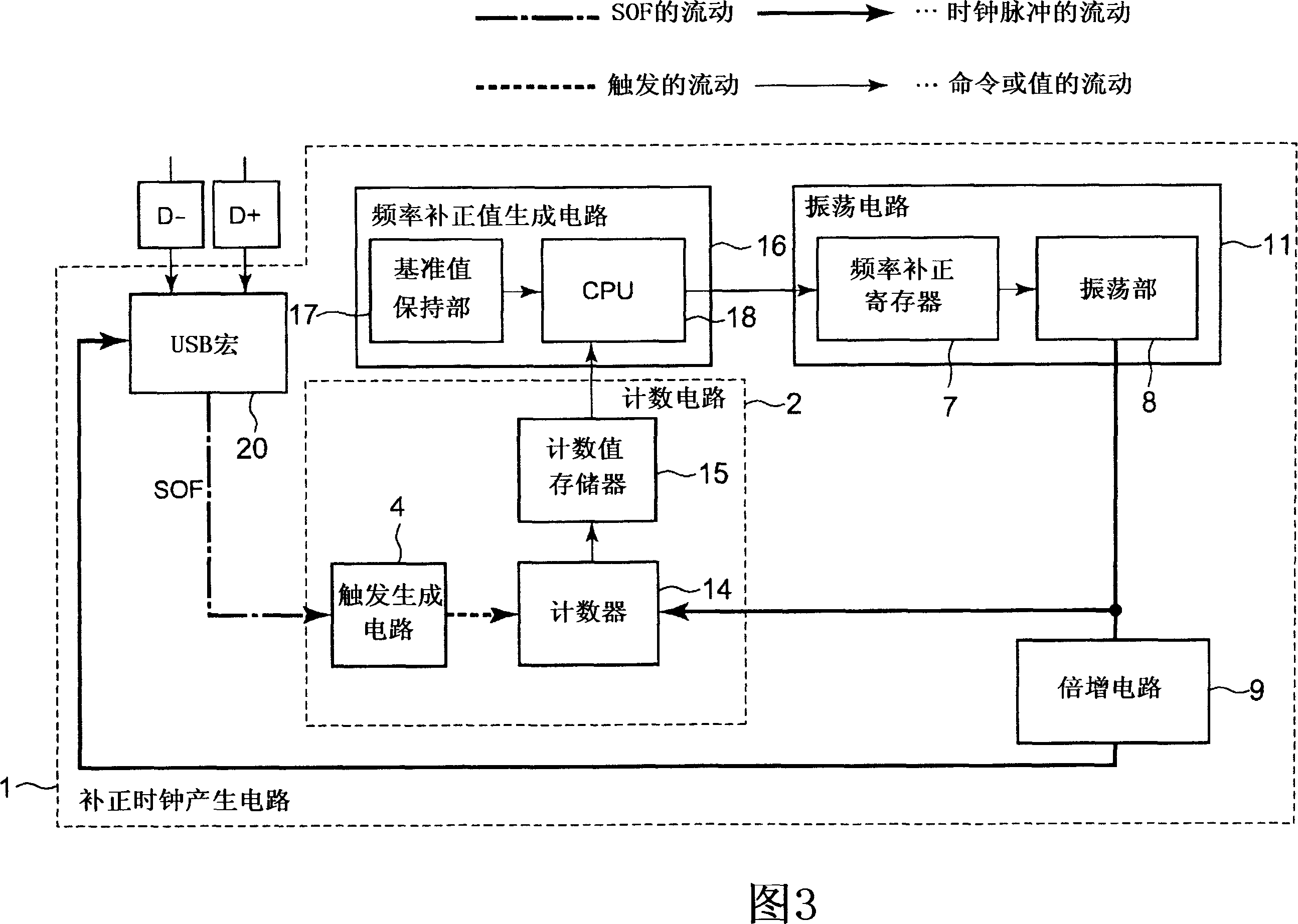

Compensated-clock generating circuit and usb device having same

InactiveCN1940808ALow costPulse automatic controlPulse generation by differential amplifiersFrequency compensationUSB

A compensated-clock generating circuit that complies with USB specifications includes an oscillating circuit that generates clock pulses; a counting circuit that counts the number of clock pulses from the oscillating circuit based upon a regular prescribed signal in accordance with a USB downstream signal; and a frequency compensation value generating circuit that compares the value counted by the counting circuit and a prescribed reference value and obtaining a compensation value. The oscillation frequency of the oscillating circuit is corrected to a prescribed value in response to receipt of the compensation value from the frequency compensation value generating circuit. Compensation is applied based upon a highly accurate signal that is based upon USB specifications, thereby making it possible to generate pulses of higher accuracy even if the accuracy of the oscillation frequency per se of the oscillator in the oscillation circuit is low.

Owner:NEC ELECTRONICS CORP

Current sensing multiple output current stimulators

A multiple output current stimulator circuit with fast turn on time is described. At least one pair of input side and output side transistors is arranged in a current mirror connected to a supply transistor by cascode coupling. The output side transistor supplies stimulation current to an electrode in contact with tissue. An operational amplifier connected to a reference voltage and to the output side transistor drives the supply transistor to maintain the voltage at the output side transistor equal to the reference voltage. The at least one pair of transistors includes multiple pairs of transistors whose output side transistors drive respective electrodes with stimulation currents. The stimulator determines the initiation and duration of stimulation current pulses supplied to each electrode. At circuit activation, large currents are generated which discharge capacitances in the output side transistors causing rapid output side transistor turn on.

Owner:ALFRED E MANN FOUND FOR SCI RES

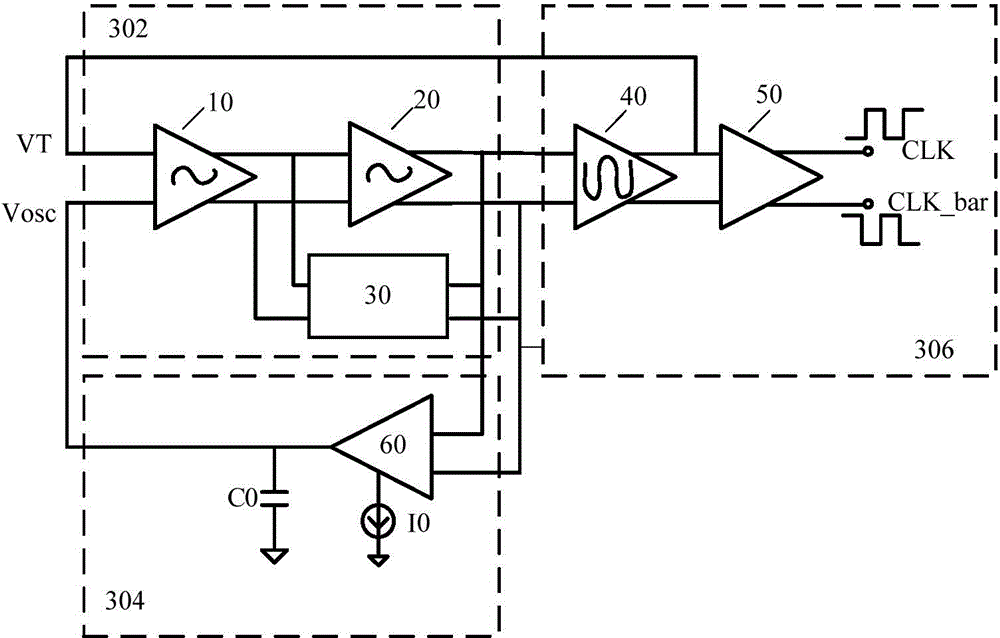

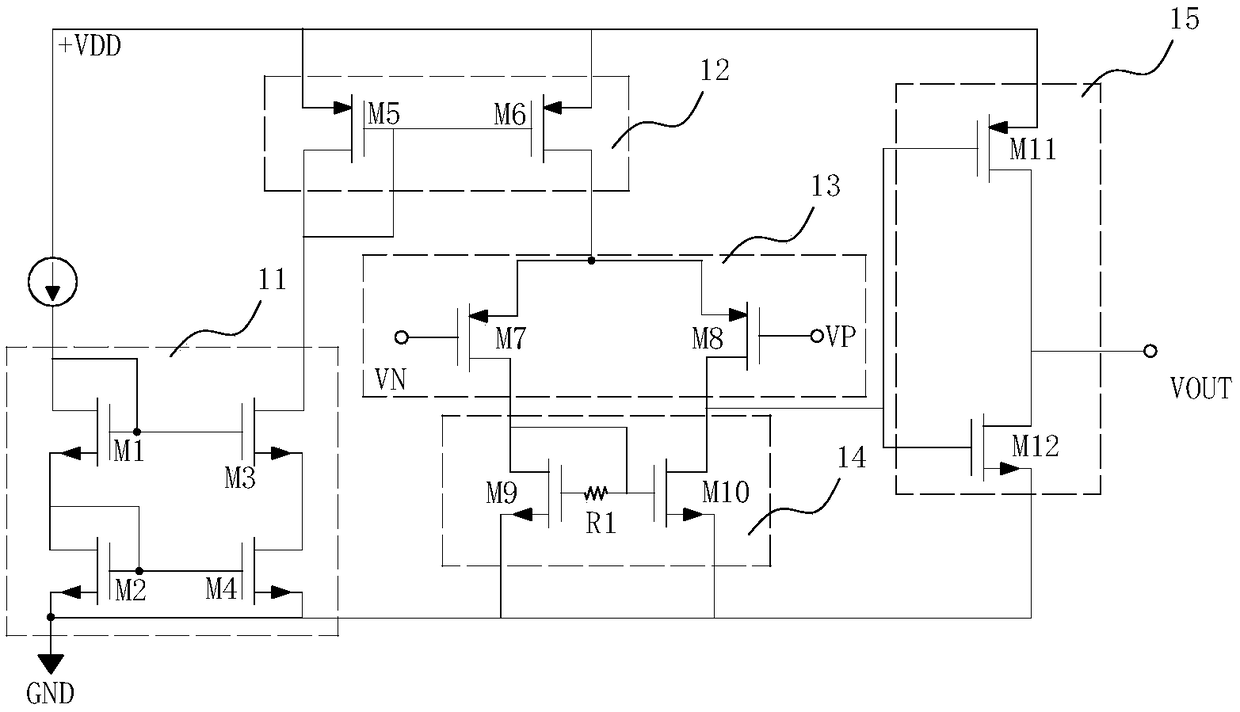

Clock signal producing circuit

ActiveCN104868880AWide operating voltage rangeSolve the problem of excessive delay errorPulse generation by differential amplifiersLevel shiftingDifferential signaling

The invention provides a clock signal producing circuit. The clock signal producing circuit comprises a small signal amplification unit, a delay unit and a level shifting unit. The small signal amplification unit comprises a first input end for inputting a threshold voltage, a second input end for inputting an oscillation voltage, a first output end for outputting a first differential signal, and a second output end for outputting a second differential signal. The delay unit comprises a third input end connected with the first output end, a fourth input end connected with the second output end, a third output end for outputting the oscillation voltage to the second input end, and a capacitor with one end connected with the third output end. The level shifting unit comprises a fifth input end connected with the first output end, a sixth input end connected with the second output end, a fourth output end for outputting the threshold voltage to the first input end, and a fifth output end for outputting a clock signal. Through adoption of the clock signal producing circuit, the problem of excessive delay error of the clock signal producing circuit in the prior art is solved.

Owner:SG MICRO

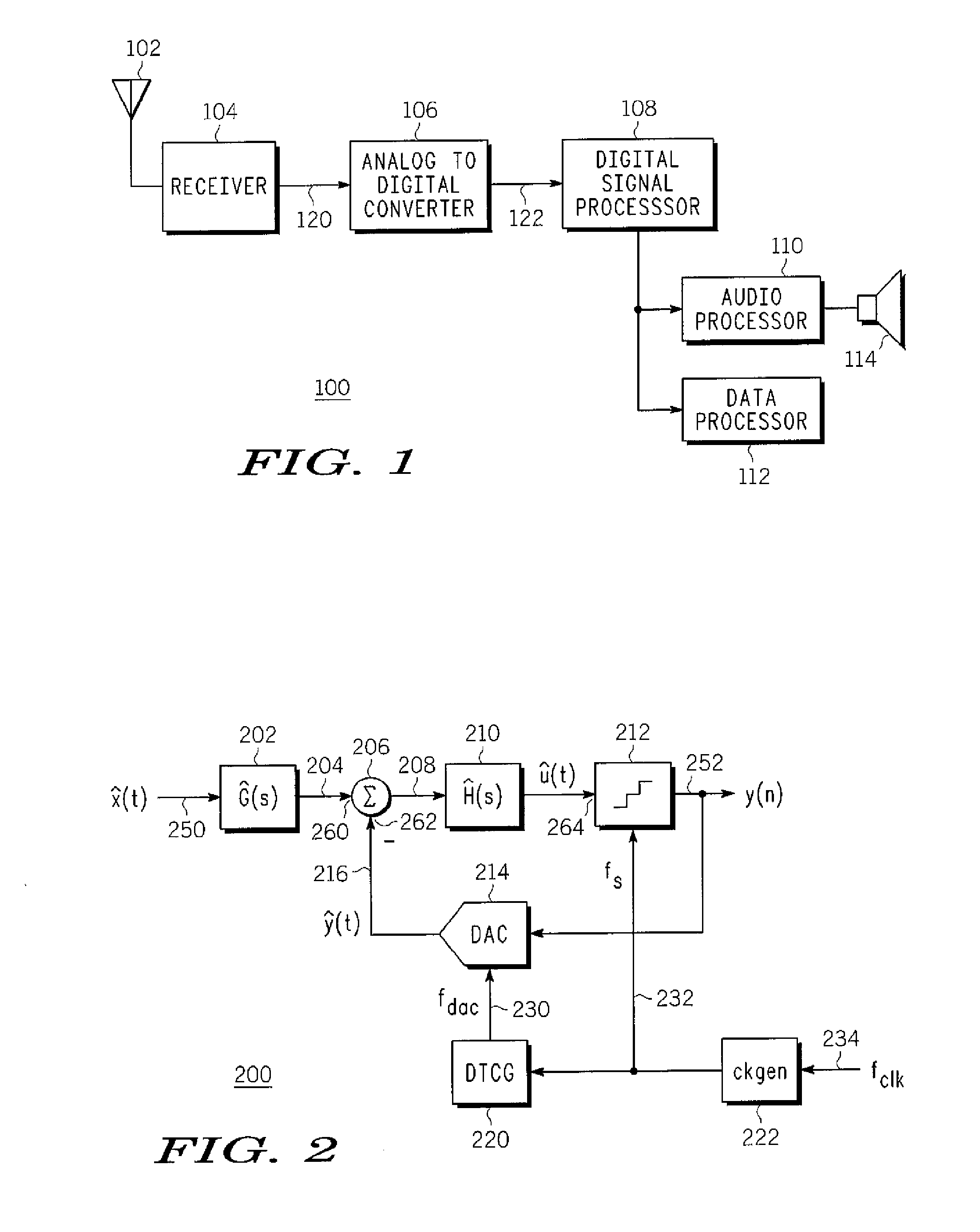

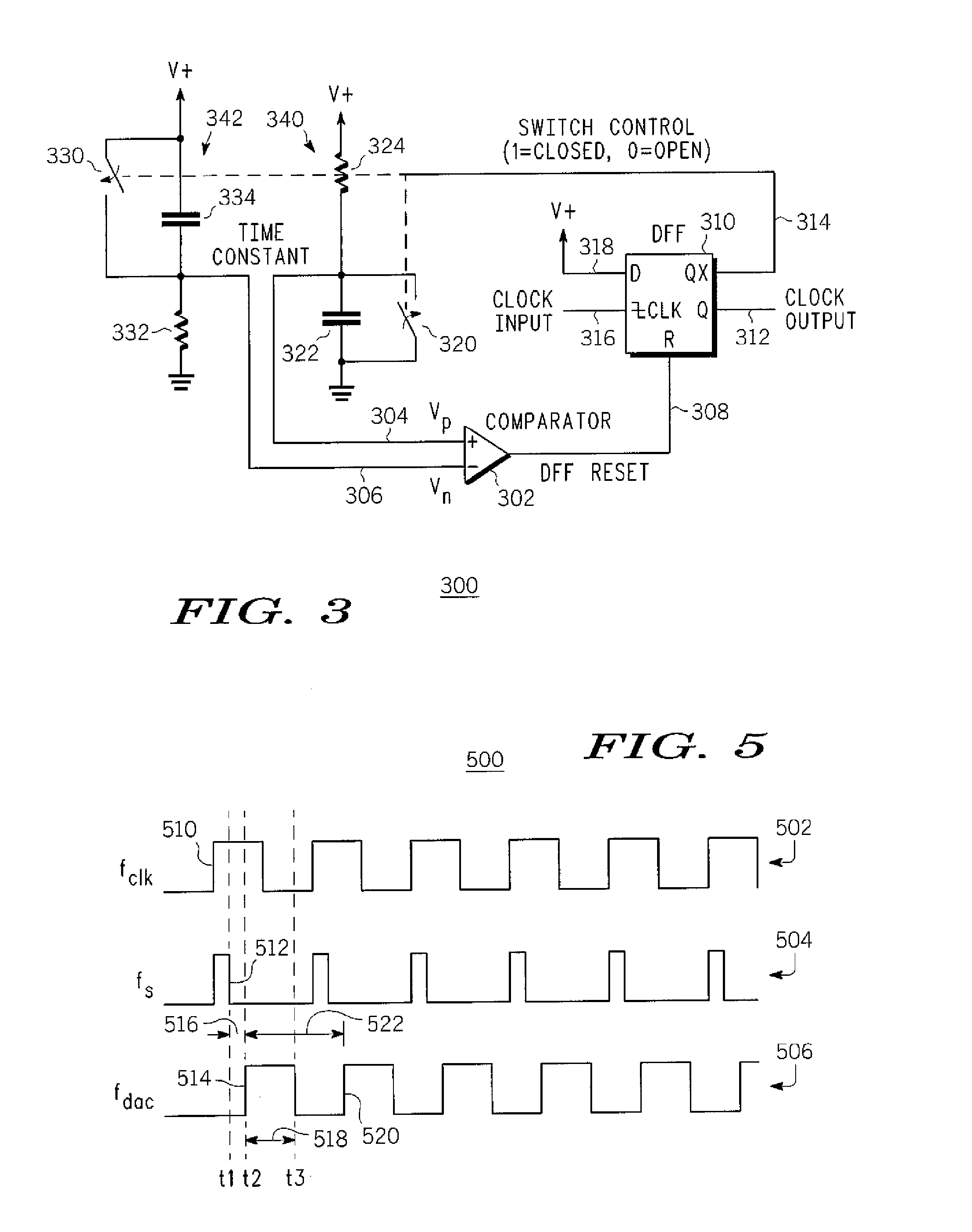

Clock jitter minimization in a continuous time sigma delta analog-to-digital converter

InactiveUS7397291B1Electric signal transmission systemsAnalogue conversionDigital analog converterDigital down converter

A digital-to-analog converter adapted for use as a feedback converter in a continuous time sigma delta analog-to-digital converter. The digital-to-analog converter has a discrete time digital signal input accepting digital signal samples that are synchronized with an assertion of a first data clock signal and a discrete time clock generator that generates an output pulse in response to receiving an assertion of the first data clock. The output pulse is asserted for a fixed duration that is independent of a jitter of the first data clock. The digital-to-analog converter also includes a continuous time analog output that produces, during assertion of the output pulse, a continuous time analog output signal having a magnitude corresponding to the digital signal samples.

Owner:NORTH STAR INNOVATIONS

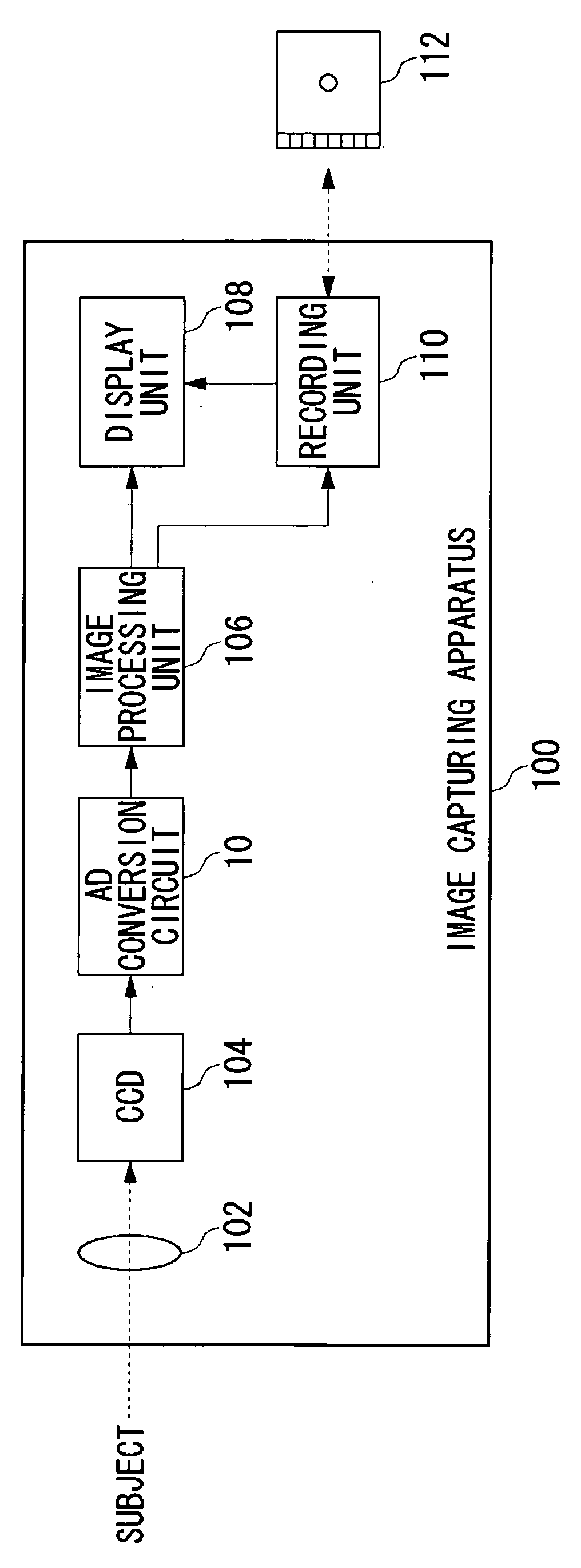

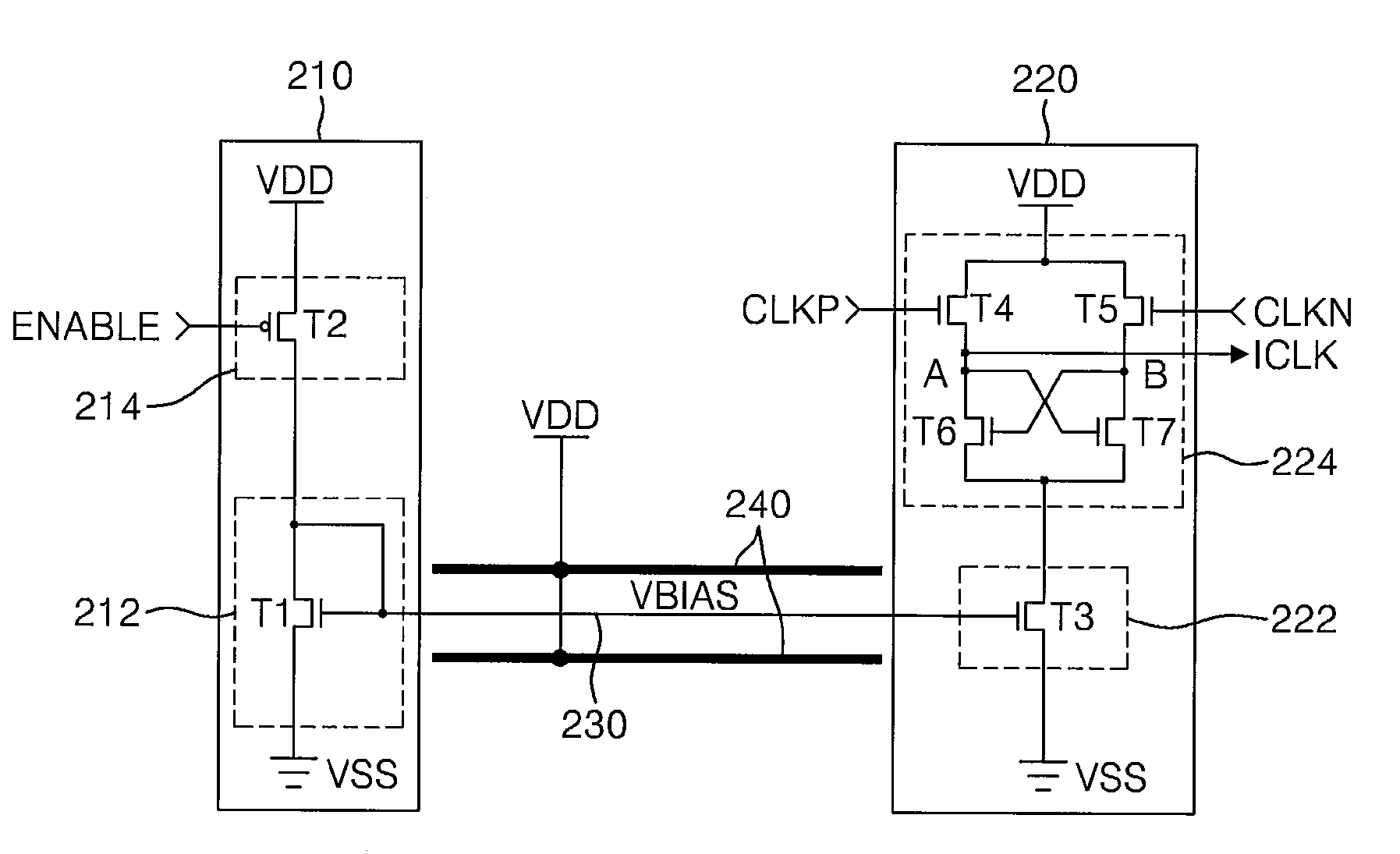

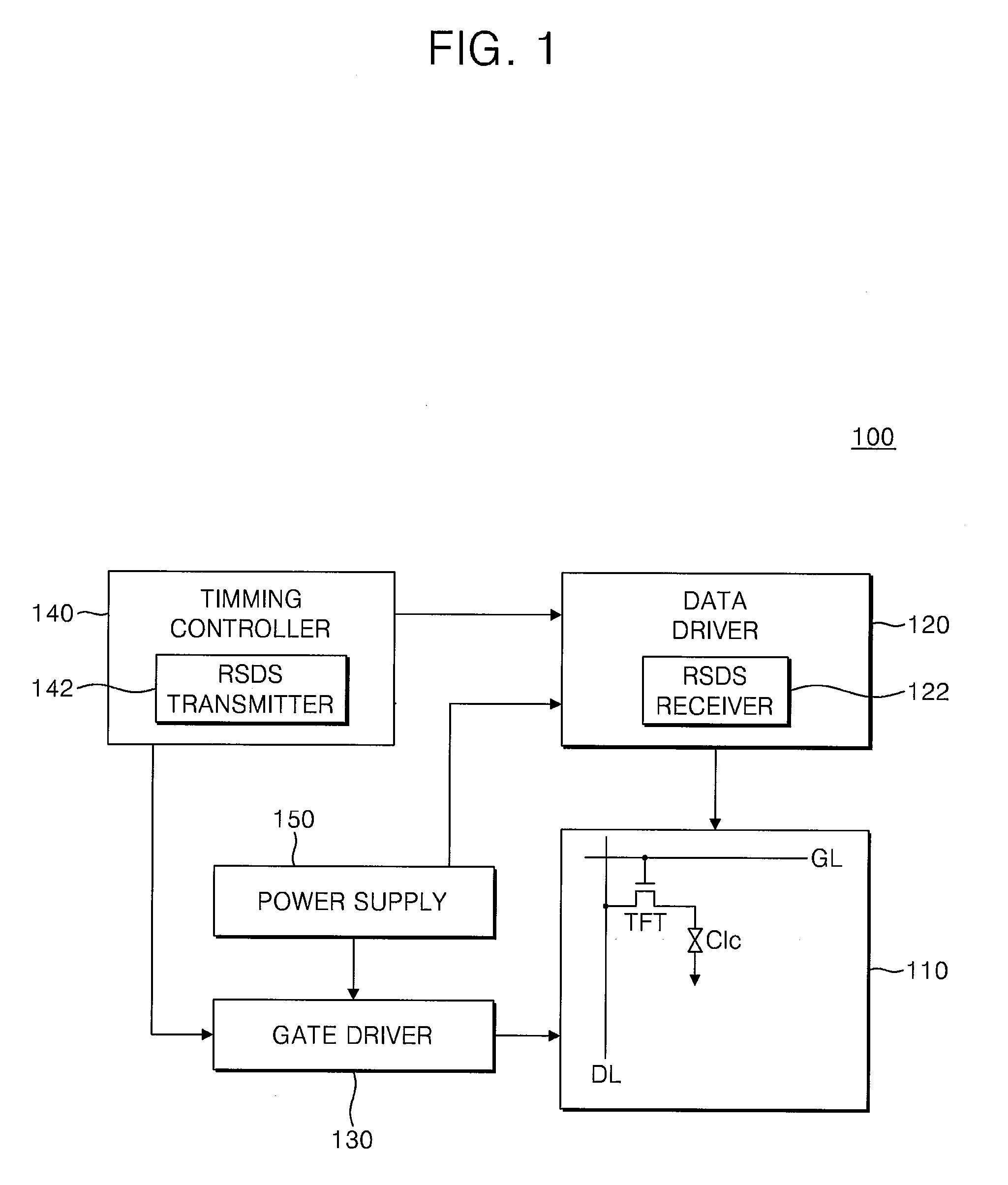

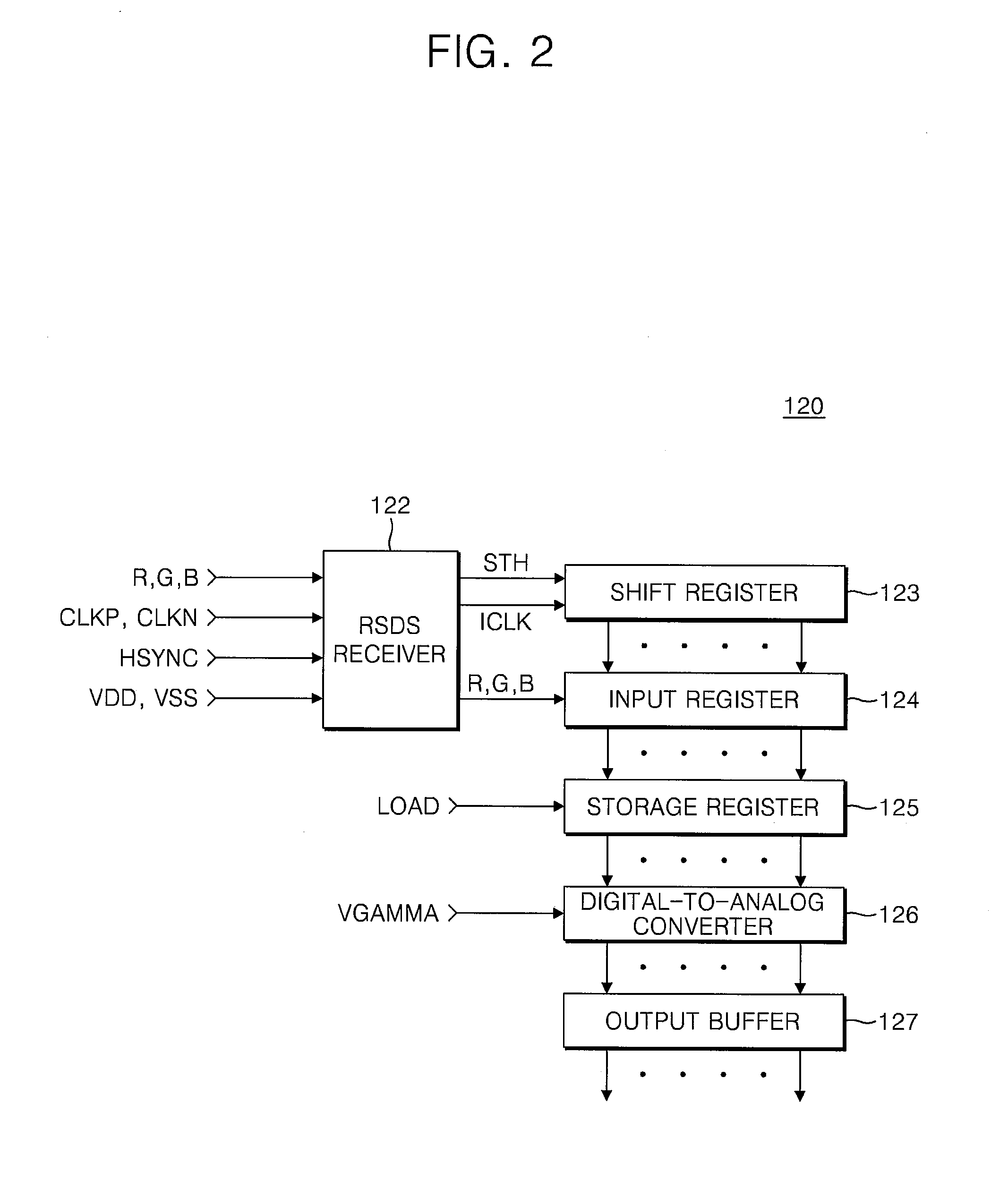

Clock generator, data driver, clock generating method for liquid crystal display device

InactiveUS20080106316A1Eliminate the problemStatic indicating devicesPulse generation by differential amplifiersLiquid-crystal displayClock generator

A clock generator and data driver for a liquid crystal display device in which the clock generator includes a bias voltage supply receiving a power supply voltage and generating a bias voltage, an internal clock generator converting differential clock signals into an internal clock signal in response to the bias voltage, a bias line electrically connecting the bias voltage supply and the internal clock generator to supply the bias voltage to the internal clock generator, and a shield line shielding the bias line and receiving a voltage having a level identical with a level of the bias voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

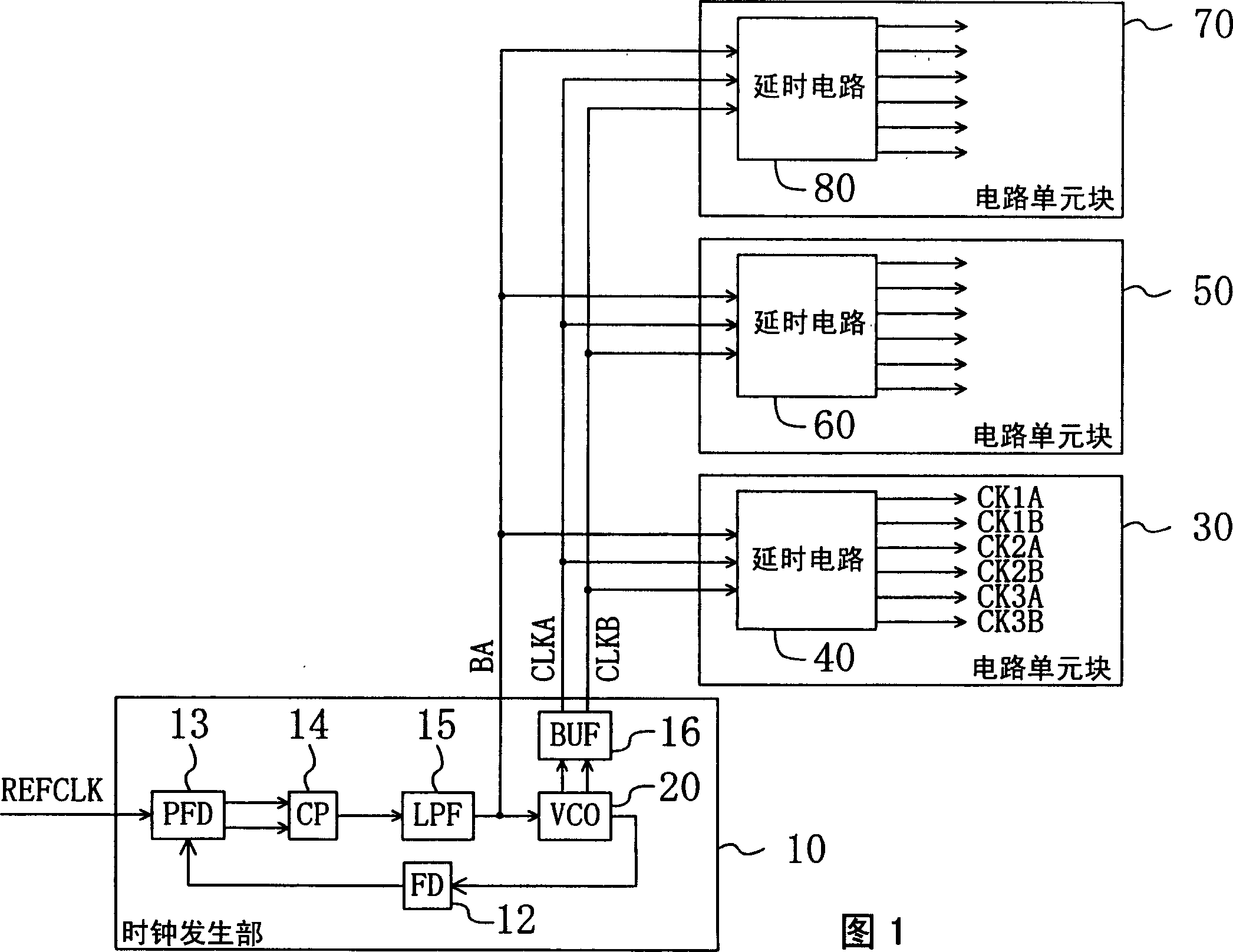

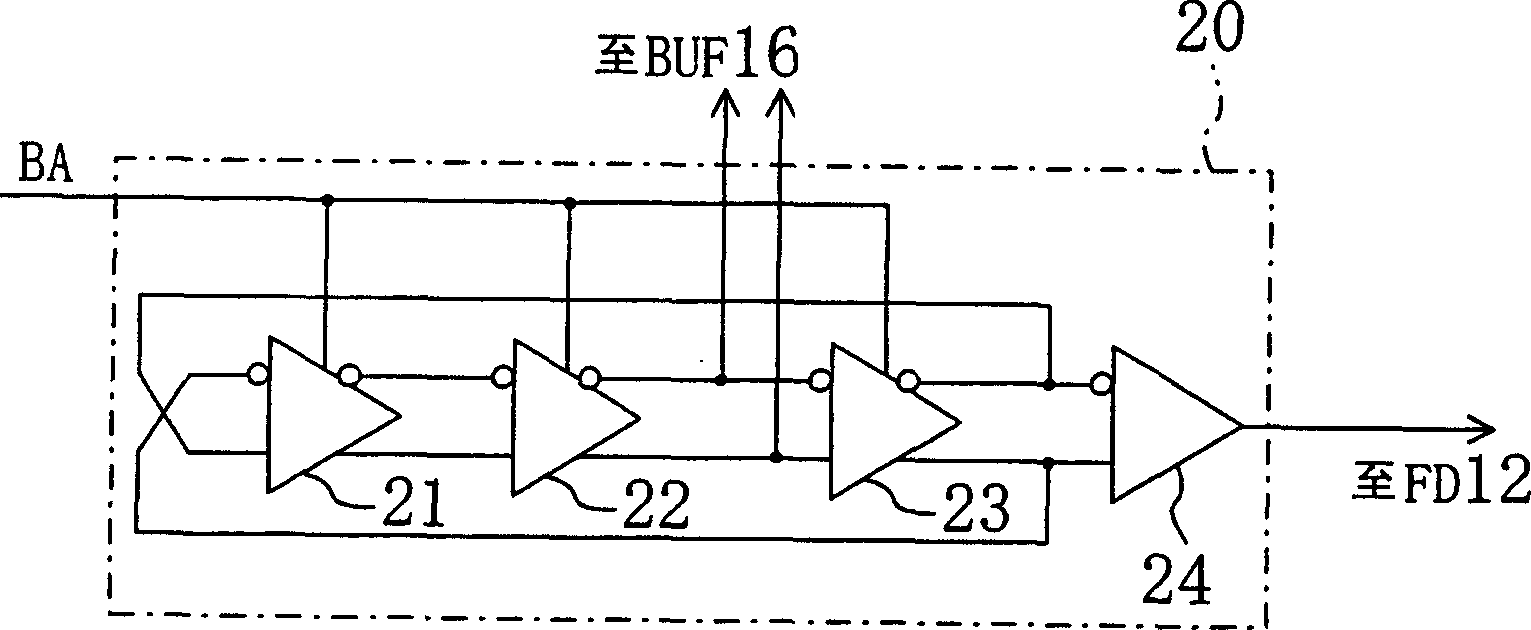

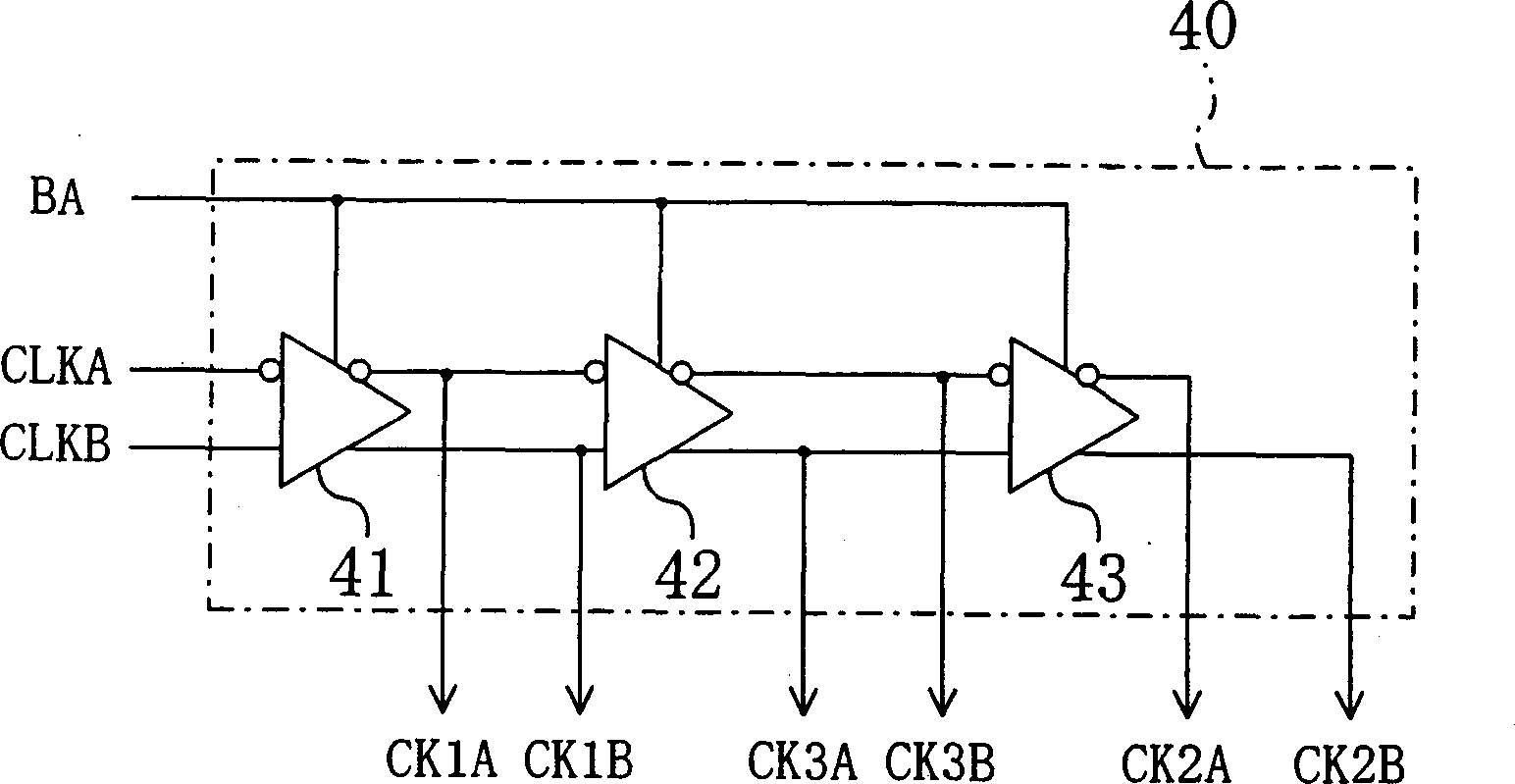

Multiphase clock transfer circuit and method

A multi-phase clock transmission circuit includes: a clock generator for generating a clock synchronizing with a reference clock and a control signal responsive to the phase difference between the reference clock and the generated clock; and a delay circuit for generating a multi-phase clock based on the clock and the control signal. The clock generator generates a signal having a frequency equal to an integral multiple of the frequency of the reference clock and outputs the signal as the clock. The delay circuit has a circuit receiving the clock and including a plurality of delay elements in cascade connection each giving a delay according to the control signal to an input signal. Signals output from the plurality of delay elements are used as signals constituting the multi-phase clock.

Owner:SOCIONEXT INC

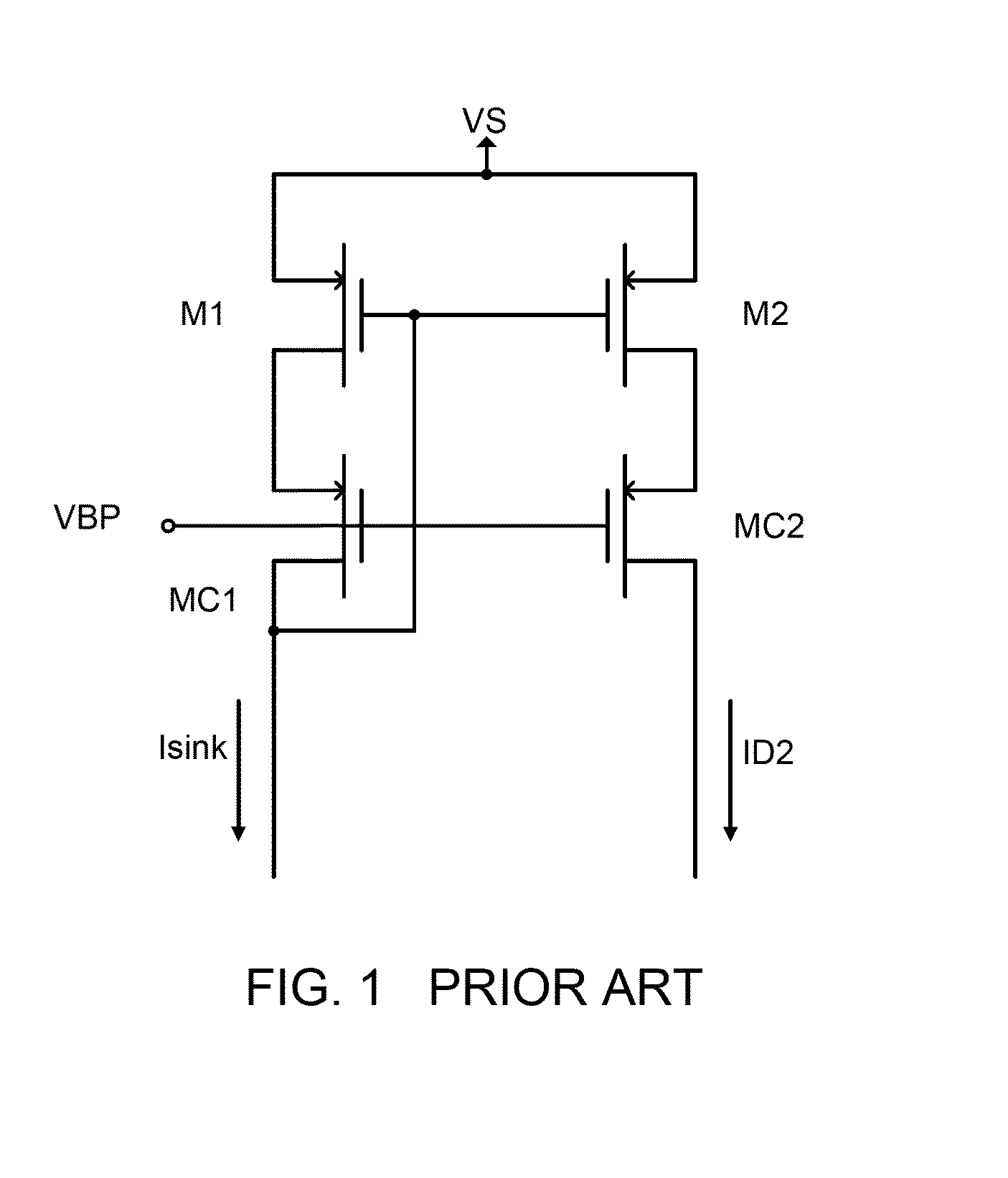

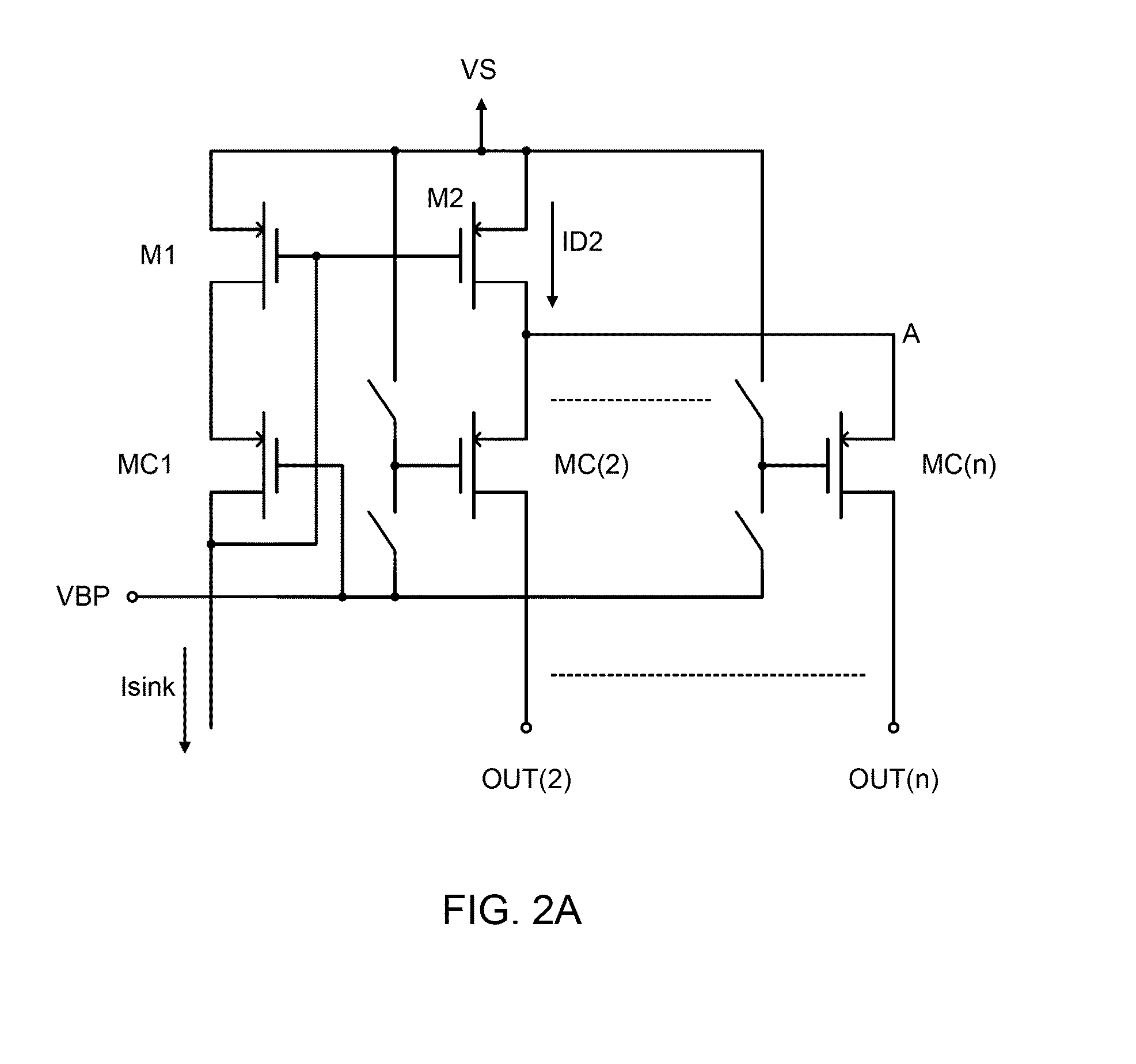

Comparator and relaxation oscillator employing same

ActiveUS8643443B1Pulse generation by bipolar transistorsMultiple input and output pulse circuitsPower flowRelaxation oscillator

A relaxation oscillator has a comparator that includes first through third bias current transistors coupled to a first supply rail. First and second input transistors form a pair of parallel coupled transistors connected to the first bias current transistor. A first current mirror control transistor connects the first input transistor to a second supply rail. A first current mirror output transistor is coupled to the first current mirror control transistor, and connects the second bias current transistor to the second supply rail. A second current mirror control transistor connects the second input transistor to the second supply rail. A second current mirror output transistor is coupled to the second current mirror control transistor, and connects the third bias current transistor to the second supply rail. A transition time reduction transistor, coupled across the third bias current transistor, is coupled to the second bias current transistor, and provides a comparator output.

Owner:NXP USA INC

Comparator and AD conversion circuit having hysteresis circuit

InactiveUS7196563B2Simple configurationImprove stabilityTelevision system detailsMultiple input and output pulse circuitsHysteresisVoltage reference

A comparator is provided, which compares an input voltage and a reference voltage by using a plurality of inverting circuits connected in series. The comparator includes a first inverting circuit, a second inverting circuit, a feedback path, and a capacitor arranged on the feedback path. The first inverting circuit inverts a difference between the input voltage and the reference voltage for output. The second inverting circuit further inverts the output of the first inverting circuit for output. The feedback path feeds back the output of the second inverting circuit to the input side of the first inverting circuit. The capacitor causes hysteresis such that an increasing threshold and a decreasing threshold of the second inverting circuit corresponding to an increase and a decrease of the input voltage have a difference therebetween.

Owner:ROHM CO LTD

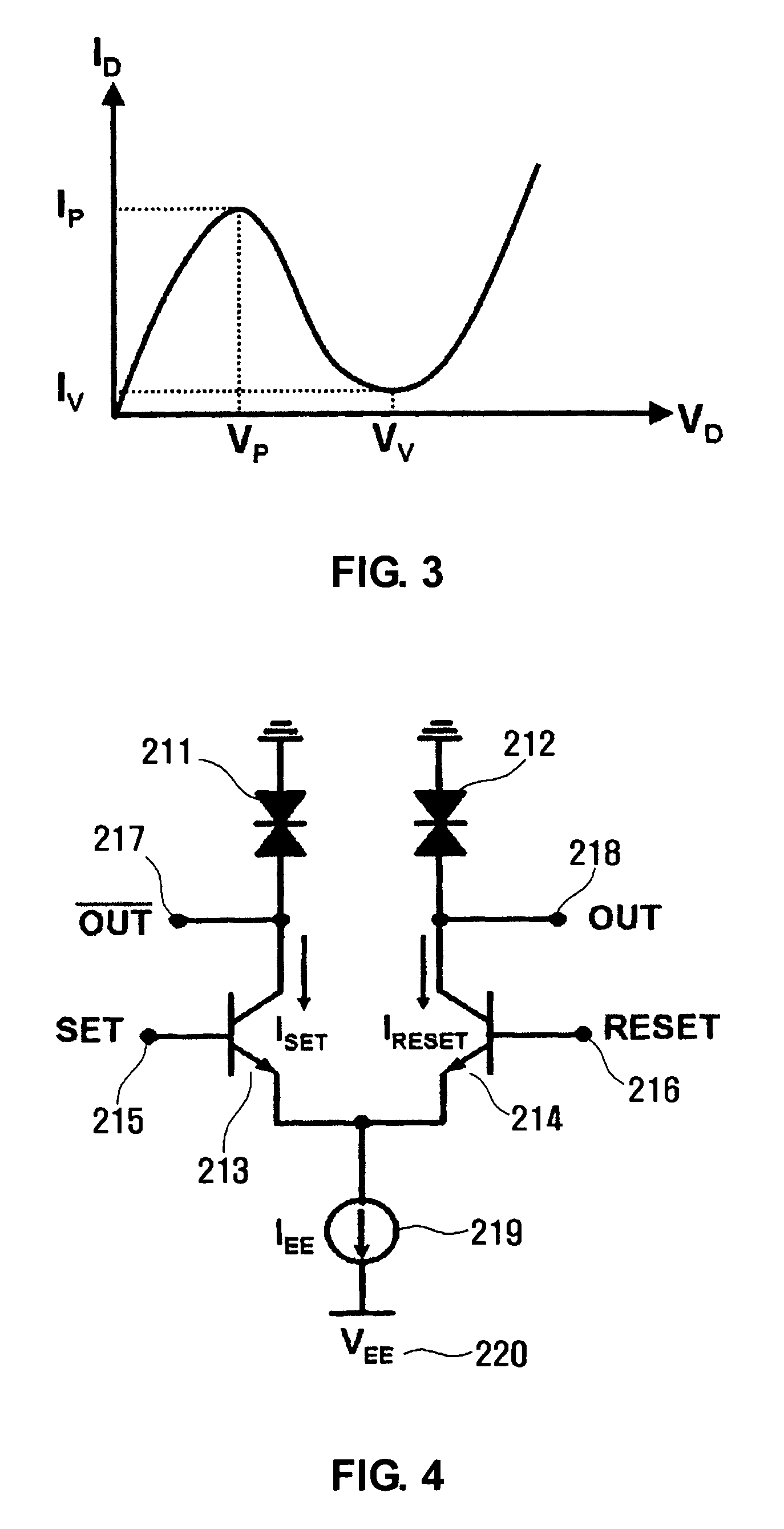

SET/RESET latch circuit, Schmitt trigger circuit, and MOBILE based D-type flip flop circuit and frequency divider circuit thereof

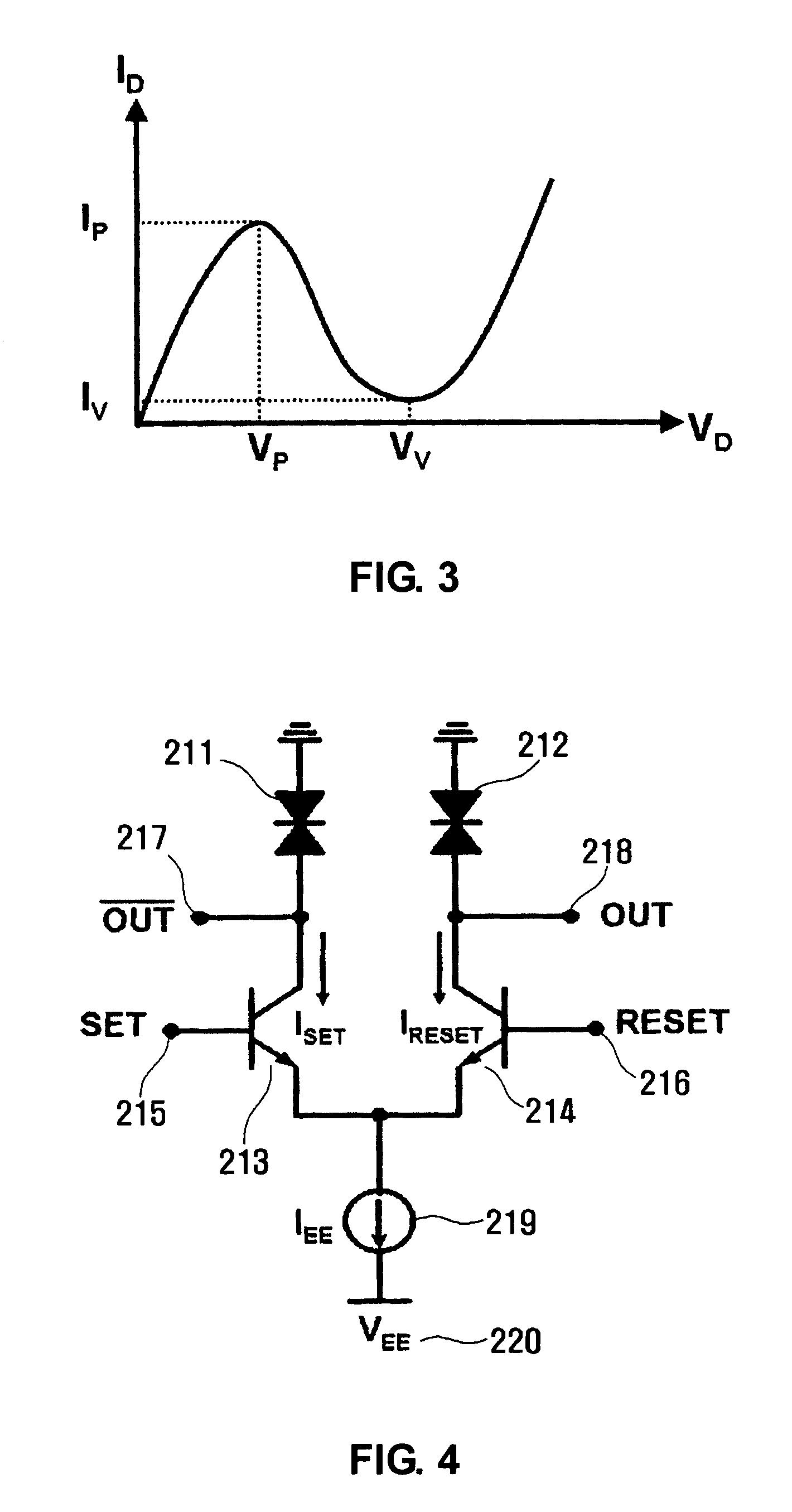

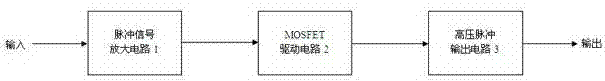

InactiveUS20070069810A1Easy to useHigh speedLogic circuits characterised by logic functionDiodeUltra high speedReturn-to-zero

The present invention relates to SET / RESET latch circuit, Schmitt trigger circuit, and MOBILE based D-type flip flop circuit and frequency divider circuit using the SET / RESET latch circuit and Schmitt trigger circuit. Herein, SET / RESET latch circuit is especially configured with CML-type transistors and negative differential resistance diodes. The SET / RESET latch circuit can be applied for very high speed digital circuits A SET / RESET latch circuit, characterized by including a transistor 1 and 2 in which each emitter of said transistors is commonly connected to a current source, and a negative differential resistance diode 1 and 2 which are respectively connected to each collector of said transistor 1 and 2; and additionally performing to be the relationship of IP<IEE<2·IP(where, IP: the peak current of said negative differential resistance diode 1 and 2, IEE: the current of the current source connected in series to the common node of emitters of said transistor 1 and 2); and thereby providing a single and differential Non-Return-to-Zero mode outputs in case that Return-to-Zero mode SET and RESET voltages are respectively supplied on the base ports of said transistor 1 and 2.

Owner:KOREA ADVANCED INST OF SCI & TECH

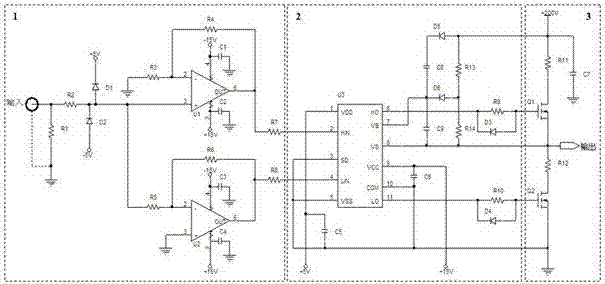

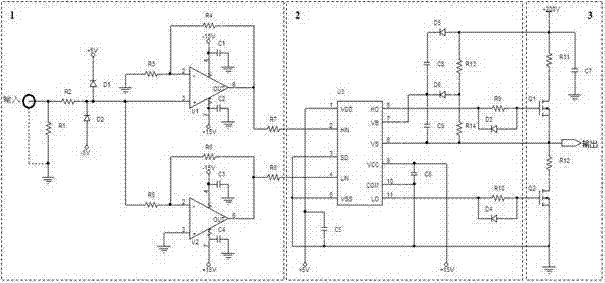

High frequency high voltage pulse generator

InactiveCN102355236AOvercoming qualityOvercoming repetitivenessPulse generation by differential amplifiersMOSFETHigh voltage pulse

A high frequency high voltage pulse generator is a pulse driving and emission source which is applied to fields of display measurement, display drive, communication technology and the like. The generator comprise a pulse signal amplification circuit, a MOSFET (Metal Oxide Semiconductor Field Effect Transistor) driving circuit, and a high voltage pulse output circuit which are in serial connection in order. An input terminal of the pulse signal amplification circuit is an input terminal of the generator, and an output terminal of the high voltage pulse output circuit is an output terminal of the generator. An upper end suspension power supply of the MOSFET driving circuit of the generator is formed by a high voltage pulse attenuator, so a positive / negative high frequency pulse which has a duty ratio of 0.005 % in a frame period and meets a technical index is generated in the display measurement, a maintenance pulse which has a duty ratio of 50% and satisfies more than 8 subfields is provided in the display drive, and an emission source pulse which 100% operating efficiency, large power and low loss is outputted in the communication technology.

Owner:SOUTHEAST UNIV

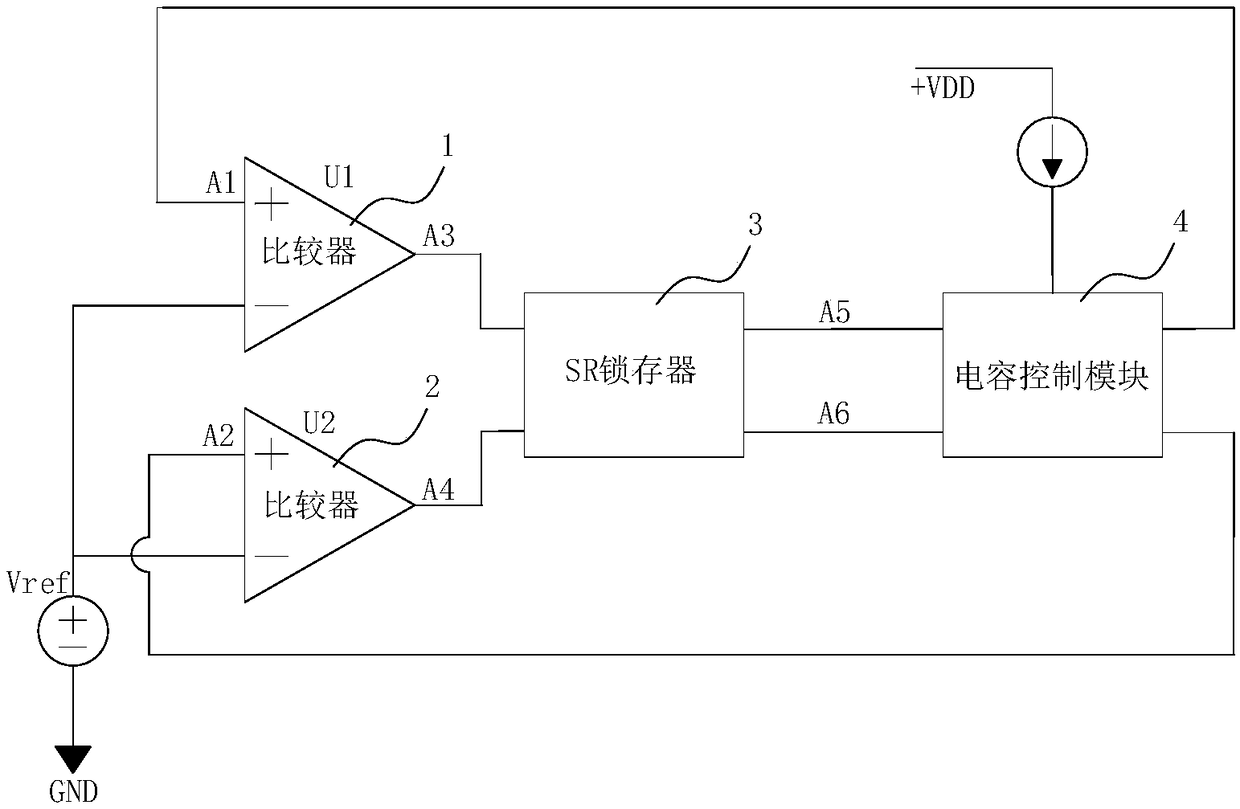

Relaxation oscillator

PendingCN108880507AHigh speedFrequency stabilityPulse generation by differential amplifiersCapacitanceExternal bias

The invention provides a relaxation oscillator, comprising a first comparator, a second comparator, an SR latch and a capacitor control module. An input terminal of the first comparator is coupled with a capacitor control module and an external reference threshold voltage, and an output terminal of the first comparator is coupled with an input terminal of the SR latch. An input terminal of the second comparator is coupled with the capacitor control module and the external reference threshold voltage, and an output terminal of the second comparator is coupled with the input terminal of the SR latch. An output terminal of the SR latch is coupled with an input terminal of the capacitor control module. A bias current input terminal of the capacitor control module is coupled to an external biascurrent source. A control signal is generated by inputting a first comparison signal generated by the first comparator and a second comparison signal generated by the second comparator into the SR latch according to the external reference threshold voltage, and a first capacitor and a second capacitor are controlled to periodically charge and discharge to generate an oscillation signal accordingto a bias current of the external bias current source and the control signal output from the SR latch.

Owner:HANGZHOU HONGXIN MICROELECTRONICS TECH CO LTD

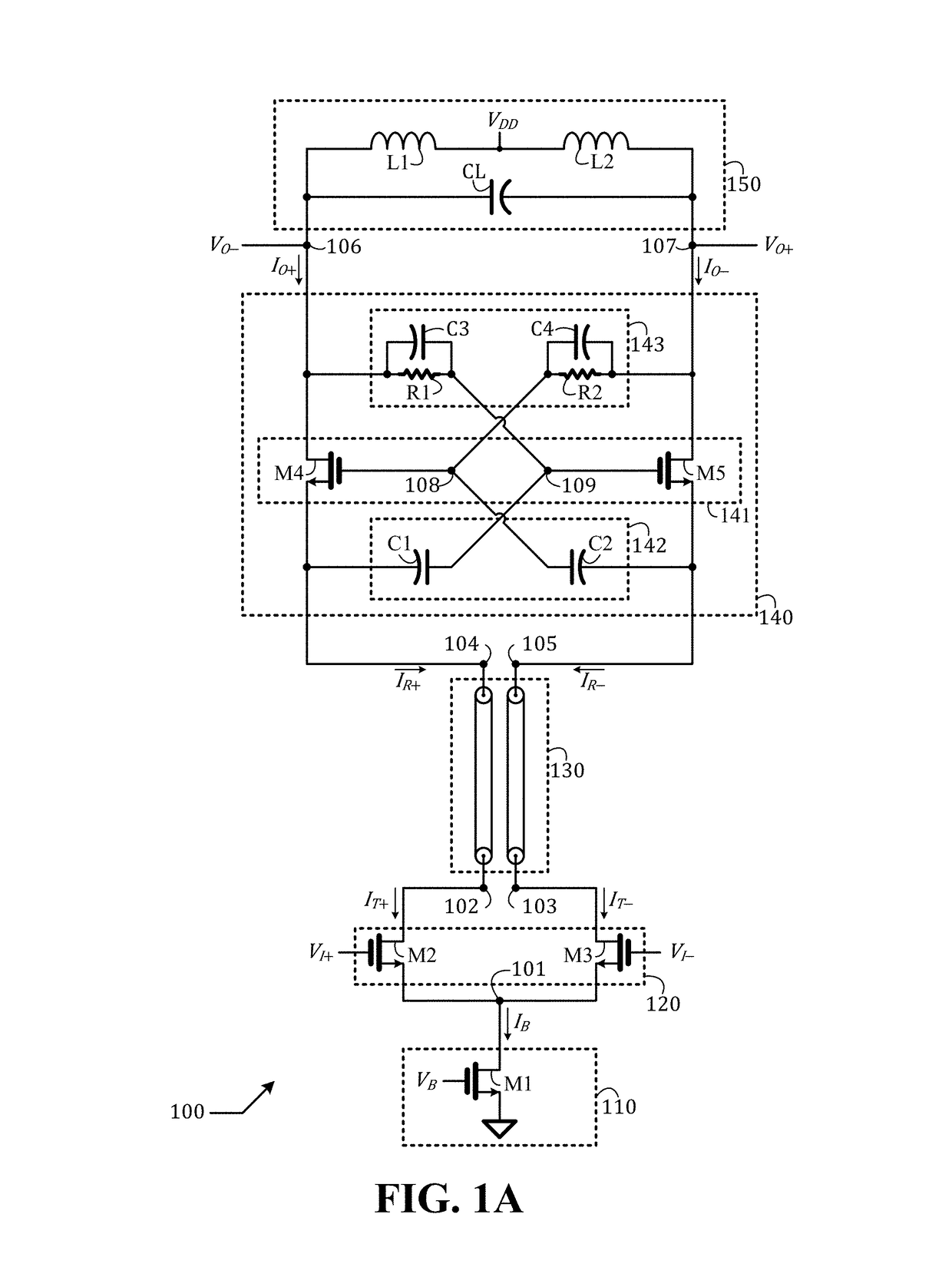

Method and apparatus for high speed clock transmission

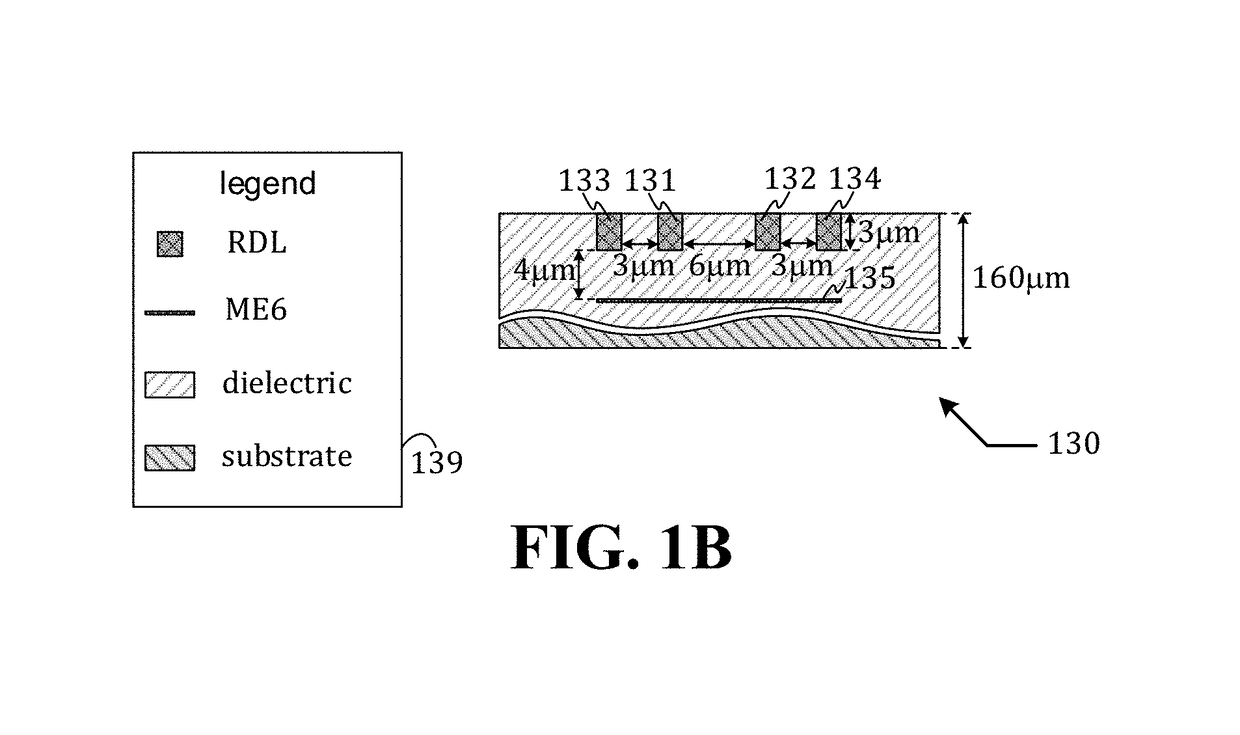

ActiveUS10224905B1Lower input impedanceIncrease output impedanceLogic circuit coupling arrangementsPulse generation by differential amplifiersDifferential transmissionEngineering

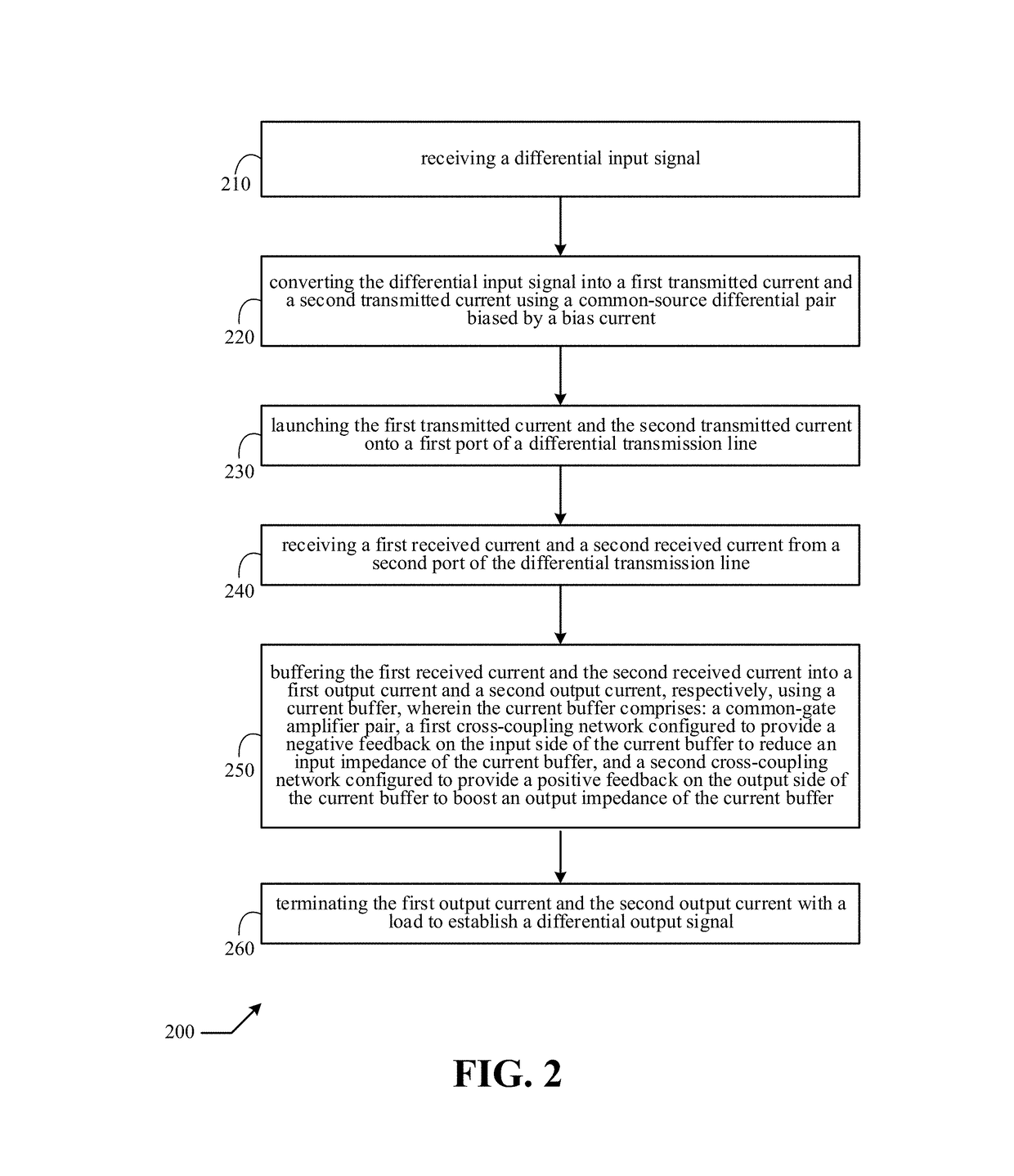

A method comprises: receiving a differential input signal; converting the differential input signal into a first transmitted current and a second transmitted current using a common-source differential pair biased by a bias current; launching the first transmitted current and the second transmitted current onto a first port of a differential transmission line; receiving a first received current and a second received current from a second port of the differential transmission line; buffering the first received current and the second received current into a first output current and a second output current, respectively, using a current buffer, wherein the current buffer comprises: a common-gate amplifier pair, a first cross-coupling network configured to provide a negative feedback on the input side of the current buffer to reduce an input impedance of the current buffer, and a second cross-coupling network configured to provide a positive feedback on the output side of the current buffer to boost an output impedance of the current buffer; and terminating the first output current and the second output current with a load to establish a differential output signal.

Owner:REALTEK SEMICON CORP

Popular searches

Electrial characteristics varying frequency control Pulse manipulation Ac network voltage adjustment Electric variable regulation Artificial respiration Pulse duration/width modulation Generating/distributing signals Sinusoidal oscillation interference reduction Pulse frequency/rate modulation Pulse generation with predetermined statistical distribution