High-linearity relaxation oscillator

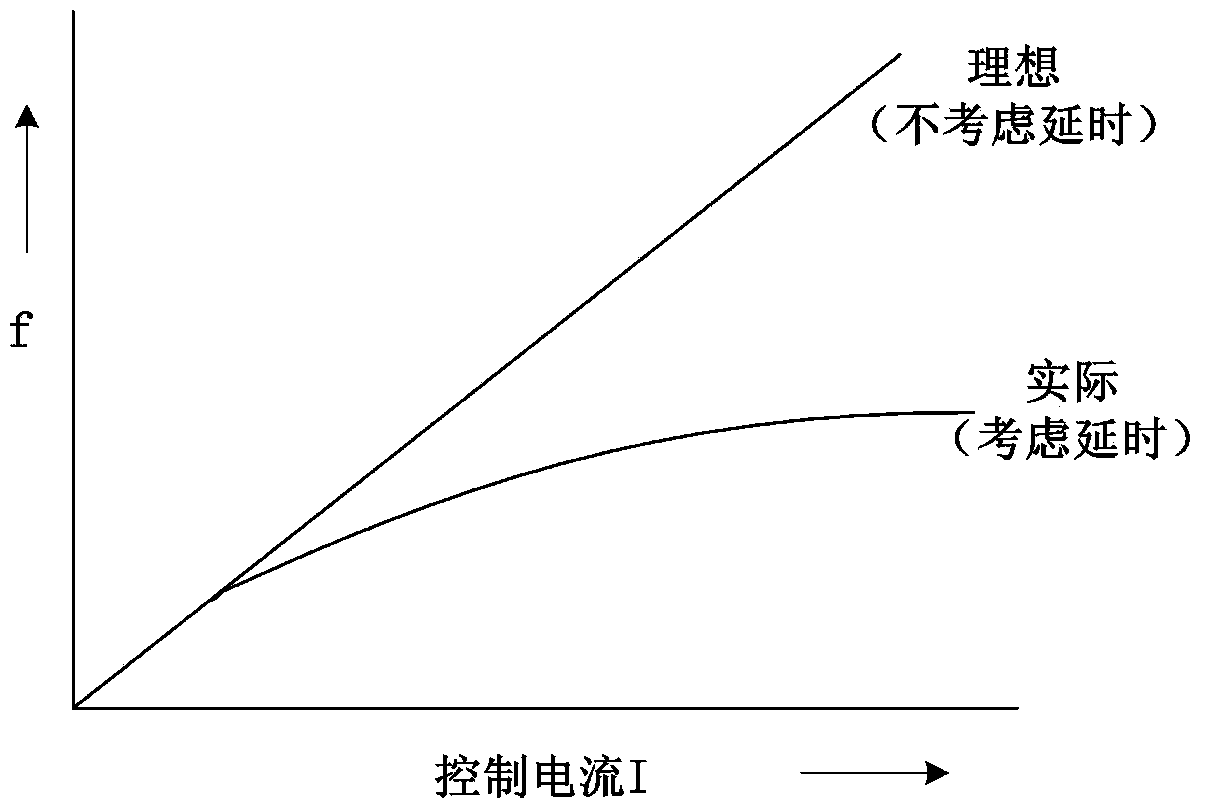

A relaxation oscillator and high linearity technology, applied in the direction of electric pulse generator circuit, differential amplifier to generate pulses, etc., can solve the problems of reducing frequency-controlling current linearity, limiting the maximum frequency range of the oscillator, etc., to improve linearity Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

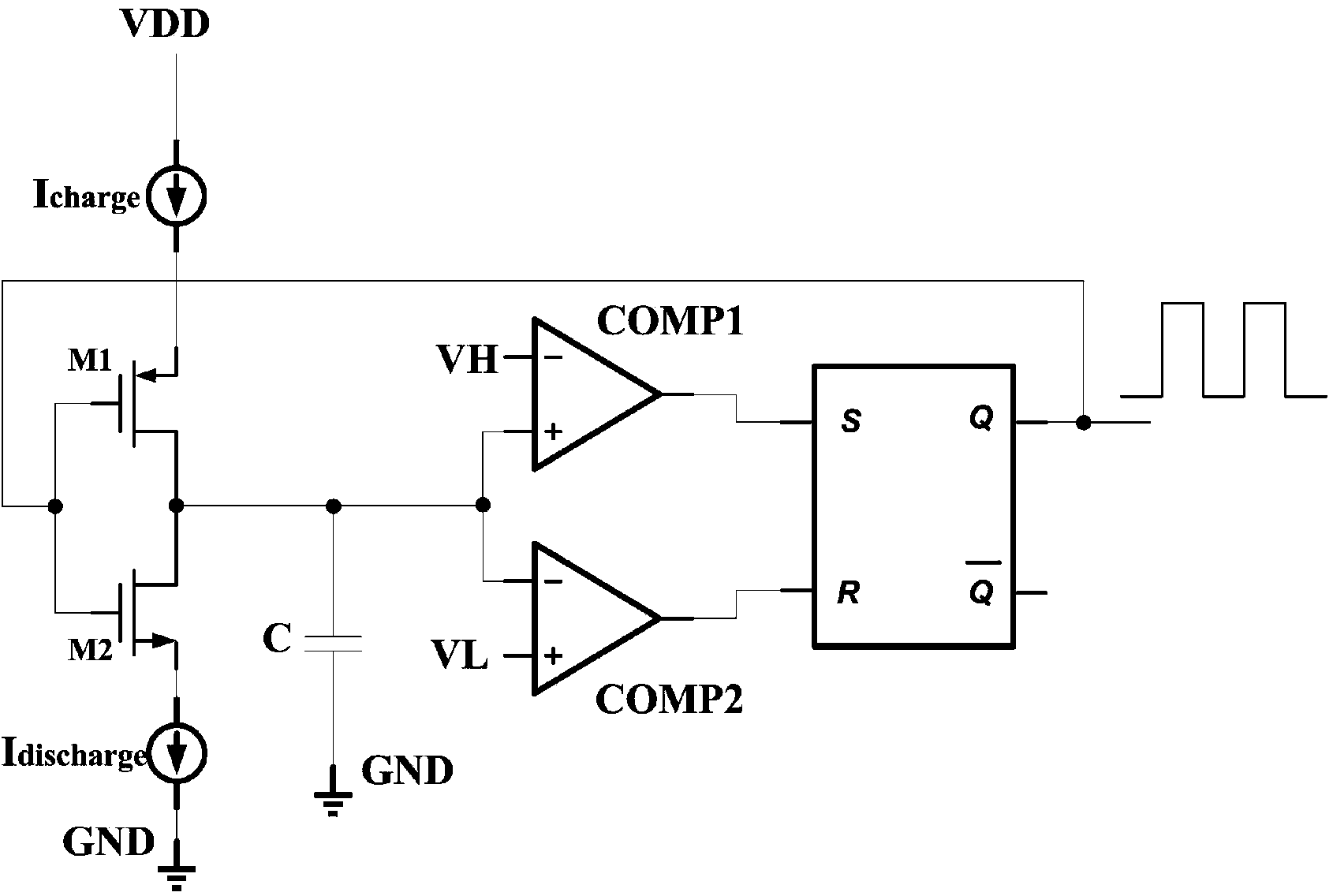

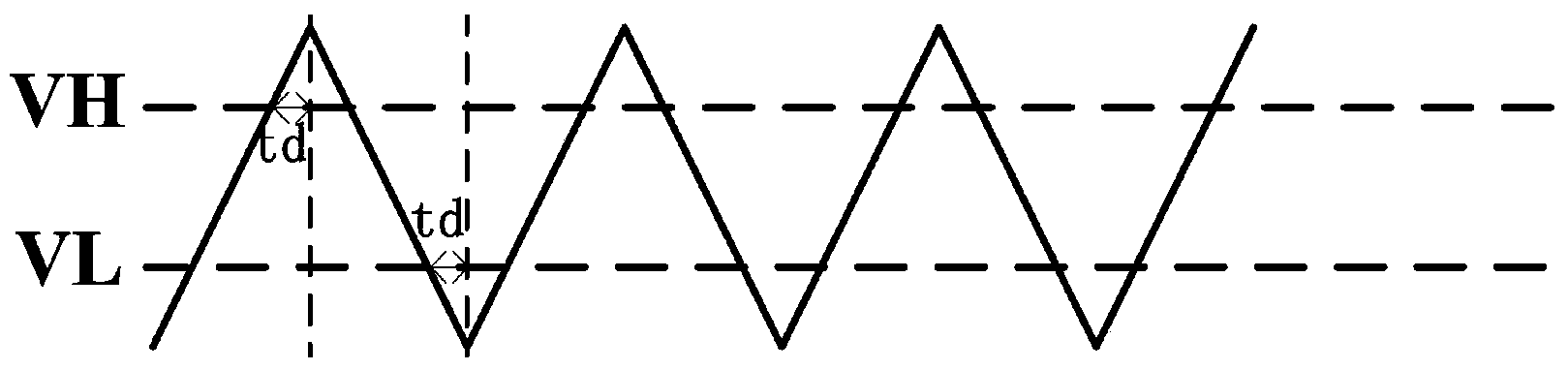

[0058] refer to Figure 6 The relaxation oscillator with high linearity of the present invention includes an oscillation circuit 1, a reference level self-adjustment circuit 2, and a transmission gate selection signal generation circuit 3, wherein the non-ground terminal output of the capacitor C1 in the oscillation circuit 1 is connected to the reference level self-adjustment The input of the circuit 2, the output of the reference level self-adjusting circuit 2 are connected to the inverting terminals of the first comparator COMP1 and the second comparator COMP2 in the oscillation circuit 1, and the output V of the transmission gate selection signal generation circuit 3 φ Connected to the gate terminal of the PMOS of the first transmission gate TG1 in the reference level self-adjusting circuit 2 and the gate terminal of the NMOS of the second transmission gate TG2, the output of the transmission gate selection signal generation circuit 3 It is connected to the NMOS gate term...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More