Multiphase clock transfer circuit and method

A technology of multi-phase clock and clock generation circuit, which is applied in the direction of electric pulse generator circuit, transmission system, electrical components, etc., and can solve the problems of increased clock time lag, increased wiring area, and wrong operation of circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

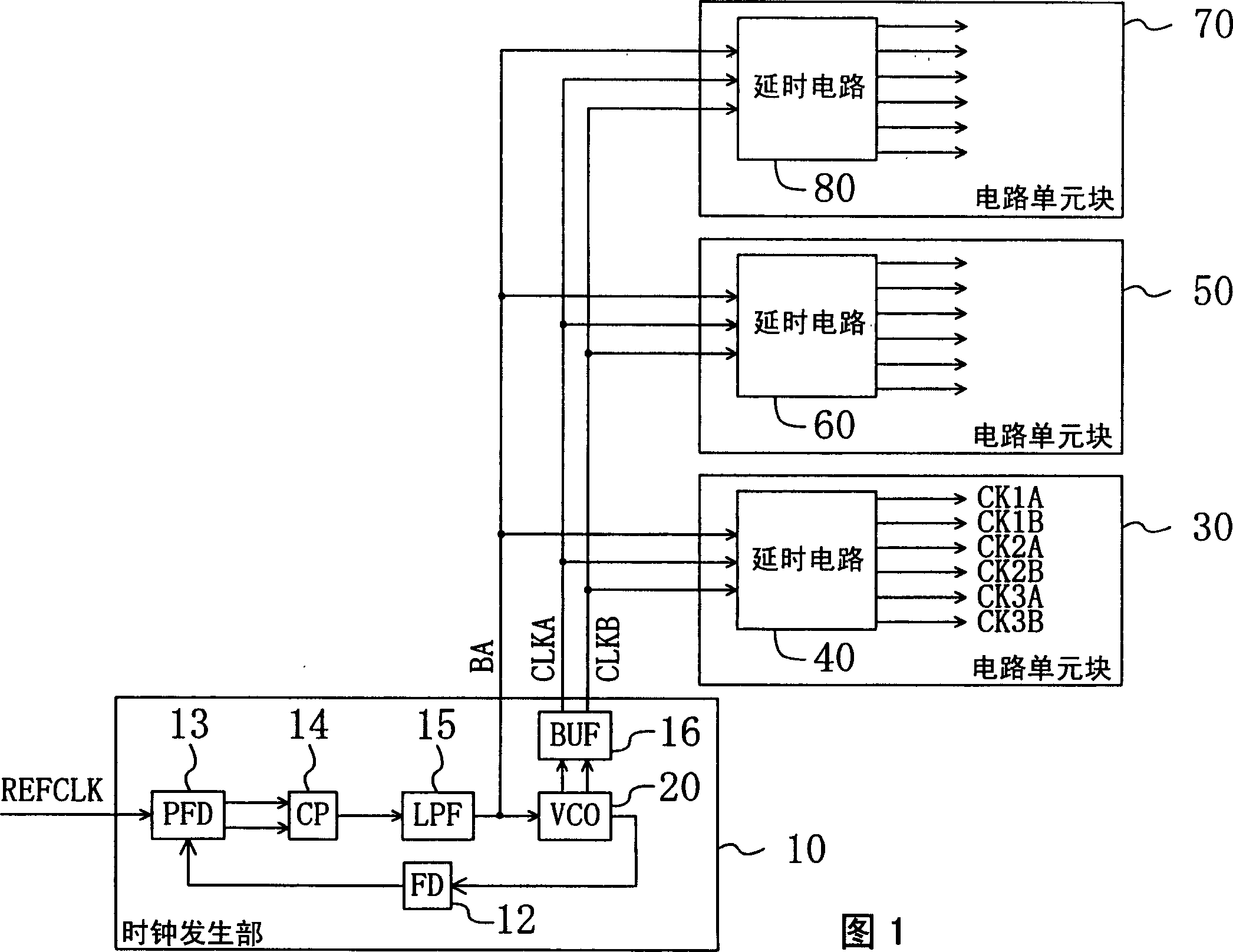

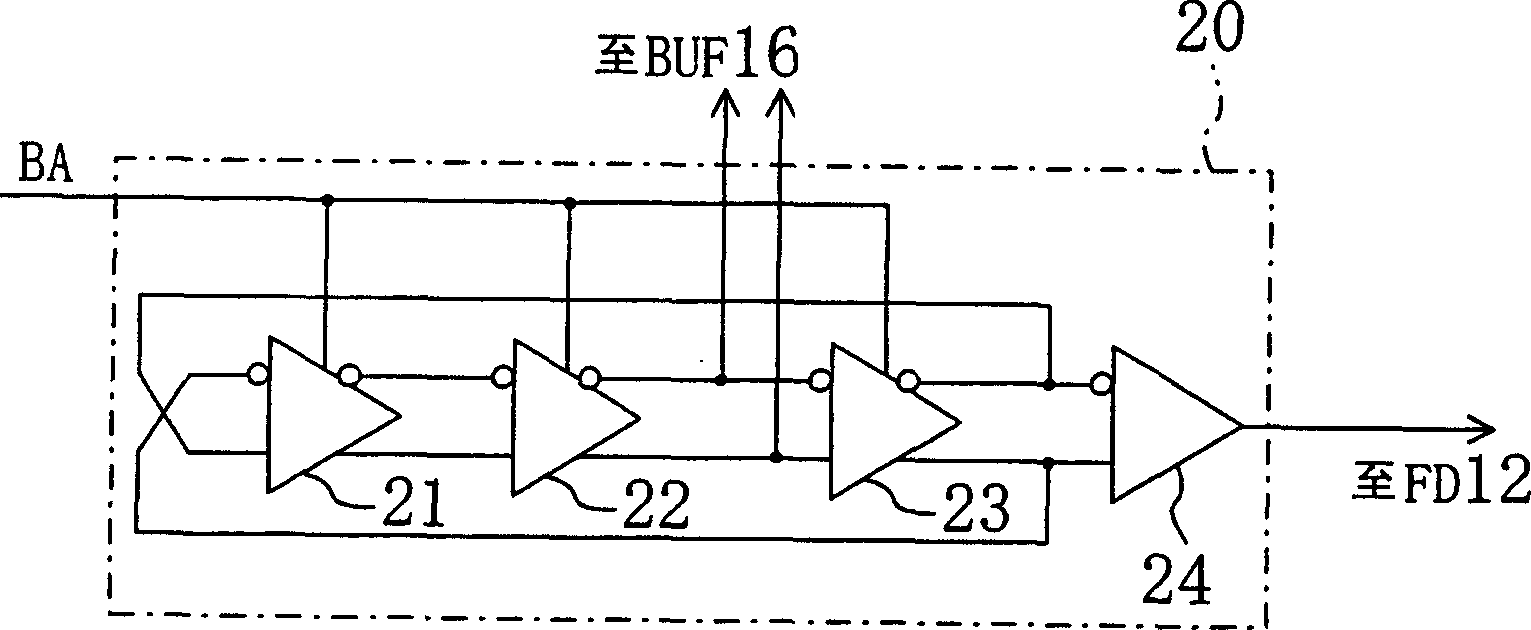

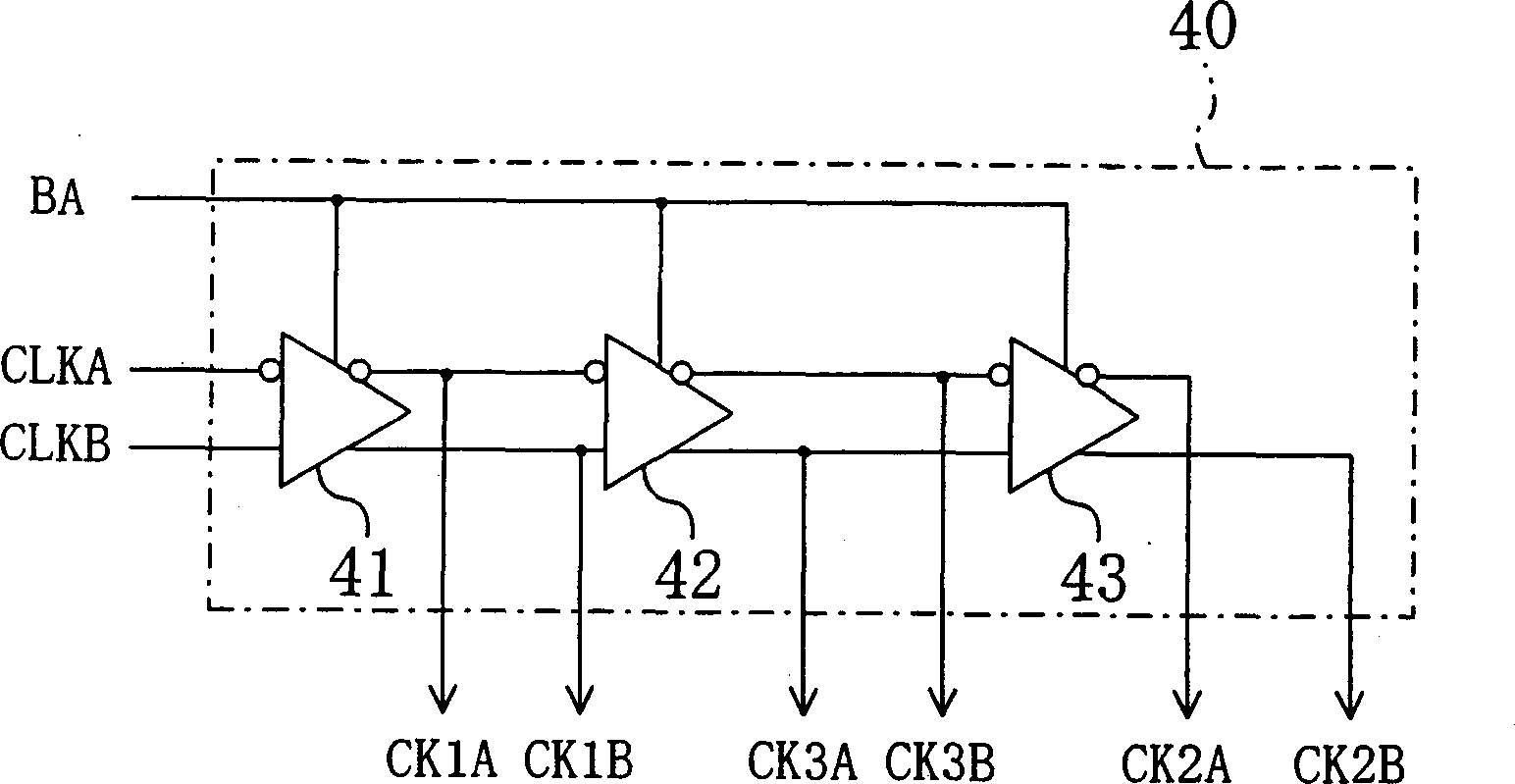

[0059] 1 is a block diagram of a semiconductor integrated circuit having a multiphase clock transfer circuit according to Embodiment 1 of the present invention. In FIG. 1 , the multiphase clock transfer circuit has a clock generation section 10 and delay circuits 40 , 60 and 80 . The delay circuits 40, 60 and 80 include clock circuit unit blocks 30, 50 and 70, respectively. The circuit unit blocks 30, 50, and 70 all employ multi-phase clocks for signal processing and the like.

[0060] The clock generating unit 10 has a frequency divider (FD) (frequency divider) 12, a phase frequency comparator (PFD) (phase frequency detector) 13, a charge pump (CP) 14, a low-pass filter (LPF) 15, a buffer ( BUF) 16 and a voltage controlled oscillator (VCO) (voltage controlled oscillator) 20 as a clock generating circuit. The phase-frequency comparator 13 and the charge pump 14 operate as a phase comparison circuit. The phase-frequency comparator 13, the charge pump 14, the low-pass filter ...

Embodiment 2

[0110] When the distance between the clock generation unit and the circuit block is large, variations in transistor characteristics are likely to occur, and inconsistencies in power supply potentials and ground potentials are also likely to occur. In this case, the delay amount of the clock generation part and the delay unit of a segment on the circuit unit block will not be consistent. In order to avoid the occurrence of this kind of situation, a circuit for correcting delay is installed on the delay circuit.

[0111] Figure 12 It is a circuit diagram of the delay circuit of the multi-phase clock transmission circuit according to Embodiment 2 of the present invention. Figure 12 The delay circuit has an alternative to the image 3 The delay units 341, 342 and 343 of the delay units 41-43 on the delay circuit 40 also have a delay correction circuit 345. The delay correction circuit 345 has a phase comparator (PD) 346 , a charge pump (CP) 347 and a low-pass filter (LPF) 348...

Embodiment 3

[0126] In the above embodiments, the technique for maintaining the frequency of the clock and the phase difference between multi-phase clocks in each circuit block has been described. In Embodiment 3, a technique for matching the phases of clocks between different circuit block blocks will be described. For example Figure 8 As shown, when the clock CKDA / CKDB is transmitted to each circuit unit block using a buffer, the phase inconsistency of the clock input to each circuit unit block will arise. This is because not only the distance from the clock generation unit to each circuit block is different, but also the number of buffers through which the clock passes differs depending on the circuit block.

[0127] Figure 14 It is a block diagram of an integrated circuit with a multi-phase clock transmission circuit according to Embodiment 3 of the present invention. exist Figure 14 , the multiphase clock transfer circuit has Figure 8 Clock generator 110, buffers 501, 502, 503,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More