Parasitic parameter extraction method suitable for high speed IC-QFN packaging design utilization

A technology of IC-QFN and parasitic parameters, which is applied in special data processing applications, computing, electrical digital data processing, etc., and can solve problems such as signal waveform distortion, crosstalk, reflection, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The technical solution will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0020] A method for extracting package parasitic parameters suitable for high-speed IC-QFN package design and application proposed in the embodiment of the present invention, its specific technical solutions include:

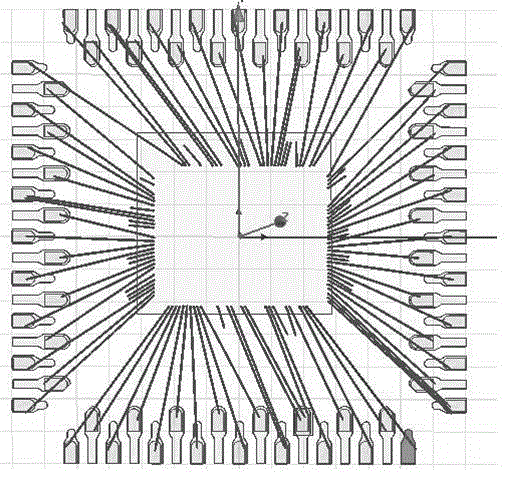

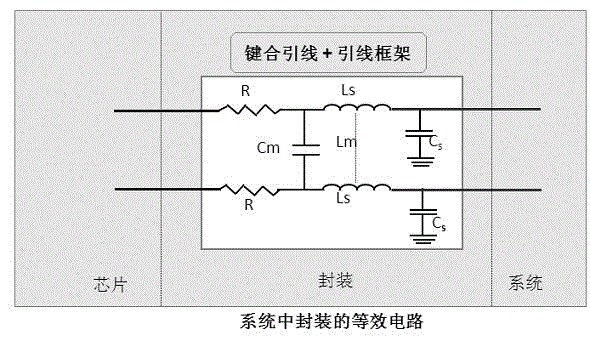

[0021] (1) Establish a three-dimensional physical model of the QFN package lead frame and bonding wire: give the physical parameters of different design dimensions of the lead frame and bonding wire suitable for the QFN package structure, including lead frame thickness, pin spacing, One or several design parameters such as the length of the bonding wire and the diameter of the bonding wire. Each parameter needs to give design dimensions of not less than four values. Then use three-dimensional electromagnetic field analysis software such as HFSS to establish a three-dimensional physical model, the effect of the model is as follo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More