n-type ldmos device and manufacturing method thereof

A manufacturing method and n-type technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of affecting the electrical isolation of the device, limiting the application range of the device operating voltage, and reducing the punch-through voltage. The effect of design margins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

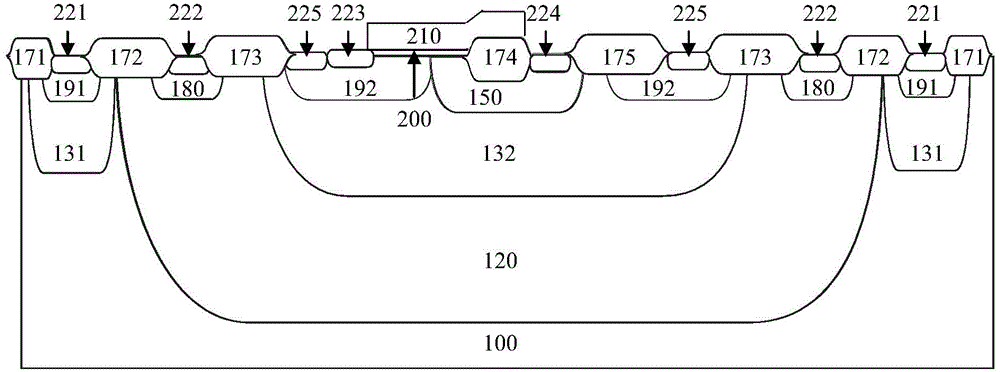

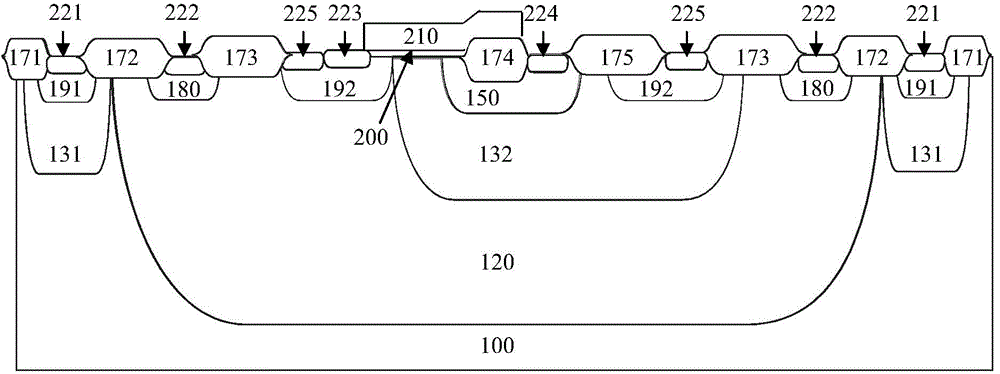

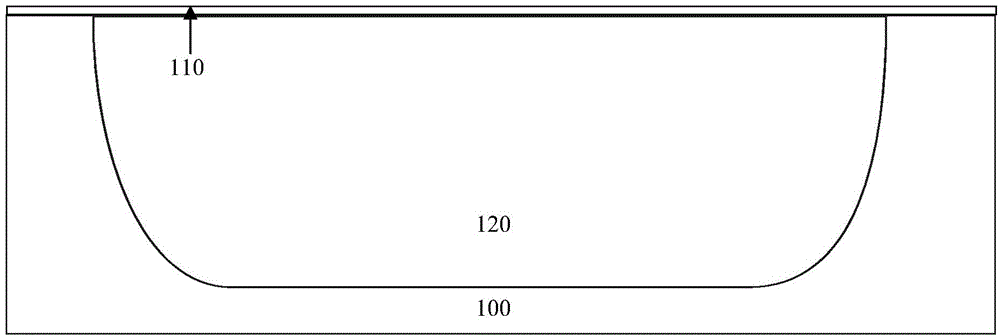

[0025] See Figure 5 , This is a schematic diagram of the cross-sectional structure of the n-type LDMOS device of the present application. The p-type lightly doped silicon substrate (or epitaxial layer) 100 has a lightly doped deep n-well 120 and a lightly doped p-well 131. The deep n-well 120 has the maximum junction depth. If viewed from a top view, the lightly doped p-well one 131 is a ring structure, surrounded by the outer side of the deep n-well 120, and the sides of the two are in contact with each other. The deep n-well 120 has a lightly doped p-well two 132, a heavily doped p-well two 192, and a heavily doped n-well two 180. The second heavily doped p-well 192 has a ring shape and is divided into two parts. The first part is directly in the deep n-well 120, and the second part is in the lightly doped p-well two 132. The first part of the second heavily doped p-well 192 and the side surface of the second lightly doped p-well 132 are in contact with each other. The r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More