FPGA chip and FPGA system

A chip and data selector technology, applied in the detection of faulty computer hardware, program control devices, etc., can solve the problems of occupying more FPGA chip pins, complex operation, and improving the complexity of FPGA system wiring.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The FPGA chip and the FPGA system of the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0043] It should be clear that the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

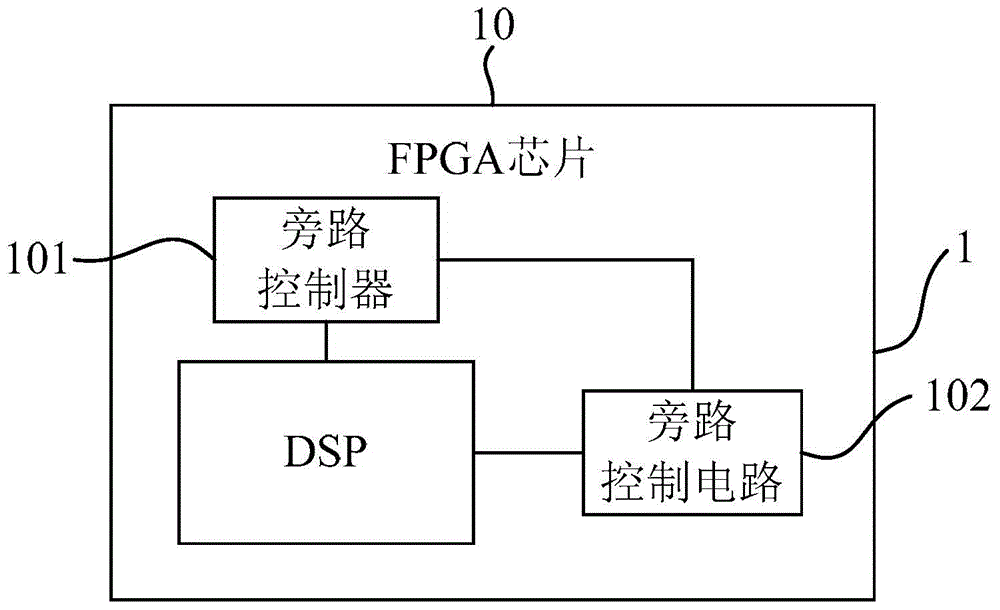

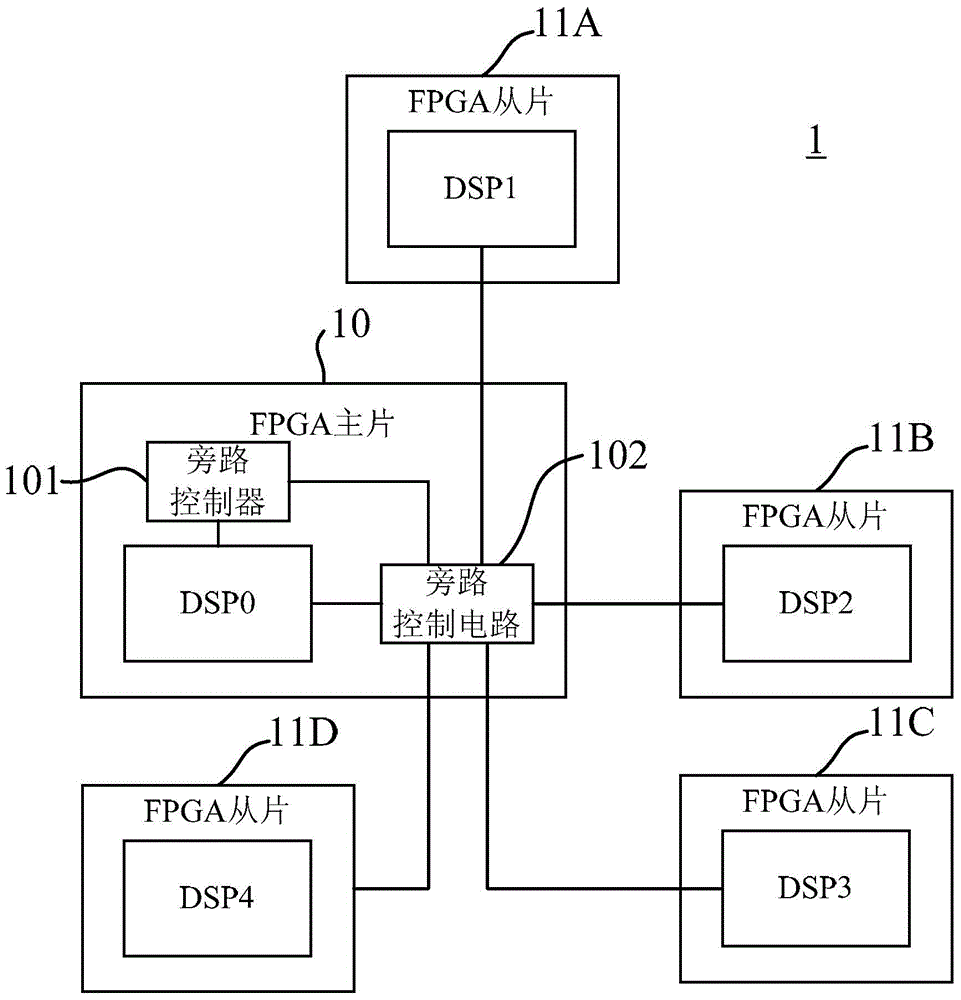

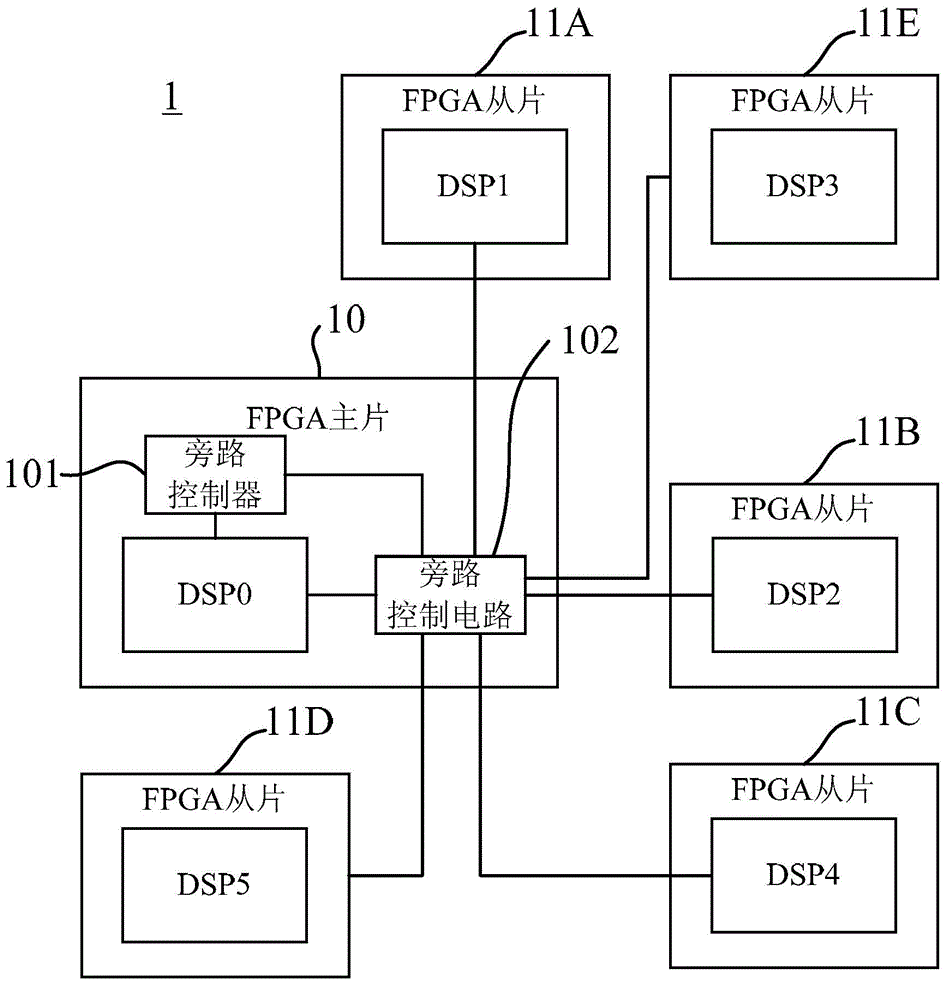

[0044] A FPGA chip 10, such as figure 1 As shown, the FPGA chip 10 is provided with a bypass controller 101 and a bypass control circuit 102 connected to the bypass controller 101;

[0045] In the FPGA system provided with the FPGA chip 10, the bypass control circuit 102 is connected to a plurality of DSPs, wherein each DSP is integrated in its own FPGA chip;

[0046] The bypass control circuit 102 is configured to perform data bypass on multiple DSPs according to a bypa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More