Manufacturing method of low-temperature polycrystalline silicon thin-film transistor array substrate

A thin-film transistor and low-temperature polysilicon technology, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electric solid-state devices, etc., can solve problems such as disadvantages, complicated process steps, and cost reduction, so as to reduce production costs, improve production efficiency, and reduce costs. Effect of using quantity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings. This invention may, however, be embodied in many different forms and should not be construed as limited to the specific embodiments set forth herein. Rather, the embodiments are provided to explain the principles of the invention and its practical application, thereby enabling others skilled in the art to understand the invention for various embodiments and with various modifications as are suited to particular intended uses. In the drawings, the same reference numerals will be used to denote the same elements throughout.

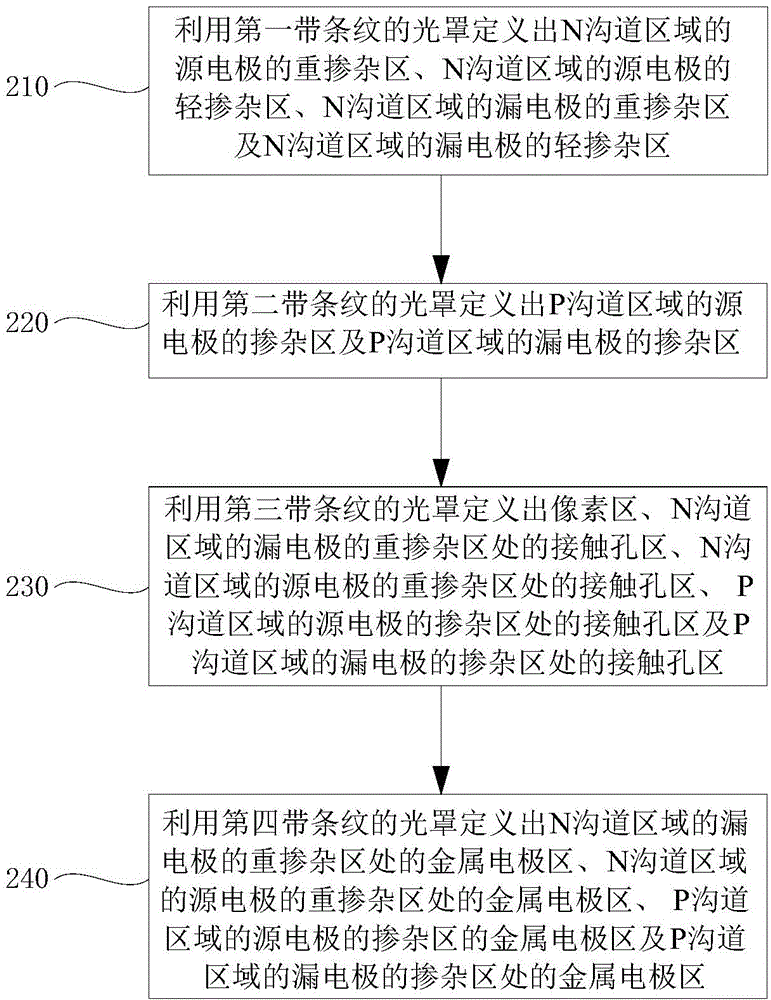

[0019] In the manufacturing method of the low temperature polycrystalline silicon (Lower Temperature Polycrystal Silicon, LTPS) thin film transistor (Thin Film Transistor, TFT) array substrate of the present invention, the LTPS TFT array substrate includes at least N channel region and P channel region, but the present invention ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More