Array substrate, manufacturing method thereof, and display device

An array substrate and active layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of pixel area reduction, storage capacitance reduction, process complexity, etc., to improve storage capacitance, The effect of increasing the storage capacitor and reducing the pixel area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

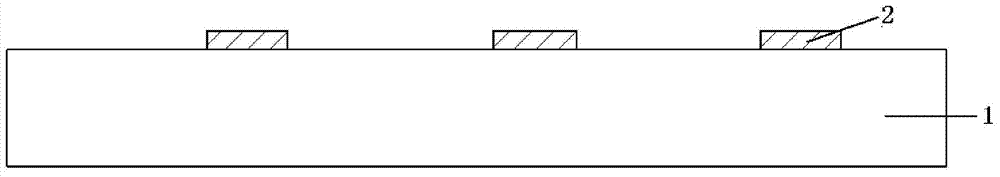

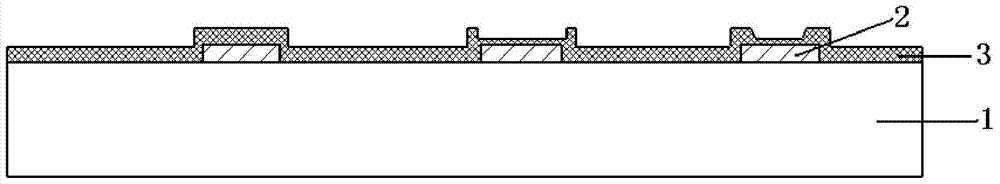

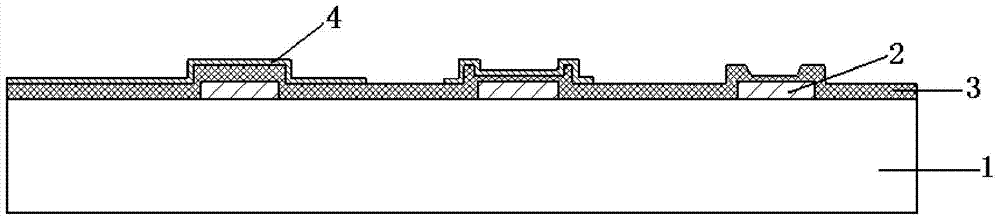

[0077] In order to explain the technical solution of the present invention more clearly, a specific embodiment 1 of the present invention will be described below in conjunction with the schematic cross-sectional view of the device structure formed in each step. In this embodiment, as Figure 8 As shown in the final product structure shown, the array substrate includes a thin film transistor area, a storage capacitor area, and a source and drain contact hole area, that is, the areas corresponding to the three gate electrode layers 2 from left to right in the figure. Of course, the array substrate also Other structures can be included, so I won't repeat them here. It should be understood that the structure shown here is exemplary, and other structural forms may be adopted according to the scope and spirit defined by the claims of the present invention. Such as Picture 9 As shown, the manufacturing method of this embodiment may specifically include the following steps:

[0078] S1:...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More