Transistor and manufacturing method thereof

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of small and complex carrier mobility in the channel region, and achieve the effects of simplified manufacturing process and good compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Although the nanowire field effect transistor in the prior art suppresses the short channel effect, the carrier mobility in the channel region of the transistor in the prior art does not meet the requirements, and the performance of the transistor is not good enough.

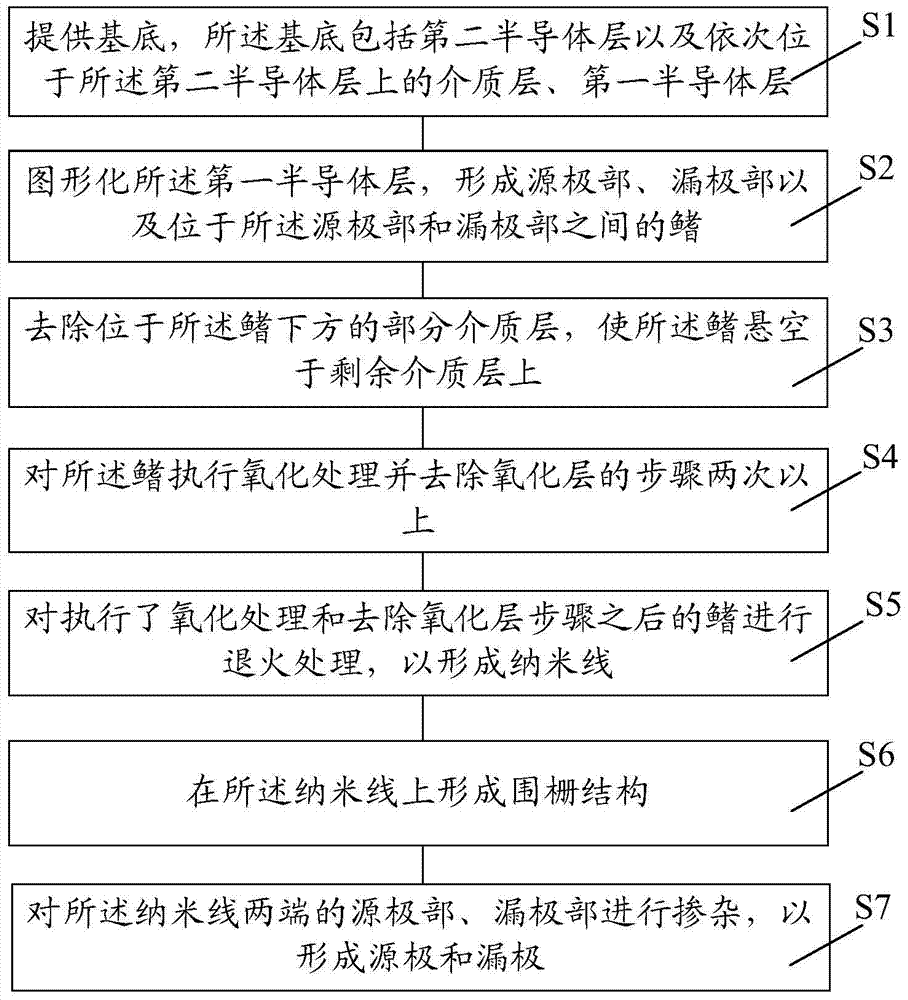

[0018] In order to solve the problems of the prior art, the present invention provides a method for manufacturing a transistor. refer to figure 1 , showing a schematic flow chart of an embodiment of the method for manufacturing a transistor of the present invention. The manufacturing method generally includes the following steps:

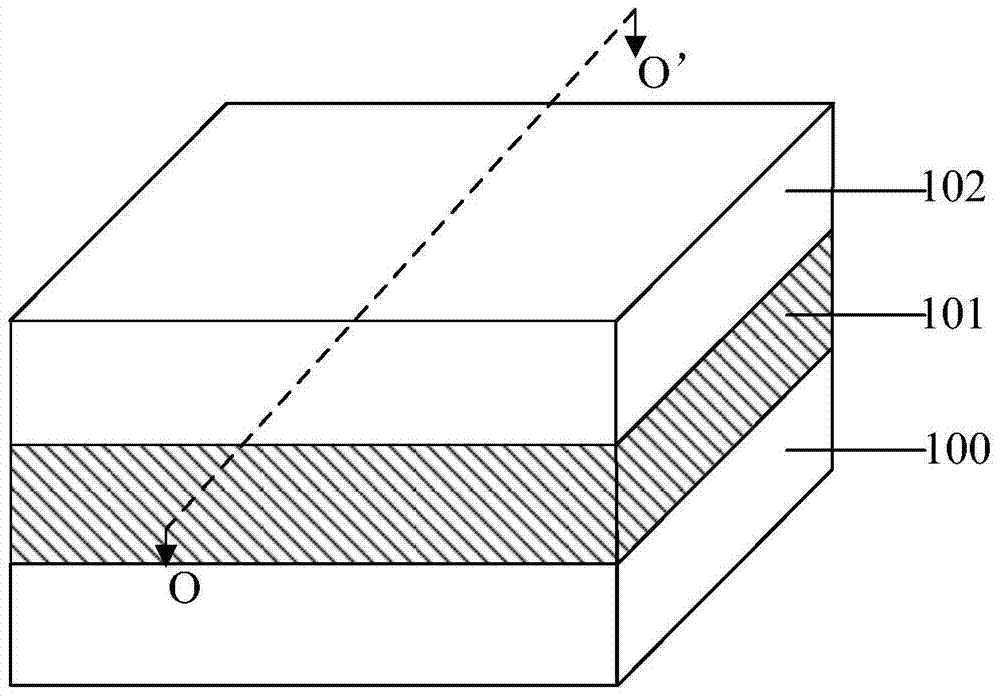

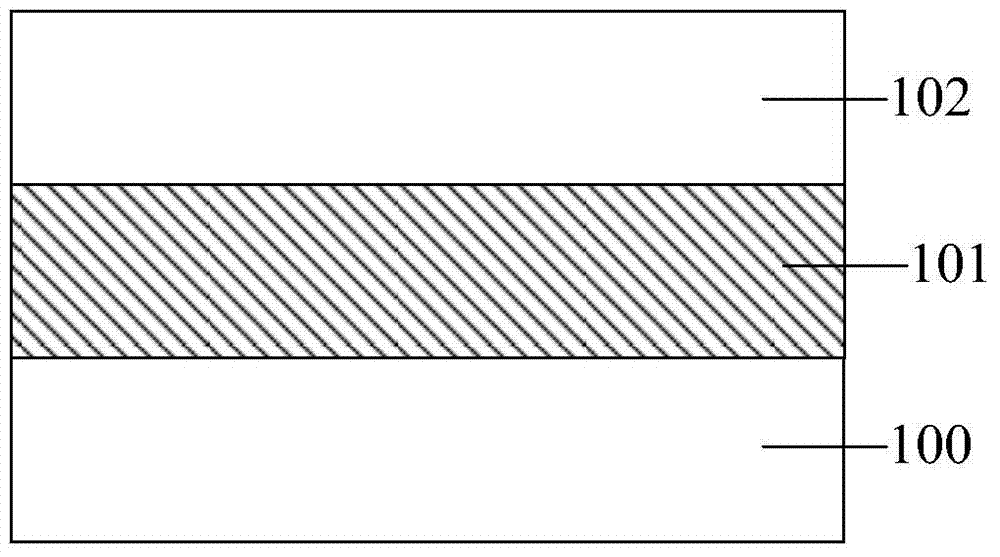

[0019] Step S1, providing a substrate, the substrate comprising a second semiconductor layer, a dielectric layer and a first semiconductor layer sequentially located on the second semiconductor layer;

[0020] Step S2, patterning the first semiconductor layer to form a source portion, a drain portion, and a fin between the source portion and the drain portion;

[0021] Step ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More