Semiconductor structure forming method

A semiconductor and gate structure technology, applied in the field of semiconductor structure formation, can solve problems such as unstable performance of fin field effect transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] As mentioned in the background, the performance of the prior art FinFET is not stable.

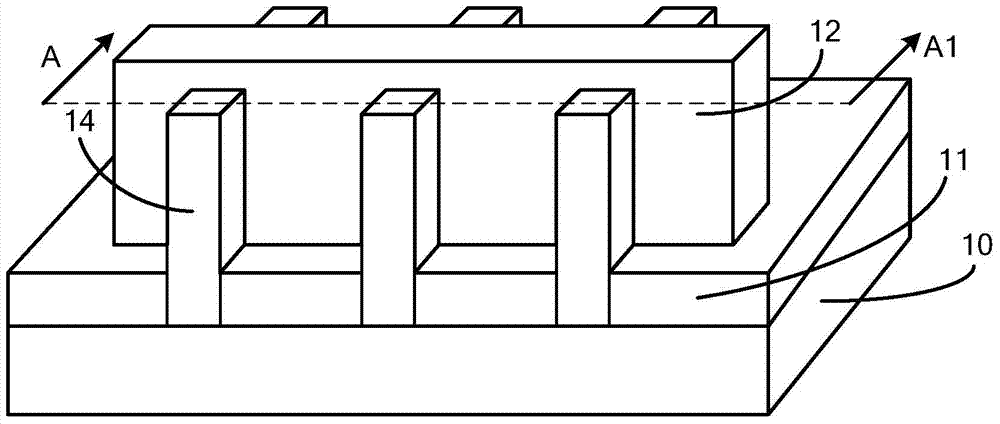

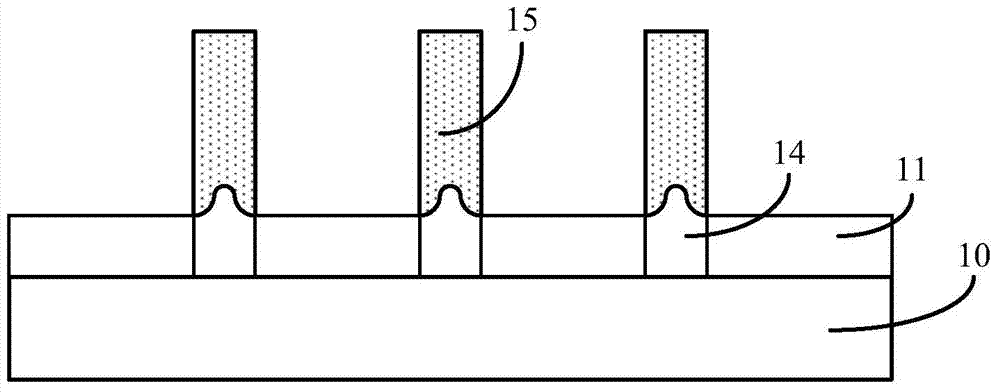

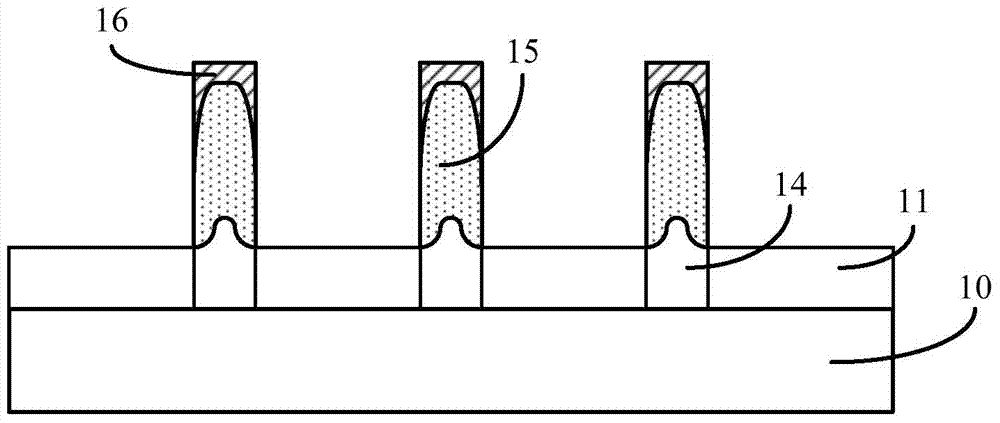

[0039] After research, please continue to refer to figure 2 , figure 2 yes figure 1 Schematic diagram of the cross-sectional structure along the AA1 direction. For a fin field effect transistor, it is necessary to adopt an ion implantation process in the gate structure 12 (such as figure 1 As shown), the fins 14 on both sides are doped with P-type ions or N-type ions to form source regions and drain regions 15, and the top and sidewalls of part of the fins 14 covered by the gate structure 12 need to become Therefore, the ion implantation process needs to dope both the top and the sidewall of the fin 14 , so that both the sidewall and the bottom of the fin 14 can form the source region and the drain region 15 .

[0040] However, since the ion implantation process needs to dope both the sidewall and the top of the fin portion 14, the ion implantation energy received by the fin port...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More