Manufacturing method of groove-type superjunction device

A manufacturing method and super-junction technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as deep and wide, low performance of pitch on-resistance, and poor wafer uniformity, and achieve improved Effects of reverse breakdown voltage, improved in-plane uniformity, reduced width and pitch

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

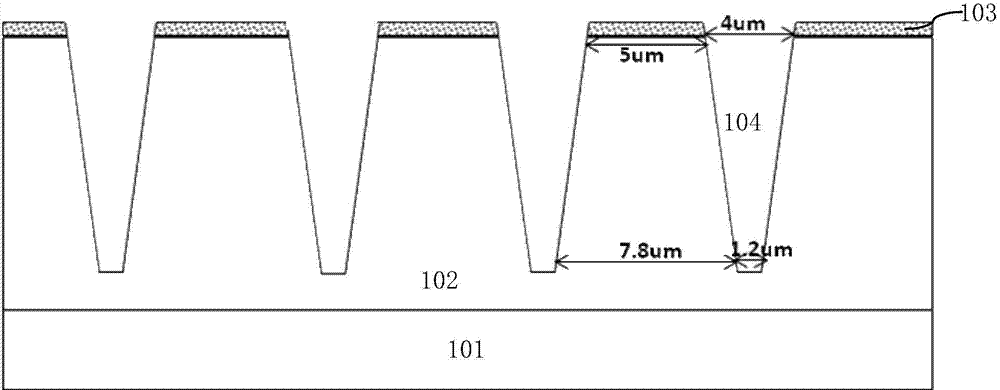

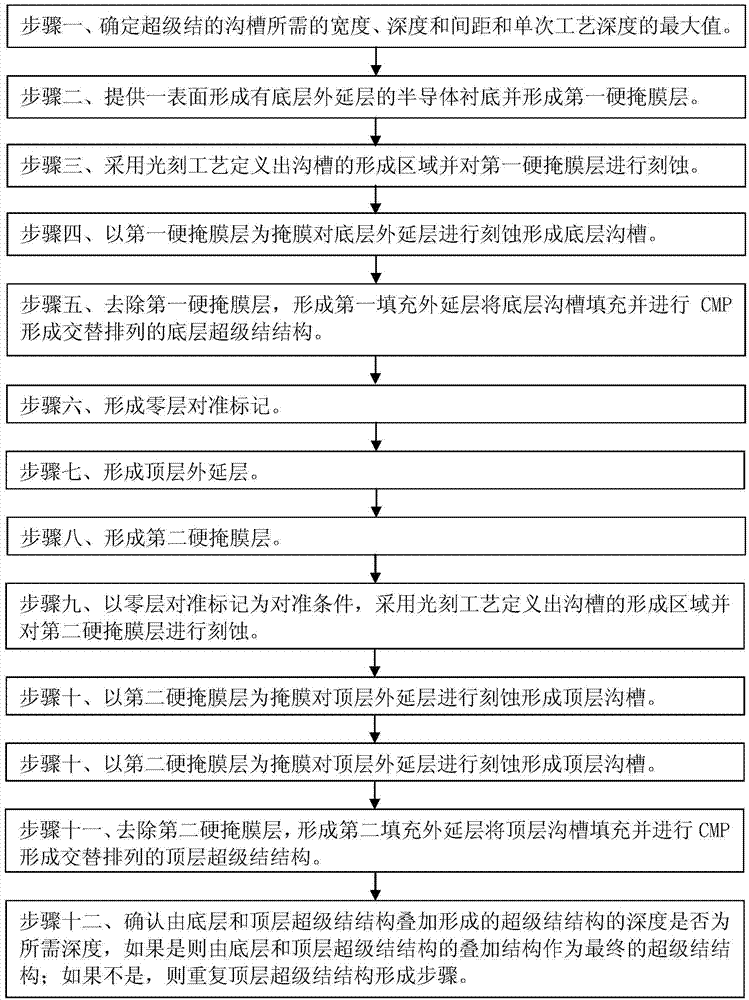

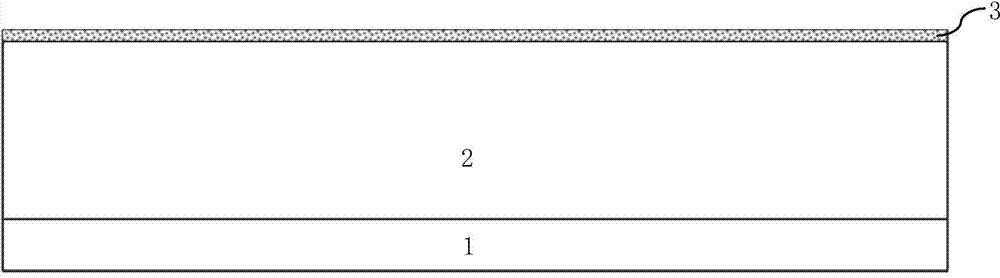

[0042] Such as figure 2 Shown is the flow chart of the method of the embodiment of the present invention; Figure 3A to Figure 3H Shown is a schematic diagram of the device structure in each step of the method of the embodiment of the present invention. The manufacturing method of the trench type super junction device according to the embodiment of the present invention includes the following steps:

[0043] Step 1. Determine the required width, depth and spacing of the grooves of the super junction according to the reverse breakdown voltage and on-resistance requirements of the trench-type super junction device; according to the equipment and process capabilities of the production line and the required The width of the trench determines the maximum value of the single process depth corresponding to the width of the trench required for one photolithography etching and filling process, and the maximum value of the single process depth requires that the The difference between...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More