Programmable static random access memory synchronous clock control module circuit

A technology of synchronous clock and control module, which is applied in the field of SRAM synchronous clock control module circuit, delay chain structure and programmable design, can solve the problems of difficult control, difficulty in SRAM implementation, fixed and immutable timing settings, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

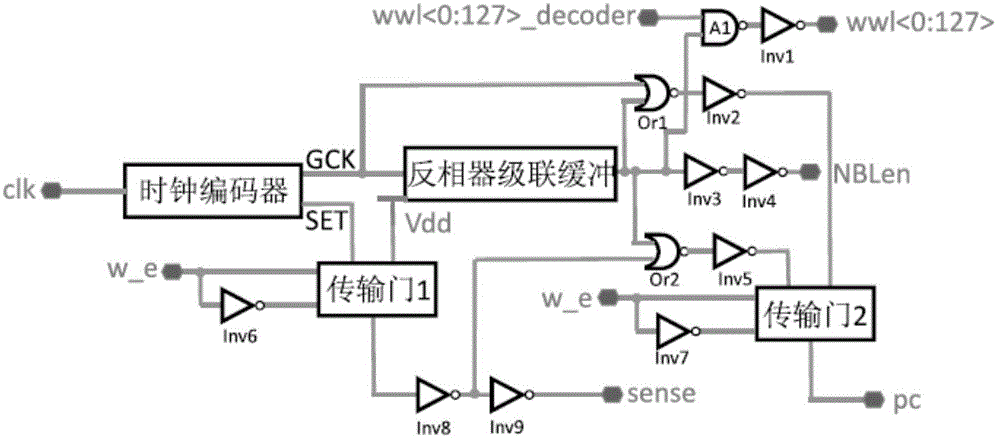

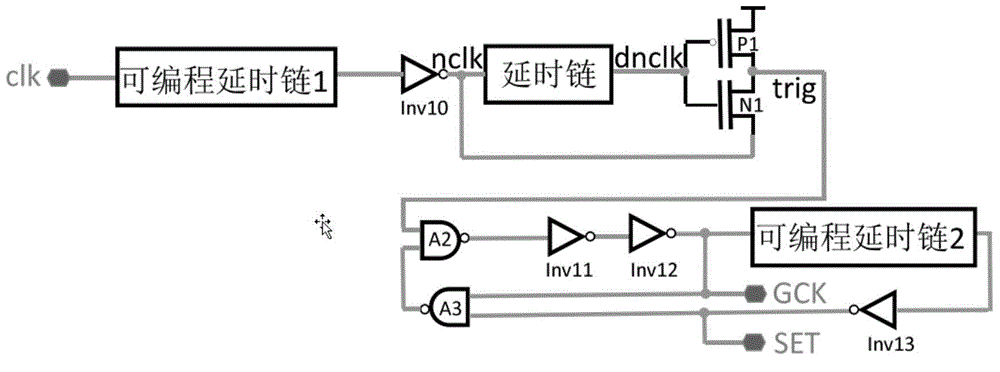

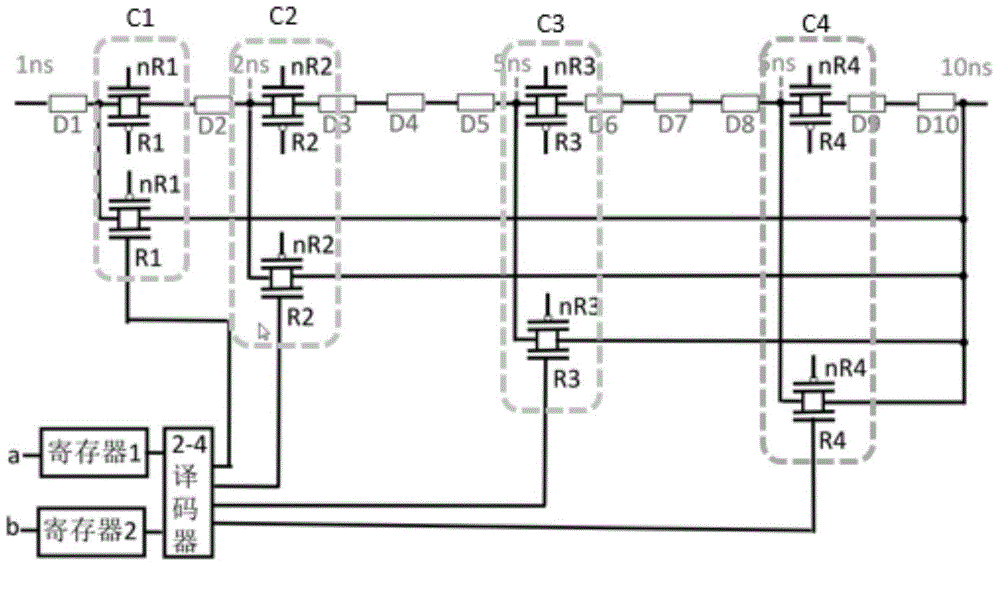

[0017] The present invention is sensitive to the rising edge of the clock. When the clock signal clk arrives, it will automatically generate the required word line strobe signal wwl, the transient negative bit line enable signal NBLen, and the bit line according to the different read and write operations. The line precharge signal pc and the sense amplifier turn on the signal sense. The present invention will be described in detail below in conjunction with the accompanying drawings and the circuit structure of the embodiment.

[0018] The circuit structure of the programmable static random access memory synchronous clock control module of the present invention is as follows: figure 1 As shown, the synchronous clock control module circuit includes 9 inverters Inv1-Inv9 composed of NMOS transistors and PMOS transistors, 1 two-input NAND gate A1, 2 two-input NOR gates Or1-Or2, and 2 transmission gate (the signal at the control terminal is the read-write control signal w_e), an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com