Clock phase control circuit

A technology for controlling circuit and clock phase, applied in the field of clock phase control circuit, can solve the problems of transistor state changing too late, occupying PCB board area, increasing cost, etc., to achieve the effect of reduced clock buffer function, simple circuit principle and easy integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

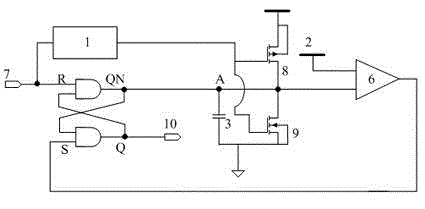

[0012] The specific embodiment of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0013] The clock phase control circuit of the present invention comprises a clock input stage, a capacitor 3, a level detection circuit 6, a pull-up circuit 8, a pull-down circuit 9, a clock output stage and a logic control circuit 1, the output terminal of the clock input stage and the level detection circuit The input terminal of circuit 6 is connected to point A, and point A is also connected to the output terminals of capacitor 3, pull-up circuit 8 and pull-down circuit 9, and the other end of the capacitor is connected to a fixed DC level, preferably grounded; said level detection circuit 6 The voltage at point A is detected, and the detection signal is output to the clock output stage; the logic control circuit 1 is connected with the clock input stage, the pull-up circuit 8 and the pull-down circuit 9, and controls the pull-up...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More