Array substrate and manufacture method thereof and display device

An array substrate and substrate substrate technology, applied in optics, instruments, electrical components, etc., can solve the problems of high production cost and low yield rate, and achieve the effect of improving yield rate, reducing the number of times, and reducing one patterning process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

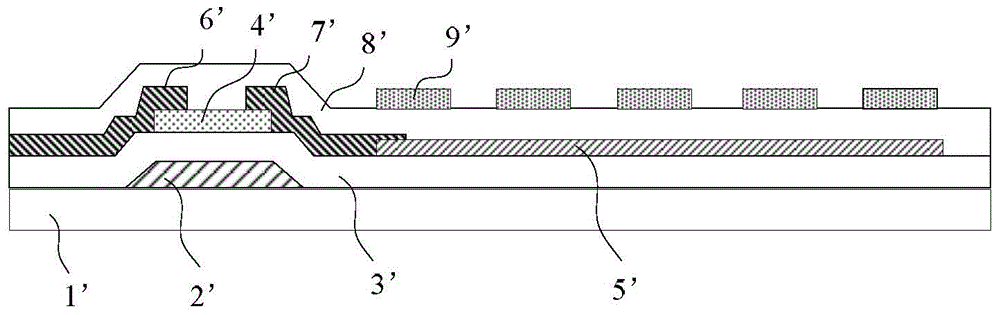

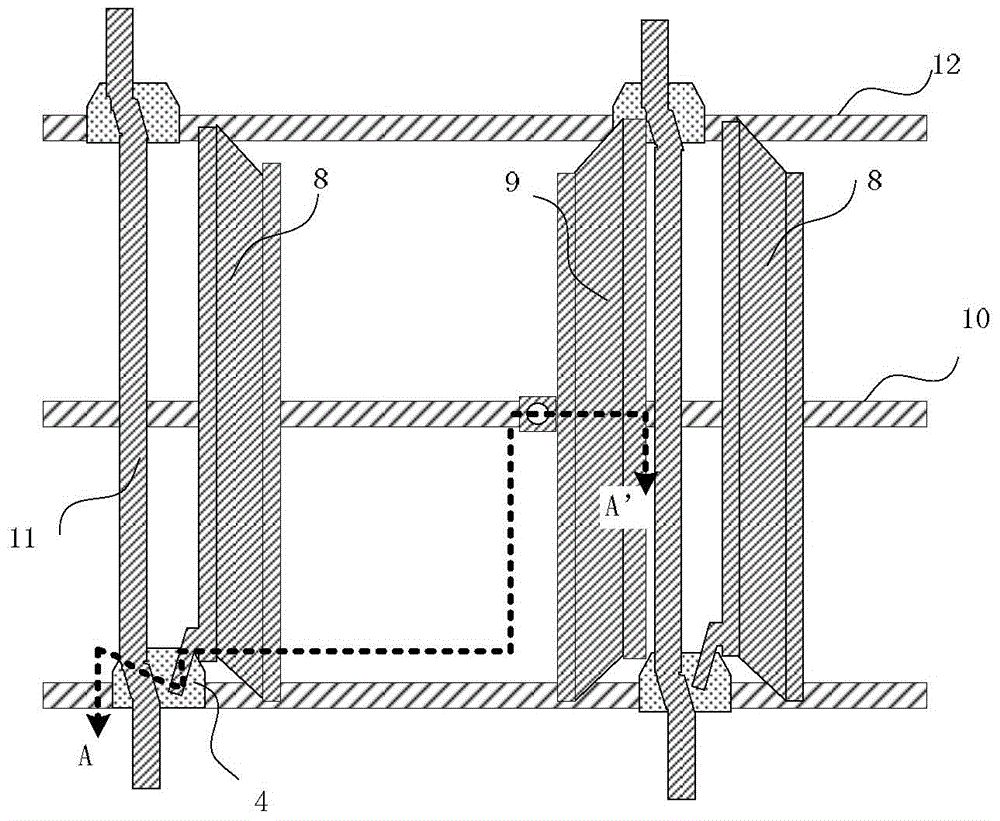

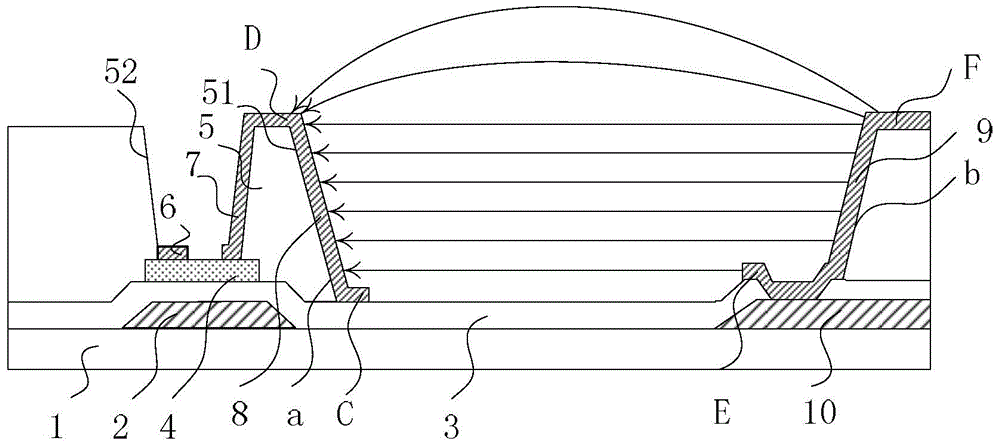

[0032] An embodiment of the present invention provides an array substrate, such as figure 2 and image 3 As shown, the array substrate includes a base substrate 1 and a gate 2 stacked on the base substrate 1, a gate insulating layer 3 and an active layer 4. The array substrate also includes a passivation layer disposed on the active layer 4. The passivation layer 5 and the source electrode 6, the drain electrode 7, the first electrode 8 and the second electrode 9 arranged on the same layer on the passivation layer 5; wherein, the first via hole 51 is arranged on the passivation layer 5, and the second via hole 51 is arranged on the passivation layer 5. A via hole 51 includes two opposite inclined sides; the first electrode 8 at least partially covers one side of the first via hole 51, the second electrode 9 at least partially covers the other side of the first via hole 51, and the second electrode 9 It is electrically connected with the common electrode lead 10; the second v...

Embodiment 2

[0047] An embodiment of the present invention provides a method for manufacturing an array substrate, such as Figure 4 shown, including:

[0048] In step 401, a pattern including a gate is formed on the base substrate through a first patterning process. Exemplarily, a conductive layer is formed on the base substrate by methods such as plasma-enhanced chemical vapor deposition, sputtering or thermal evaporation, a photoresist is coated on the conductive layer, and a mask plate with a grid pattern is used Covering the conductive layer coated with photoresist, after exposure, development, etching and other steps, a pattern including the gate is formed.

[0049] Step 402 , forming a gate insulating layer on the base substrate formed with a pattern including a gate. Exemplarily, the gate insulating layer is formed on the base substrate on which the pattern including the gate is formed by plasma enhanced chemical vapor deposition, sputtering or thermal evaporation.

[0050] In s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com