NAND flash memory error control code structure and error code control method thereof

A technology of error control code and flash memory controller, which is applied in the direction of response error generation and redundant code for error detection, etc. It can solve the problems of hardware complexity increase, short life, high early capacity, etc., and achieve the effect of ensuring long-term stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

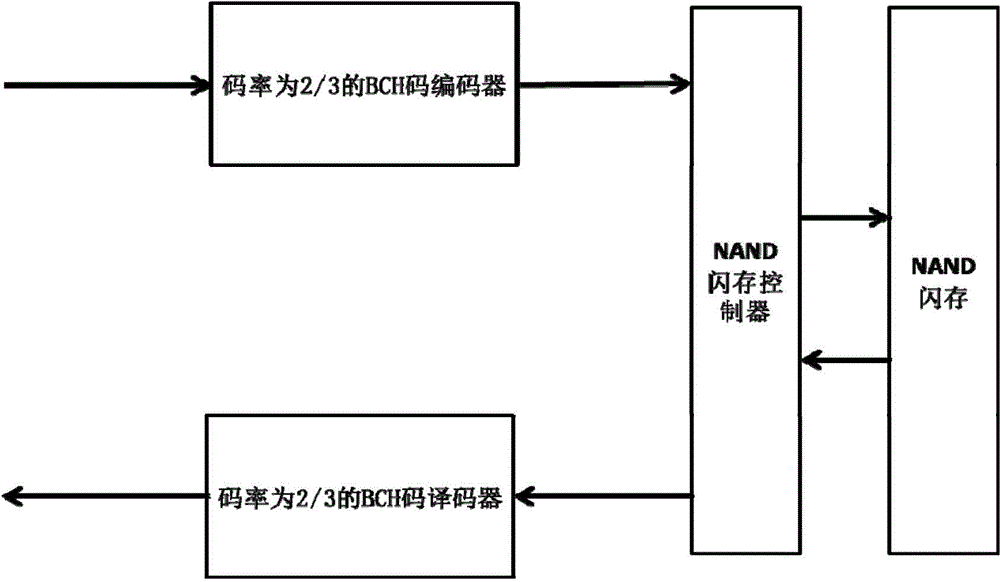

[0026] Such as figure 1 Shown, a kind of error control code structure of NAND flash memory, code length is the BCH code encoder (code length is 65535) of code rate 2 / 3, code length is the BCH code decoder of code rate 2 / 3 (code length 65535) and NAND flash controller. The data output end of the BCH encoder is connected to the data input interface of the NAND flash memory controller, and the data input end of the BCH decoder is connected to the data output interface of the NAND flash memory controller.

[0027] A kind of error code control method of the error control code framework of NAND flash memory, comprises the following steps:

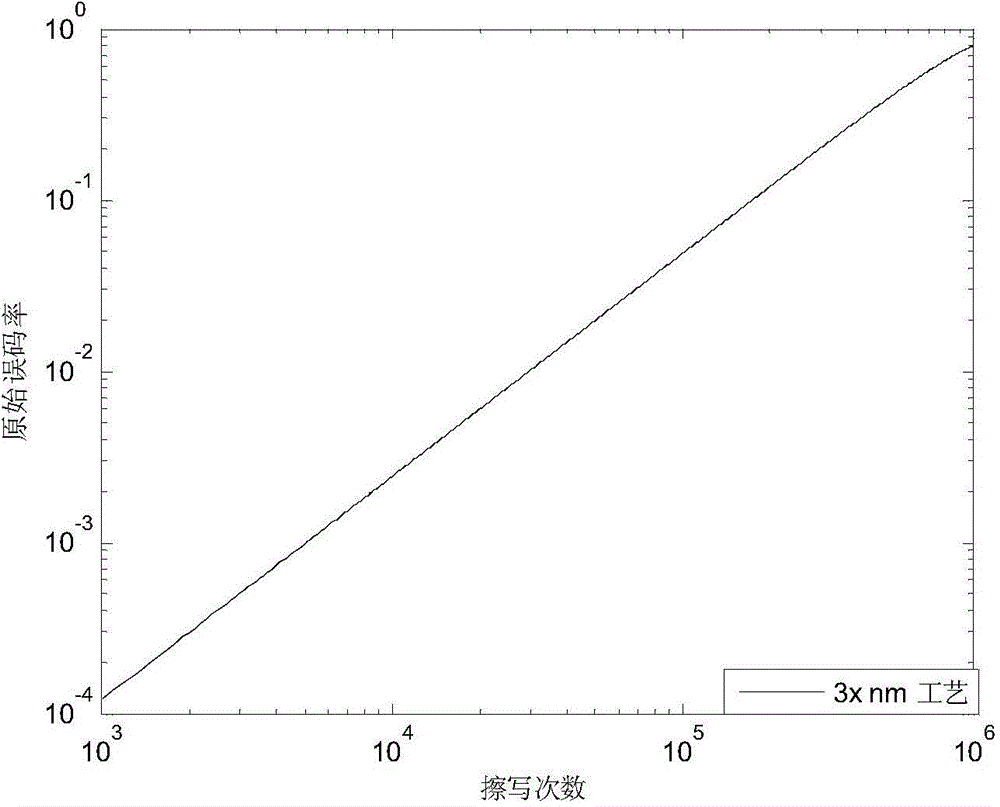

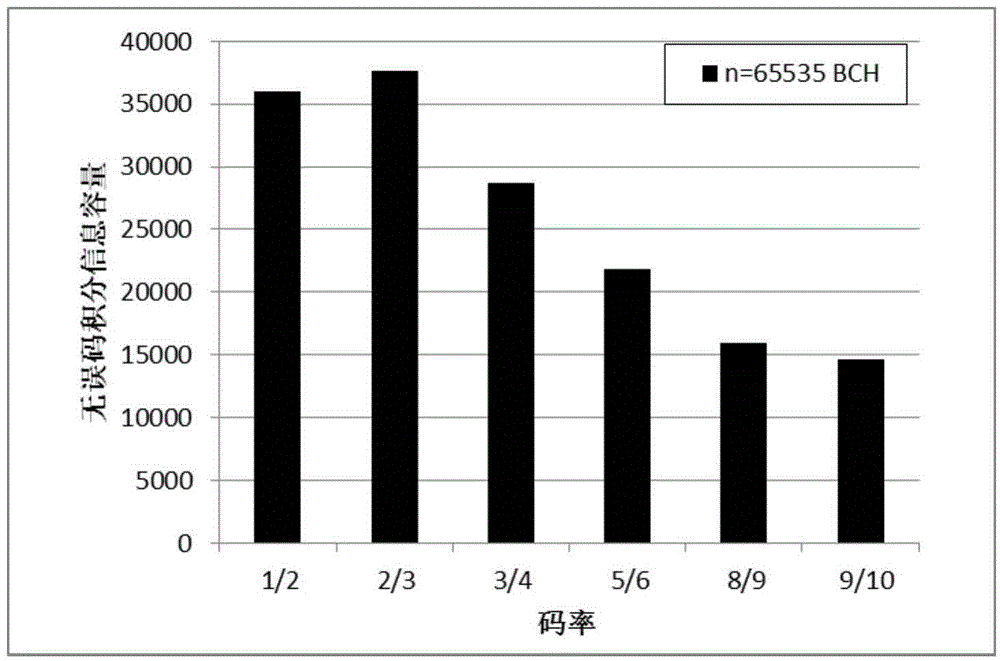

[0028] Step 1: Set the value of the code length N of the BCH code, set the information bit length as k, set the number of error correction bits t of the BCH code, and the code rate R range from 0 to 1. According to the NAND flash memory under different processes, the relationship between the original bit error rate RBER of the flash memory and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More