High-speed low voltage phase frequency detector circuit

A frequency and phase detector, high-speed and low-voltage technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of limiting the maximum working speed of the circuit, limiting the maximum working speed of the PFD, and increasing the static power consumption of the PFD, reaching the fourth state and frequency discrimination and phase discrimination range are optimized, and the dead zone is suppressed and the phase discrimination range is good.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further explained below in conjunction with the accompanying drawings.

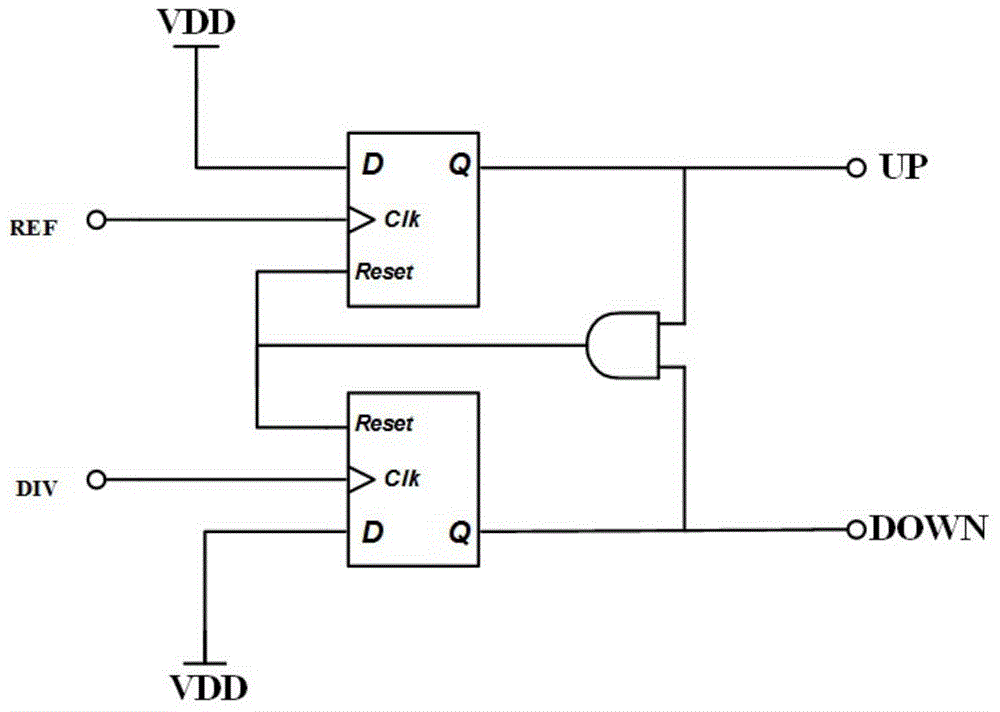

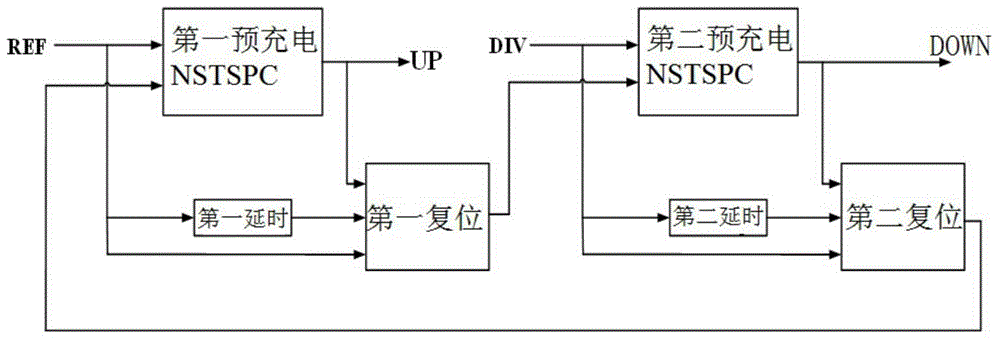

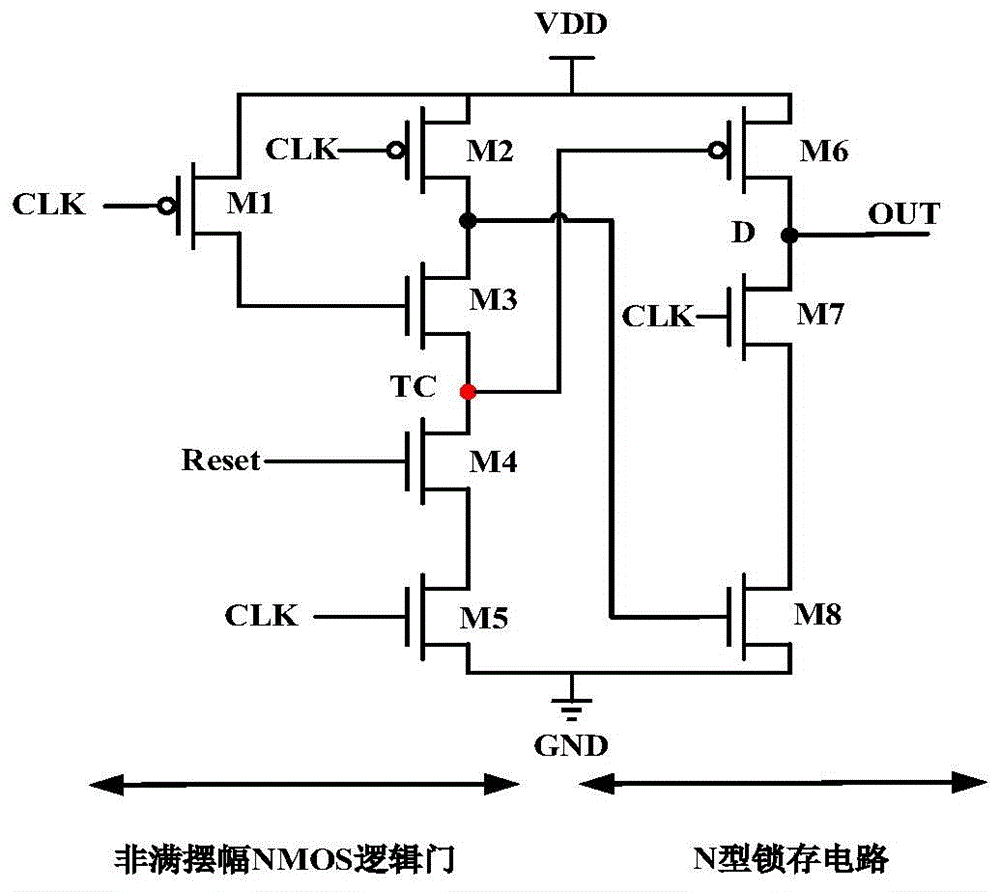

[0017] like figure 2 As shown, a high-speed low-voltage frequency and phase detector circuit includes a first pre-charge NSTSPC circuit, a second pre-charge NSTSPC circuit, a first delay circuit, a second delay circuit, a first reset circuit, and a second reset circuit . The reference signal REF is input to the signal input terminal of the first precharge NSTSPC circuit, the feedback signal DIV is input to the signal input terminal of the second precharge NSTSPC circuit, the first precharge NSTSPC circuit outputs an UP signal, and the second precharge NSTSPC circuit outputs a DOWN signal.

[0018] Wherein, the first delay circuit is used to delay the reference signal REF by τ0 time and input it to the first reset circuit. The first reset circuit is used to perform an AND logic operation on the reference signal REF and the reference signal REF delayed by τ0, and then...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap