Jitter tolerance testing method and circuit for high-speed serial IO interface based on BIST

A jitter tolerance test, high-speed serial technology, applied in the direction of line transmission monitoring/testing, line transmission components, etc., can solve the problems of not being able to simulate the actual situation well, complex jitter components, complex circuit implementation, etc., to achieve Reduce testing costs, reduce dependencies, and achieve simple effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the method and advantages of the present invention more understandable, the BIST-based high-speed serial IO interface jitter tolerance test design scheme provided by the present invention is described in detail below in conjunction with the accompanying drawings, but this does not constitute a limitation of the present invention.

[0030] The present invention is based on the high-speed serial IO interface jitter tolerance test method of BIST, and its implementation steps comprise:

[0031] Phase 1: Build the BIST circuit

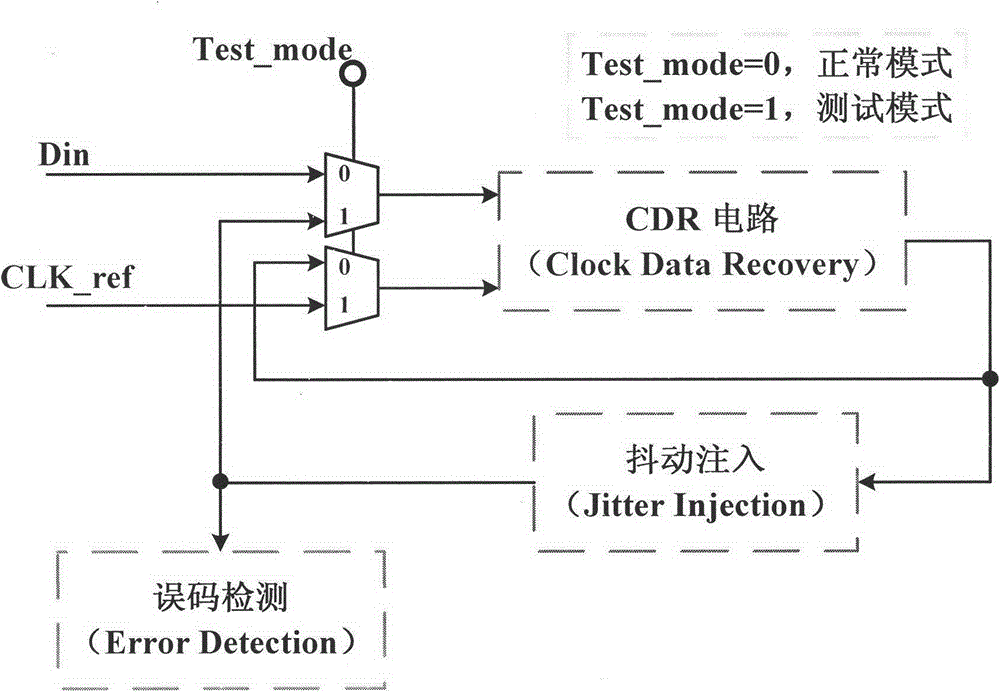

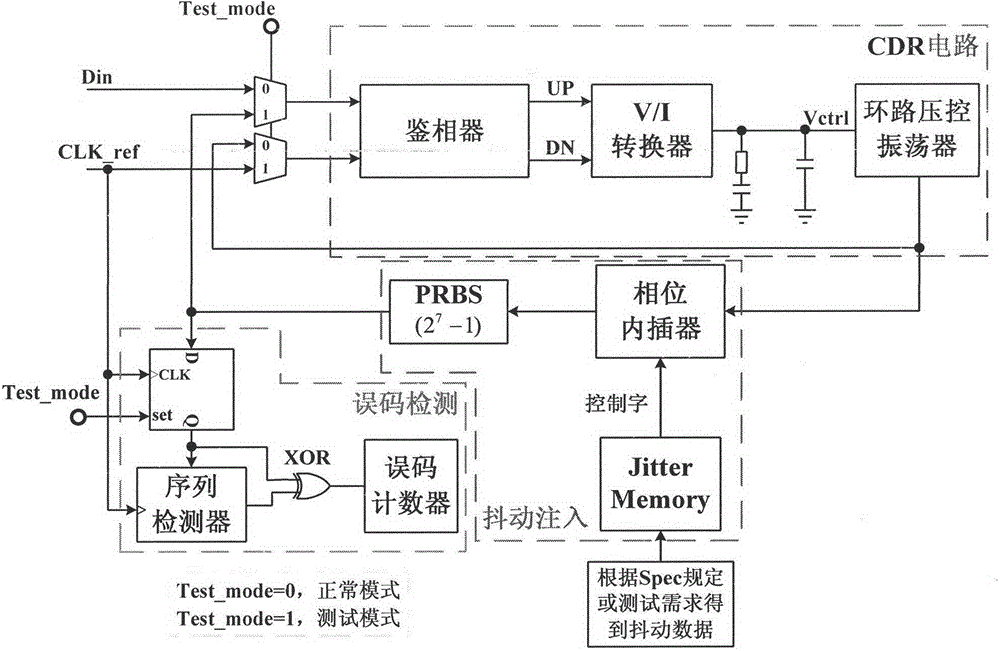

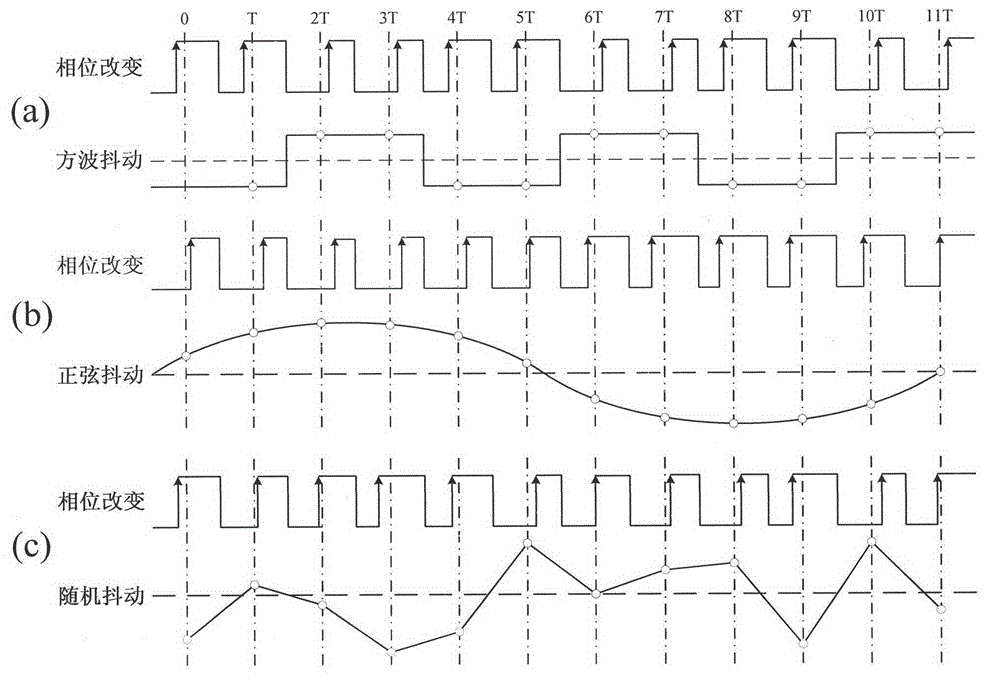

[0032] Step1: After the design of the high-speed serial IO interface circuit is completed, insert the BIST circuit for the jitter tolerance test. Such as figure 1 As shown, the BIST of the present invention includes two parts: jitter injection and bit error detection. Such as figure 2 As shown, the jitter injection module is used to generate a binary sequence containing the jitter information required for testing, including Jitte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More