Circuit and method for multiplexing universal serial bus (USB) and PS/2 interfaces on computer

An interface multiplexing and computer technology, which is applied in the computer field, can solve the problems of increasing the number of host interfaces, increasing the volume of external interfaces, increasing design costs, etc., and achieves the effects of saving machine space, practical methods, and saving design costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

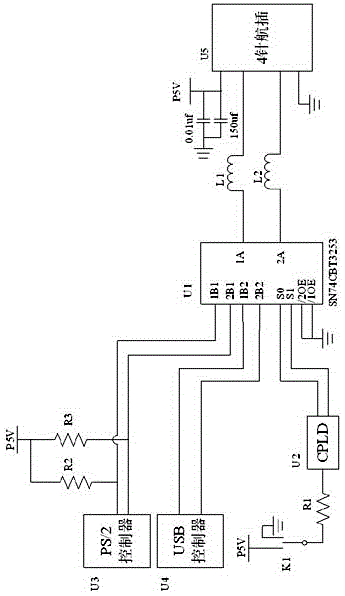

[0019] Such as figure 1 Shown, a kind of circuit of USB, PS / 2 interface multiplexing on the computer, described circuit comprises CPLD control chip U2, two-way switch chip U1, dial switch K1, PS / 2 controller U3, USB controller U4, 4-pin aviation connector U5, where:

[0020] The PS / 2 controller U3 is connected to the input terminals 1B1 and 2B1 of the dual switch chip U1;

[0021] The USB controller U4 is connected to the input terminals 1B2 and 2B2 of the two-way switch chip U1;

[0022] After the dial switch K1 is connected in series with the resistor R1, it is connected to the input terminals S0 and S1 of the dual switch chip U1 through the CPLD control chip U2;

[0023] The output terminals 1A and 2A of the dual-way switch chip U1 are respectively connected in series with the inductors L1 and L2 to the 4-pin aviation plug interface U5;

[0024] The / 2OE and / 1OE of the two-way switch chip U1 are grounded;

[0025] The voltage P5V is connected to the 1B1 terminal of the...

Embodiment 2

[0031] On the basis of Embodiment 1, the model of the two-way switch chip U1 in this embodiment is SN74CBT3253.

Embodiment 3

[0033] On the basis of embodiment 1 or 2, present embodiment a kind of method for USB, PS / 2 interface multiplexing on the computer, described method implementation process is: when dial switch K1 is high level, CPLD controller U2 detects In this state, the control signal is output, so that the S0 and S1 ends of the switch chip U1 are both low level, and the PS / 2 data transmission channel is connected at this time; when the dial switch K1 is low level, the CPLD controller U2 outputs the control signal , so that the S0 terminal of the switch chip U1 is at a high level and the S1 terminal is at a low level, and at this time the USB data transmission channel is connected.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More