Wafer Processing Method

A processing method and wafer technology, which is applied in the manufacture of electrical components, circuits, semiconductors/solid-state devices, etc., can solve the problems of complex process, unfavorable reduction of process time, and reduction of process cost, so as to achieve process simplification, save process cost, and save The effect of process time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] As mentioned in the background art, the existing process for forming the through-silicon via structure is complicated, which is not conducive to reducing process time and process cost.

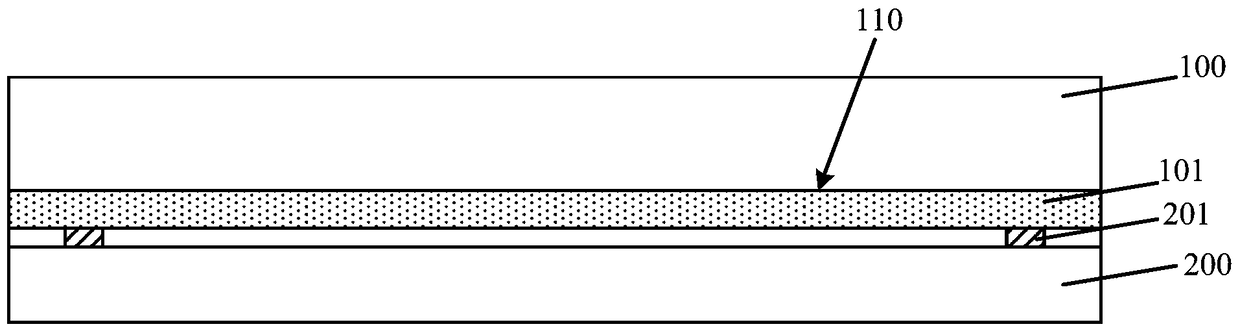

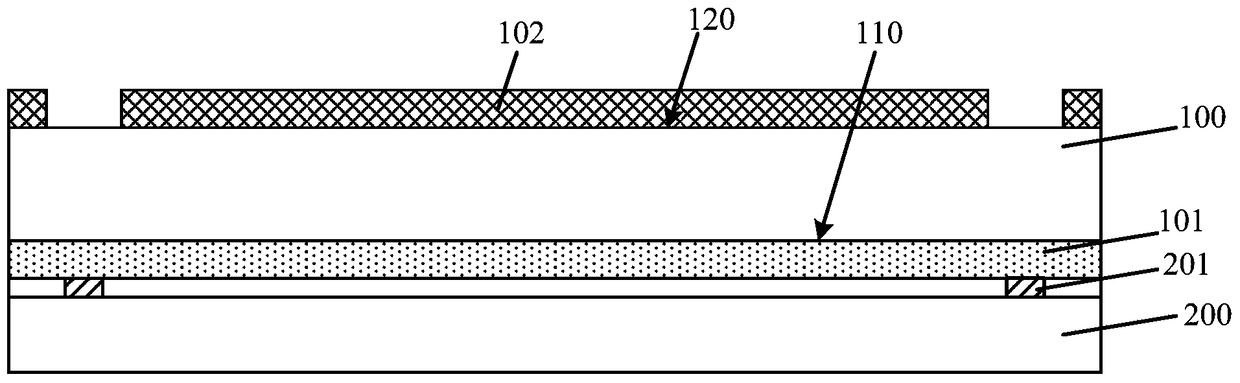

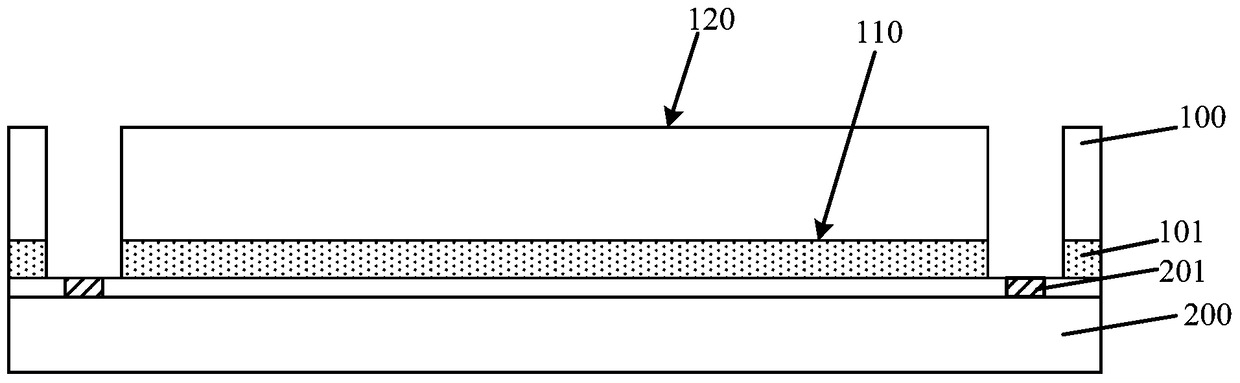

[0033] After research, it is found that after thinning the semiconductor substrate, an etching process needs to be used to etch from the second surface of the semiconductor substrate, so as to form through holes in the semiconductor substrate and the device layer. However, the process of forming the through hole is complicated. like Figure 1 to Figure 4 Shown is a schematic cross-sectional structure diagram of the process of forming a through hole in a semiconductor substrate and a device layer.

[0034] Please refer to figure 1 , provide a semiconductor substrate 100 and a carrier base 200, the first surface 110 of the semiconductor substrate 100 has a device layer 101, the first surface 110 of the semiconductor substrate 100 is bonded to the carrier base 200 through the device laye...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More