Method for forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve the problems of poor nanowire morphology and poor formation performance of fully enclosed gate nanowire transistors, and achieve the effects of performance improvement, process cost reduction, and uniformity improvement.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background art, the nanowires formed in the prior art have poor morphology, which leads to poor formation performance of the gate-all-around nanowire transistors formed.

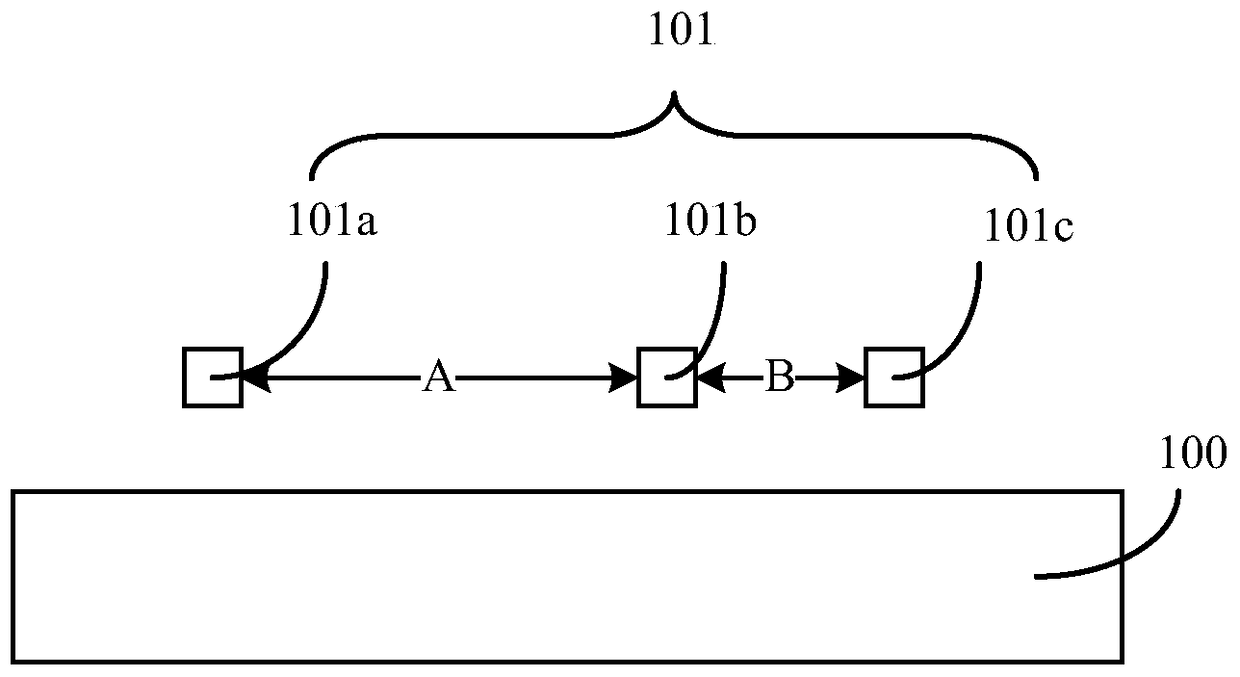

[0034] After research, please refer to figure 1 , figure 1 It is a schematic cross-sectional structure diagram of a nanowire structure embodiment, including: a substrate 100, a number of nanowires 101 suspended above the substrate 100 and arranged in parallel, and the two ends of the nanowires 101 have supports on the surface of the substrate 100 portion, so that the nanowire 100 can be suspended on the substrate 100 . Before forming the gate structure, the nanowire 101 needs to be annealed so that the cross section of the nanowire 101 is circular.

[0035] However, according to the requirements of device design, the spatial distance between each nanowire 101 and surrounding devices is different, for example, the distance A between the nanowire 101a and the nanowire 101b is large...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More