Digital PLL (Phase-Locked Loop) based phase noise measuring device and method

A digital phase-locked loop and phase noise technology, applied in the automatic control of power, electrical components, etc., can solve the problems of affecting the sensitivity of near-end measurement, certain requirements for input power, and no gain adjustment link, etc., to expand the measurement power range , Improve the sensitivity of phase noise measurement, and the effect of good promotion value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

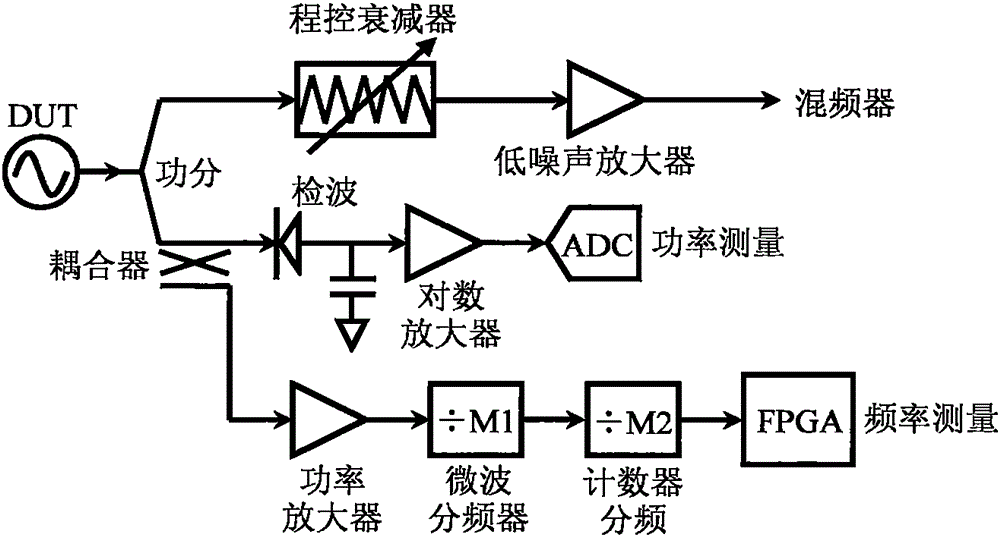

[0092] Such as image 3 As shown, the input signal power of the source under test is divided into two paths: one path is sent to the phase noise measurement part after power adjustment by the program-controlled attenuator, and the other path completes the frequency and power measurement of the source under test. In the frequency power measurement part, the input signal is coupled into two paths by a coupler, and the through signal is sent to AD for acquisition after being subjected to RMS detection, low-pass filtering and logarithmic amplification. The AD measurement voltage and the measured source power approximately satisfy a linear relationship, which can be expressed for:

[0093] P DUT =k×V+P 0

[0094] P DUT Indicates the power of the source under test, P 0 Indicates the compensation value introduced by power division, coupling, etc., k indicates the logarithmic linear coefficient between the detection voltage and power, and the corresponding relationship is determi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More