Chip automatization test system

An automated test and chip technology, applied in the field of microelectronics, can solve problems such as difficult maintenance of programs, poor signal quality, and error-prone programs, and achieve the effects of avoiding poor signal quality, easy maintenance, and saving time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

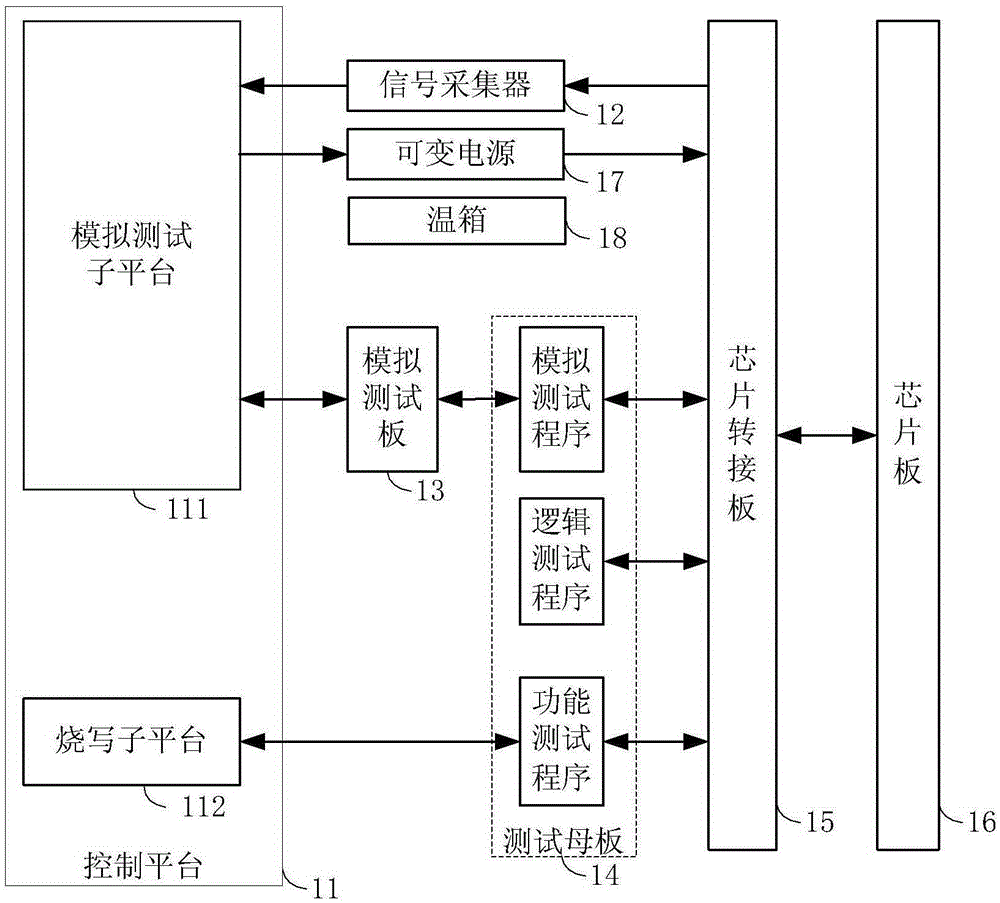

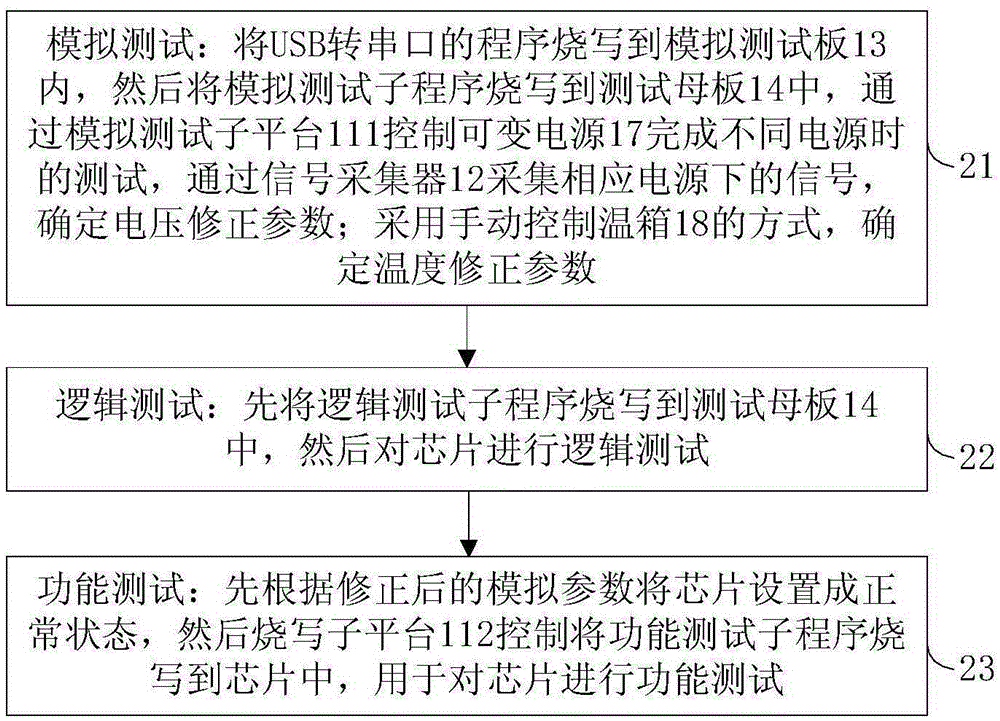

[0041] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

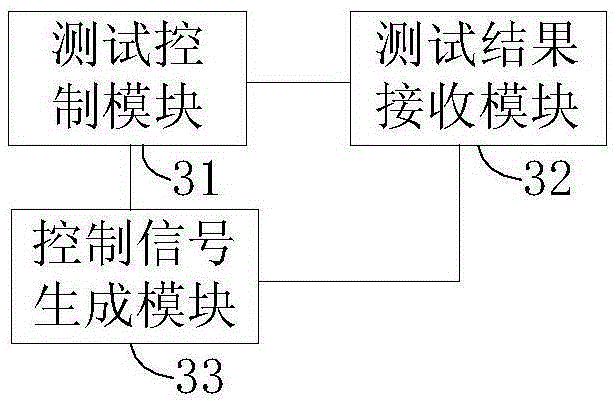

[0042] Such as image 3 Shown is a schematic structural diagram of an embodiment of an automatic test control device for chips according to the present invention. The automatic test control device may include: a test control module 31 and a test result receiving module 32 . Wherein, the test result receiving module 32 is connected with the test control module 31 .

[0043] In this embodiment, the test control module 31 is used to generate a test program selection command, and sends a test program selection command to the automated test board. The test program selection command is used to select a test subroutine from the automated test program. The automated test program includes two The above test subroutines, specifically, can generate an automated test program from different test programs; the test result receiving module 32 is used to rece...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More