Preparation method for vertical III-V family antimonide semiconductor monocrystalline thin film

A III-V, single-crystal thin-film technology, applied in semiconductor/solid-state device manufacturing, nanotechnology for materials and surface science, electrical components, etc., can solve the problem of no buffer layer, increased lattice dislocation, lattice relaxation Incomplete and other problems, to achieve the effect of easy device processing, high crystal quality, and save production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

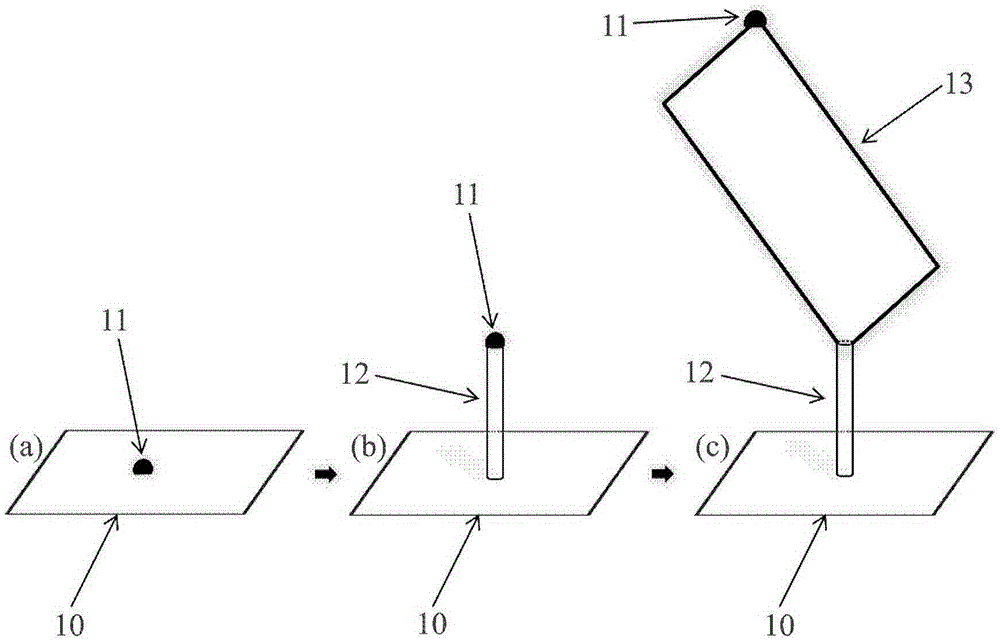

[0013] see figure 1 As shown, the present invention provides a method for preparing a vertical III-V group antimonide semiconductor single crystal thin film, comprising the steps of:

[0014] Step (a): preparing a plurality of metal catalyst particles 11 on the semiconductor substrate 10, the purpose of the metal catalyst particles 11 is to catalyze the growth of the III-V group semiconductor nanowire 12 in the catalytic step (b), and its material is Au, Ag, Cu, Pd, Mn, Ga or Fe, which are obtained by annealing corresponding metal thin films, have a diameter of several nanometers to hundreds of nanometers. The density of the metal catalyst particles 11 determines the density of the III-V semiconductor nanowires 12 in step (b), which can be adjusted by increasing or decreasing the thickness of the metal film or increasing or decreasing the annealing temperature of the metal film. The material of the semiconductor substrate 10 is Si, GaAs, GaSb, InAs, InSb, InP or GaP. The sem...

Embodiment 1

[0017] Embodiment 1: the preparation method of vertical InSb single crystal film

[0018] The invention provides a method for preparing a vertical III-V group antimonide semiconductor single crystal thin film, comprising the following steps:

[0019] Step (a): Using molecular beam epitaxy, deposit an Ag film with a thickness of about 0.5-2 nm on a Si(111) substrate at room temperature; anneal the Ag film at a high temperature (600° C.) for 20 minutes to disperse the film Forming catalyst particles with a diameter of about several nanometers to about 100 nanometers, the catalyst particles are used to catalyze the growth of InAs nanowires in step (b);

[0020] Step (b): Using molecular beam epitaxy, on the Si(111) substrate, using Ag as a catalyst to catalyze and grow InAs nanowires. The InAs nanowire growth temperature is 380°C-530°C, and the As / In beam current ratio is 30-50. The InAs nanowire diameter is about several nanometers to 100 nanometers; different InAs nanowire di...

Embodiment 2

[0022] Example 2: Vertical InAs x Sb 1-x (0<x<1) Preparation method of single crystal thin film

[0023] The invention provides a method for preparing a vertical III-V group antimonide semiconductor single crystal thin film, comprising the following steps:

[0024] Step (a): Using molecular beam epitaxy, deposit an Ag film with a thickness of about 0.5-2 nm on a Si(111) substrate at room temperature; anneal the Ag film at a high temperature (600° C.) for 20 minutes to disperse the film Forming catalyst particles with a diameter of about several nanometers to about 100 nanometers, the catalyst particles are used to catalyze the growth of InAs nanowires in step (b);

[0025]Step (b): Using molecular beam epitaxy, on the Si(111) substrate, using Ag as a catalyst to catalyze and grow InAs nanowires. The InAs nanowire growth temperature is 380°C-530°C, and the As / In beam current ratio is 30-50. The InAs nanowire diameter is about several nanometers to 100 nanometers; different ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More