Chip flip-chip eutectic bonding method with dielectric bridge and products obtained

A eutectic bonding and chip technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problem of uneven force on the contact point between the thimble and the chip, difficulty in precise control of the pressure of the thimble, and difficulty in the position accuracy of the chip. Guarantee and other issues, to achieve the effect of mass assembly, mass assembly, and high-efficiency mass assembly

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

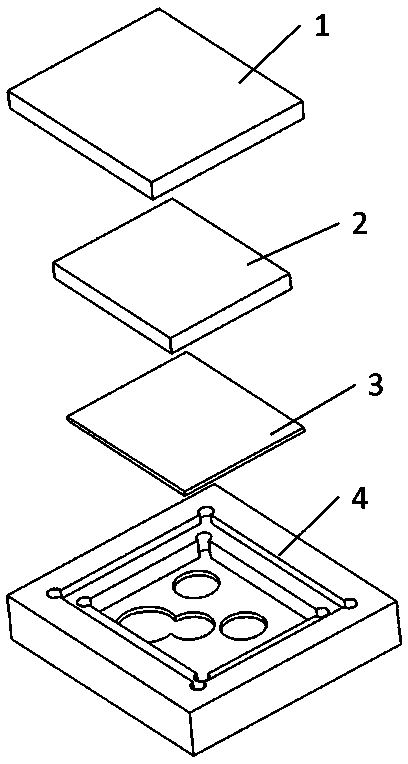

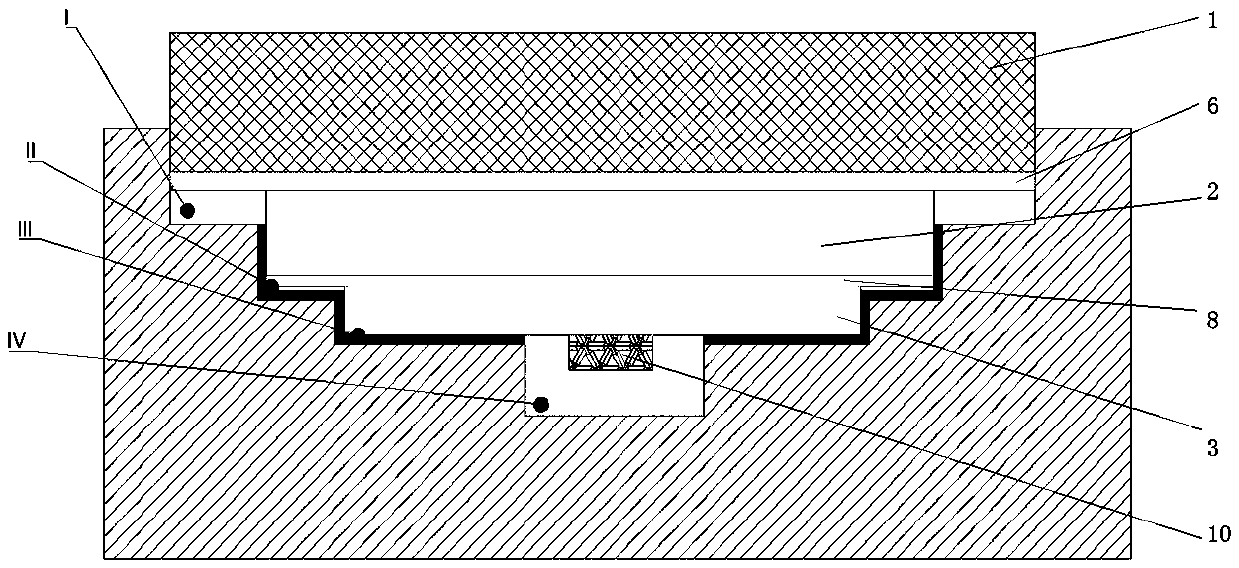

[0094] see figure 1 and figure 2 :

[0095] (1) Base forming

[0096] High-purity graphite is used for precision machining, and four-layer cavities are milled out by CNC machine tools. Cavity I is opened according to the distribution position of the dielectric bridge on the surface of the chip. Cavity II is used for chip placement and positioning. The size of the cavity is consistent with the eutectic position of the chip. The cavity height is 30µm lower than the chip thickness. The size of the surface cavity is the same as that of the substrate, and the height is slightly lower than the thickness of the substrate by 30µm.

[0097] (2) Substrate pretreatment

[0098] The substrate is a high thermal conductivity Mo80Cu20 alloy plate, which is machined into the required 4mm×6mm×0.5mm, the surface is coated with Au / Ni coating, and Au80Sn20 eutectic solder with a thickness of 12.7μm is preset on the surface to be bonded by crimping .

[0099] (3) Briquetting forming

[0100]...

Embodiment 2

[0107] see figure 1 and figure 2 :

[0108] (1) Base forming

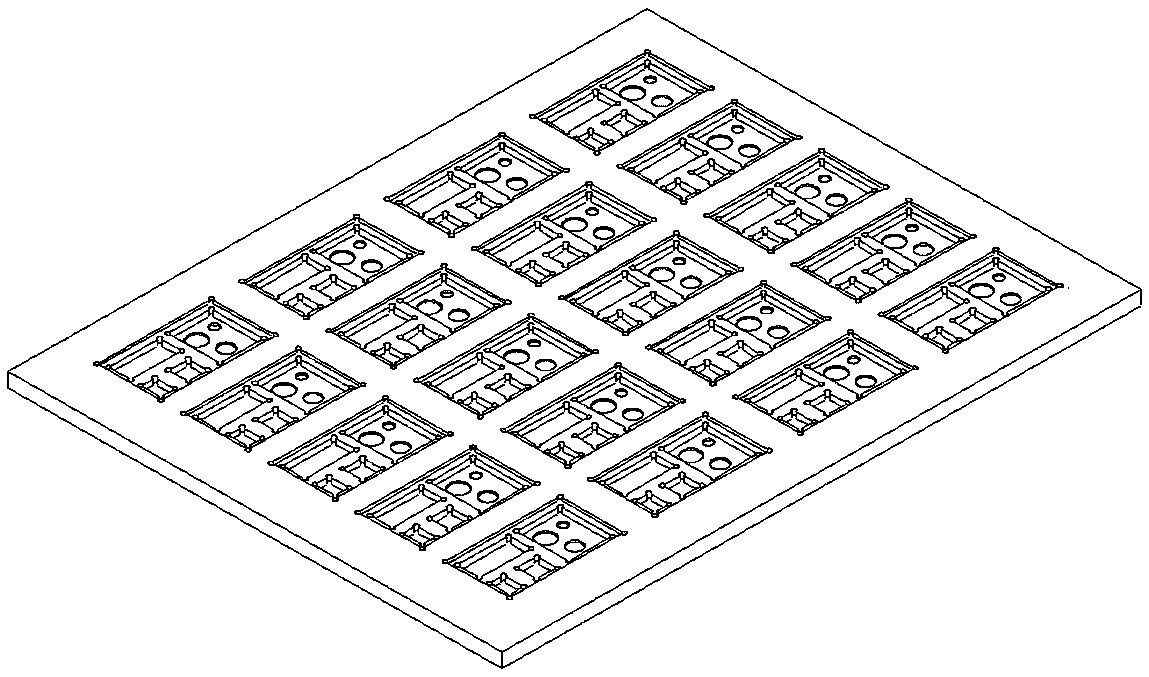

[0109] High-purity graphite is used for precision machining, and four-layer cavities are milled out by CNC machine tools. Cavity I is opened according to the distribution position of the dielectric bridge on the surface of the chip. Cavity II is used for chip placement and positioning. The size of the cavity is consistent with the eutectic position of the chip. The cavity height is 30µm lower than the chip thickness. The size of the surface cavity is consistent with the size of the substrate, and the height is slightly lower than the thickness of the substrate by 30µm. The specific structure is as follows image 3 shown.

[0110] (2) Substrate pretreatment

[0111] The substrate is a high thermal conductivity W85Cu15 alloy plate, which is machined into the required 10mm×6mm×2mm, the surface is plated with Au / Ni coating, and Pb37Sn63 eutectic solder with a thickness of 0.06mm is preset on the surface to be bon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More