Elimination method of clock jitter in radio frequency direct band pass sampling digital receiving system

A digital receiving system and band-pass sampling technology, which is applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of low computational complexity and high computational complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment example 1

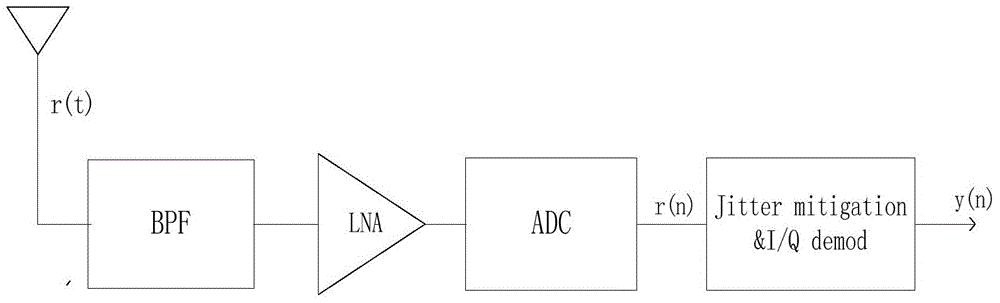

[0033] Implementation case 1: RF direct band-pass sampling digital receiving system built with MATLAB ( figure 1 As shown) the simulation environment for clock jitter compensation is taken as an example (in the experiment, the LTE uplink signal is used as the receiving signal of the digital receiving system, the carrier frequency is 2.6GHz, the sampling rate is 245.76MHz, and the SNR is 18dB).

[0034] (a) The baseband signal obtained by the radio frequency direct band-pass sampling digital receiving system after band-pass sampling and digital down-conversion is calculated according to formulas (8), (9), wherein, m=3, fc=2.6GHz

[0035] (b) Calculate the uniformly sampled baseband signal s(nT after jitter removal) according to formula (6) s );

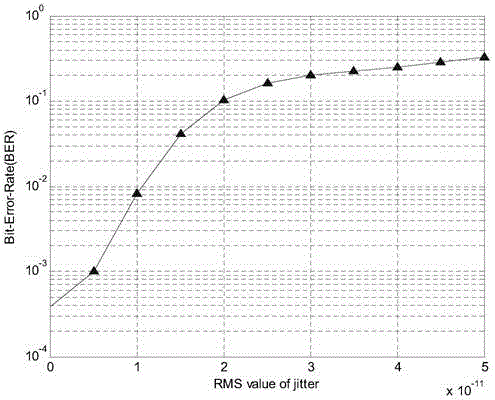

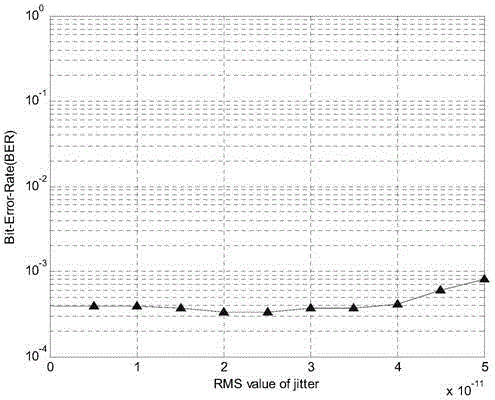

[0036] The compensated system BER (bit error rate) curve is as follows image 3 As shown, compared with the BER (bit error rate) curve of the system without clock jitter compensation ( figure 2 As shown), the BER (bit error rate) p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More