Array substrate, manufacturing method thereof, and display device

A technology of array substrates and conductive structures, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems that display devices cannot display images normally, and achieve the effect of improving the display images that cannot be displayed normally

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

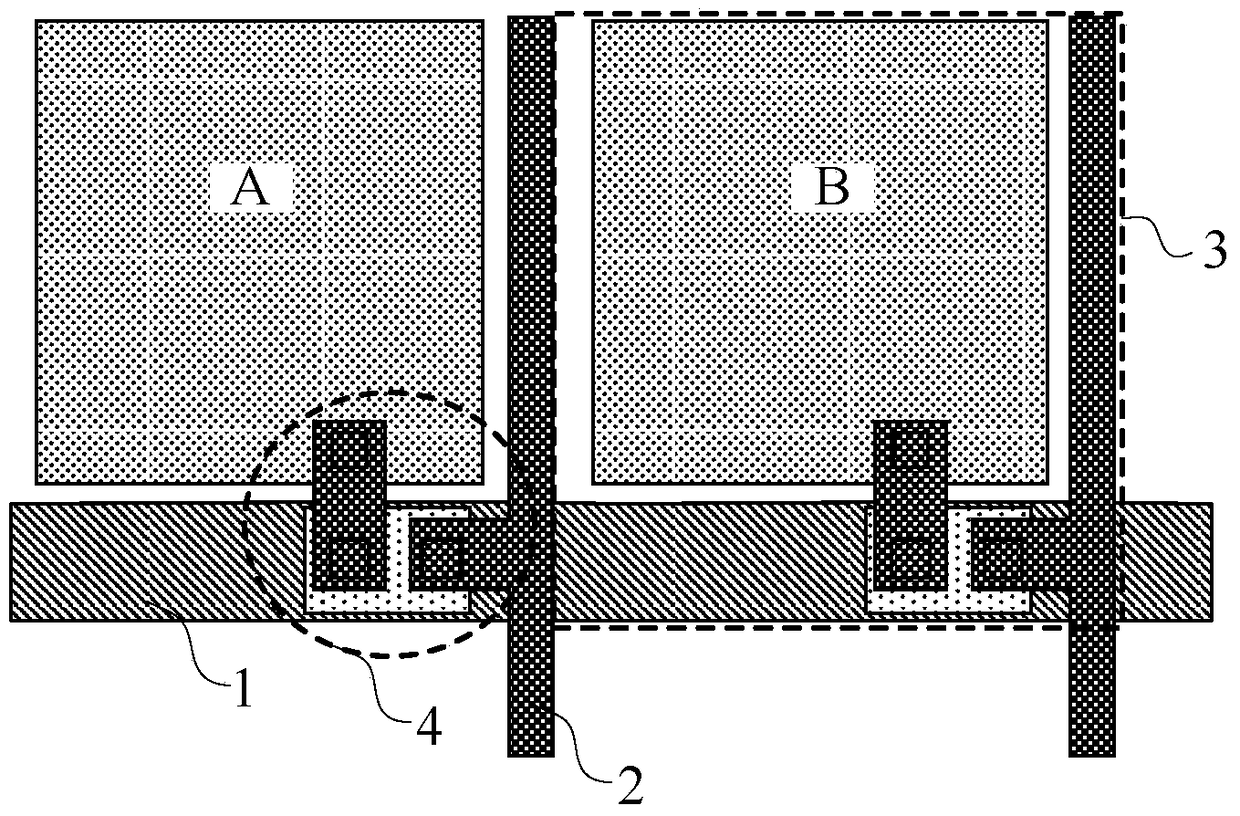

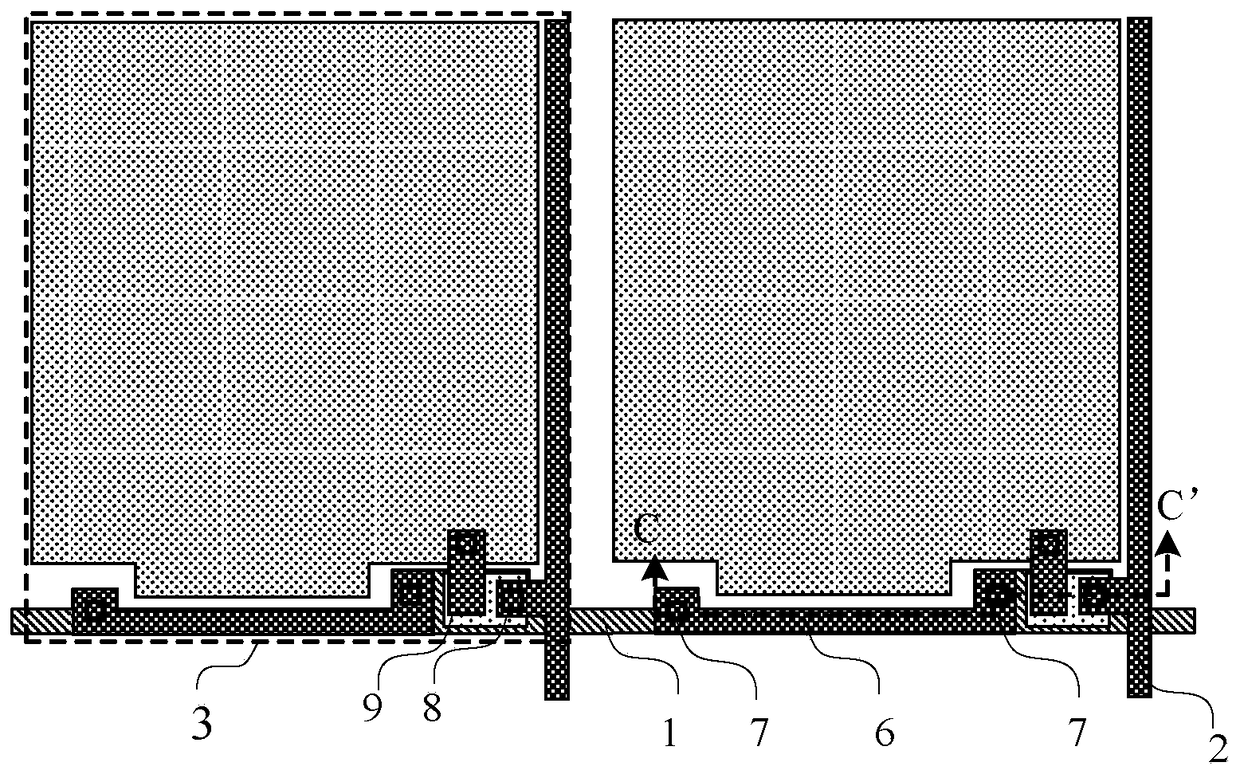

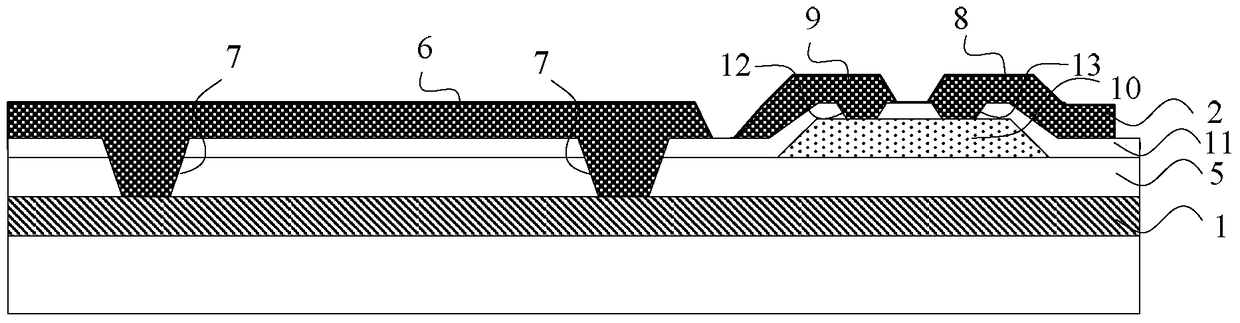

[0034] An embodiment of the present invention provides an array substrate, such as figure 2 and image 3 As shown, the array substrate includes a plurality of gate lines 1 parallel to each other, an insulating layer 5 located on the film layer where the plurality of gate lines 1 are located, and at least one first conductive structure 6 located on the insulating layer 5. The insulating layer 5 At least two first via holes 7 corresponding to the first conductive structure 6 are arranged on it, and the first conductive structure 6 is electrically connected to the gate line 1 through the first via holes 7 .

[0035] When the array substrate is in operation, since the first conductive structure 6 is electrically connected to the gate line 1 through at least two first via holes 7, the first conductive structure 6 is connected in parallel to the gate line 1, which is equivalent to connecting a resistor in parallel to the gate line 1. Therefore, the resistance value of the grid lin...

Embodiment 2

[0054] An embodiment of the present invention provides a method for manufacturing an array substrate, such as Figure 9 As shown, the method includes:

[0055]S901, forming a gate metal layer, and forming a pattern including a gate line through a patterning process. Exemplarily, a gate metal layer is formed by methods such as plasma-enhanced chemical vapor deposition, sputtering, or thermal evaporation, and a photoresist is coated on the gate metal layer. The gate metal layer of the photoresist forms a pattern including gate lines after exposure, development, etching and other steps.

[0056] S902, forming an insulating layer on the film layer where the gate line is located, and forming at least two first via holes corresponding to the first conductive structure on the insulating layer through a patterning process. Exemplarily, by plasma-enhanced chemical vapor deposition, sputtering or thermal evaporation and other methods, an insulating layer is formed on the film layer wh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More