RC triggered ESD protection circuit for integrated circuit

An ESD protection, integrated circuit technology, applied in the electronic field, can solve the problems of large resistance and capacitance, RC trigger ESD protection circuit occupying a large chip area and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

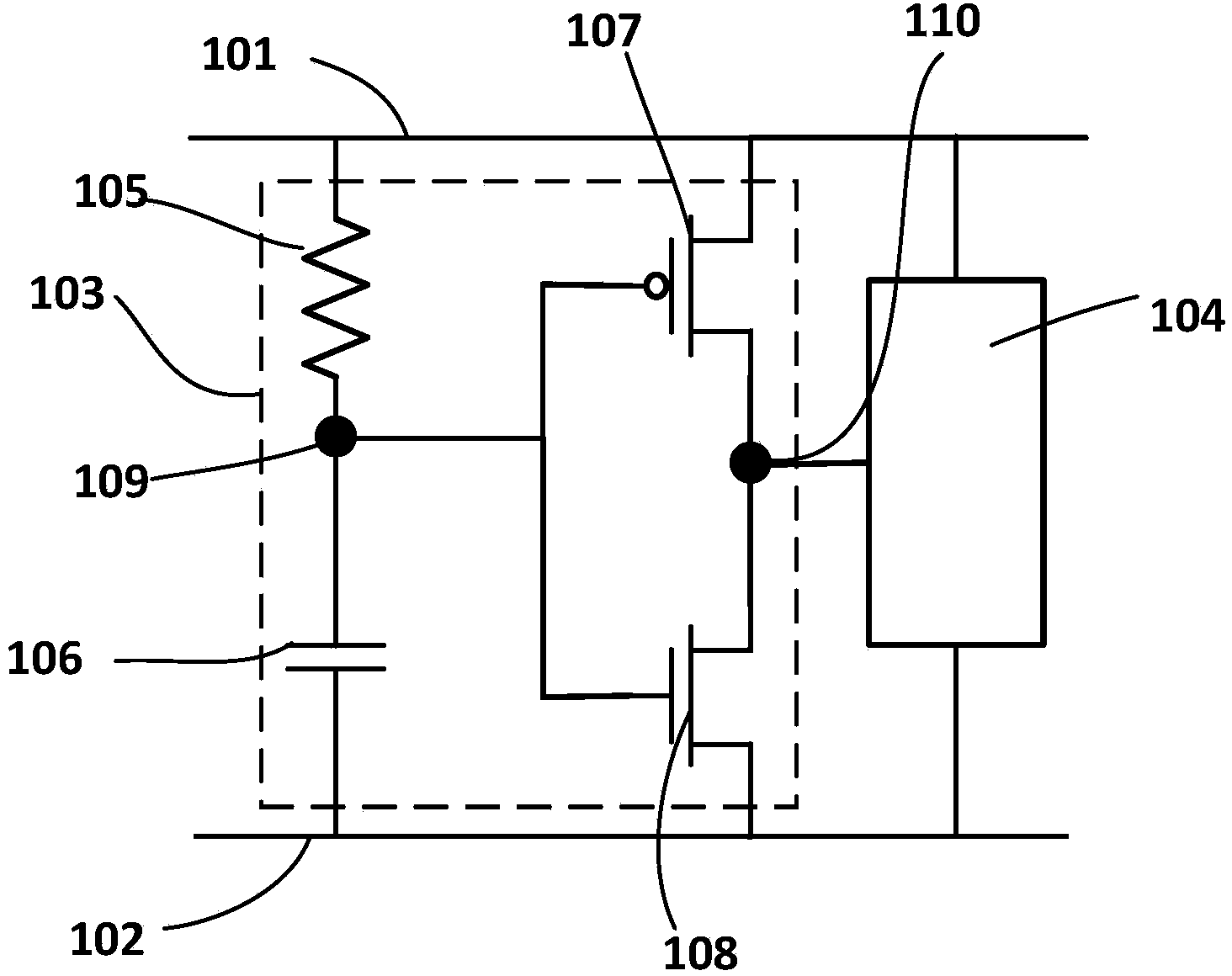

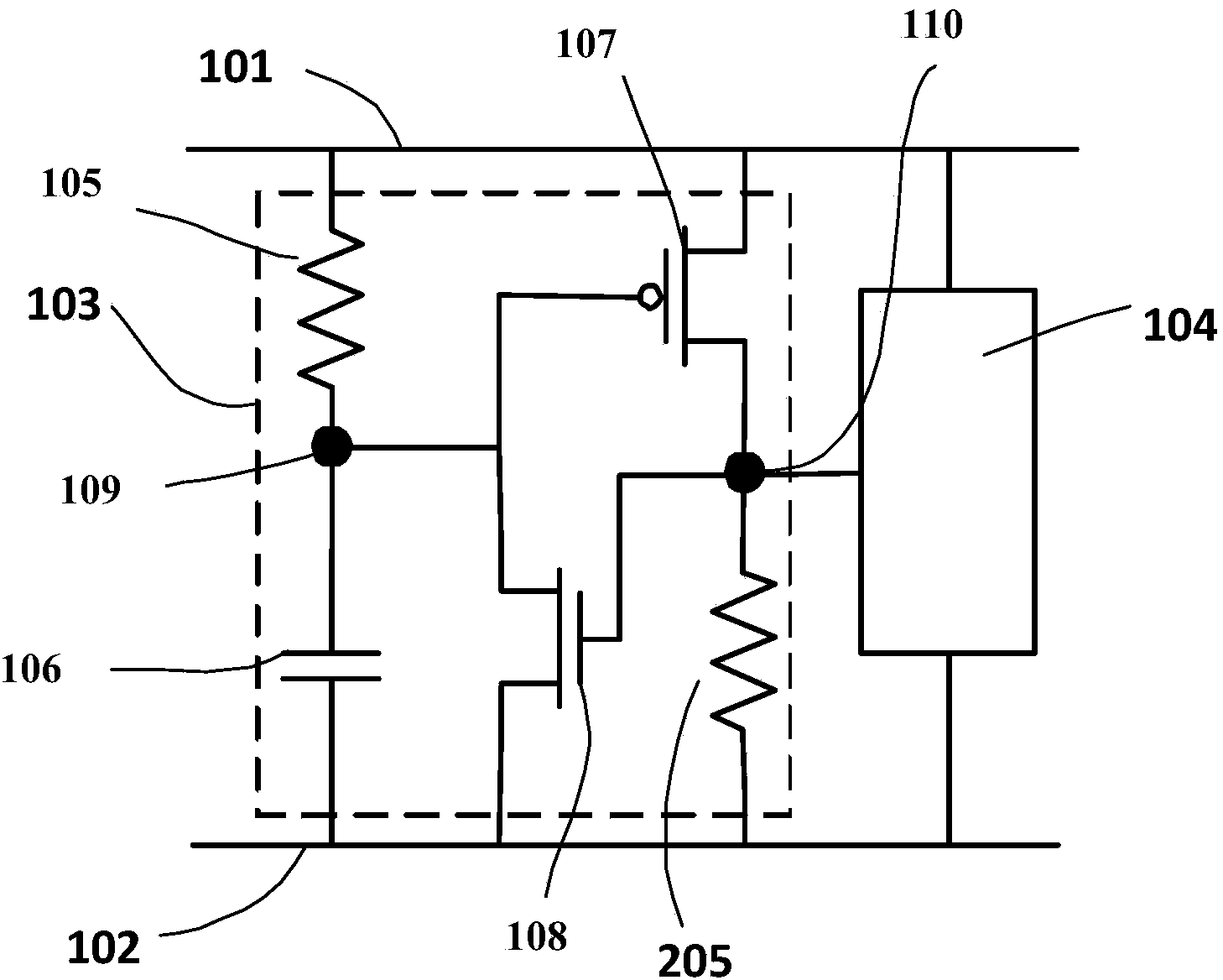

Embodiment 1

[0020] An RC trigger ESD protection circuit for integrated circuits such as figure 2 As shown, it includes: RC trigger circuit 103 and ESD clamping device 104 . The trigger circuit 103 includes two resistors 105 and 205 , a capacitor 106 , a PMOS transistor 107 and an NMOS transistor 108 . After the first resistor 105 and capacitor 106 are connected in series, the resistor is connected to the VDD power supply line 101, and the capacitor is connected to the VSS power supply line 102; the connection point 109 between the first resistor 105 and the capacitor 106 is connected to the gate of the PMOS transistor 107 and the gate of the NMOS transistor 108. Drain, the source of the PMOS transistor 107 is connected to the VDD power supply line 101, the source of the NMOS transistor 108 is connected to the VSS power supply line 102, and the drain of the PMOS transistor 107 and the gate of the NMOS transistor 108 are connected to each other at the connection point 110 connected to the ...

Embodiment 2

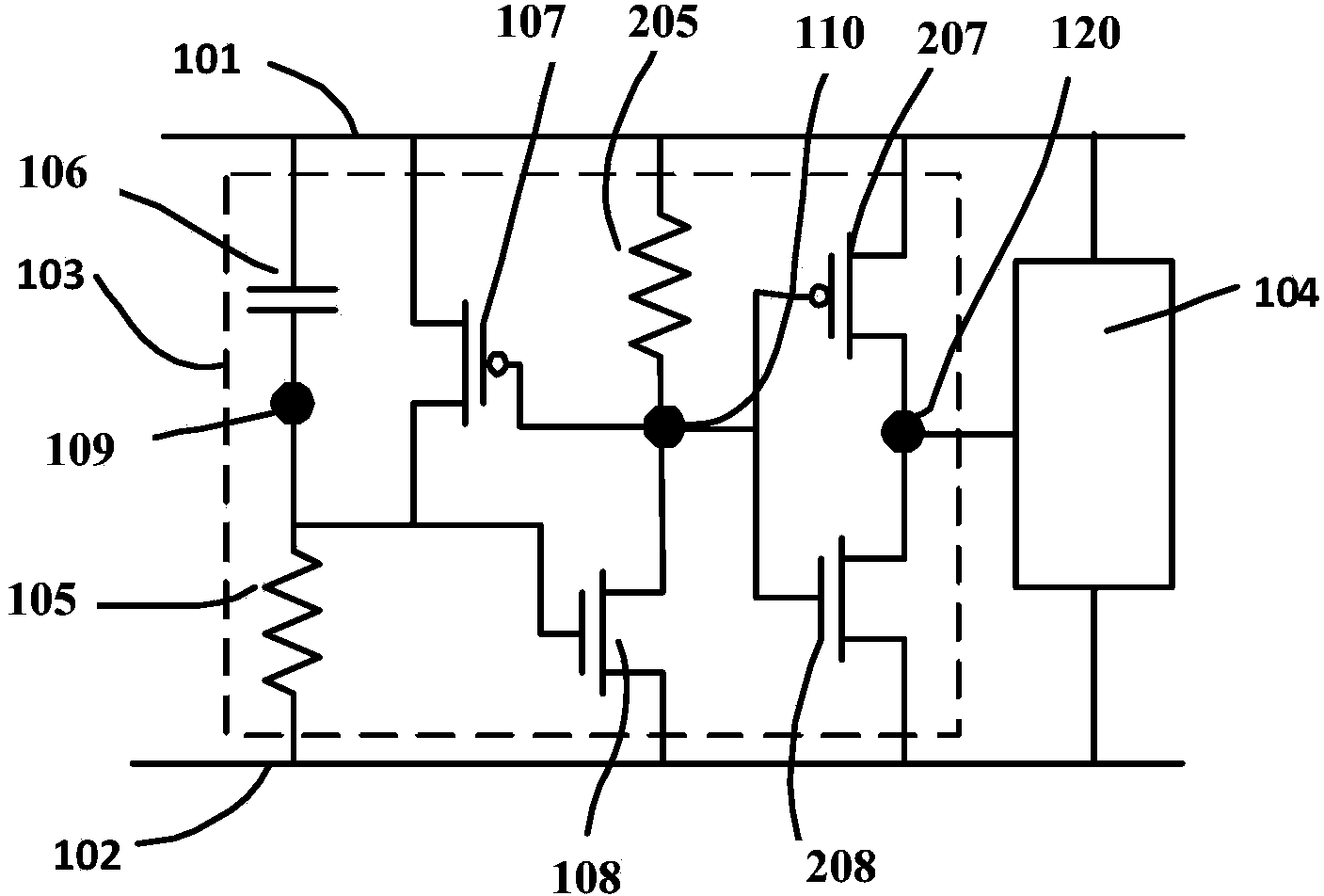

[0025] Another RC trigger type ESD protection circuit for integrated circuits provided by the present invention, such as image 3 As shown, it includes: RC trigger circuit 103 and ESD clamping device 104 . The trigger circuit 103 includes two resistors 105 and 205 , a capacitor 106 , two PMOS transistors 107 and 207 , and two NMOS transistors 108 and 208 . The capacitor after the first resistor 105 and capacitor 106 are connected in series is connected to the VDD power supply line 101, and its resistor is connected to the VSS power supply line 102; the connection point 109 between the first resistor 105 and the capacitor 106 is connected to the drain of the first PMOS transistor 107 and the first The gate of the NMOS transistor 108, the source of the first PMOS transistor 107 is connected to the VDD power supply line 101, the source of the first NMOS transistor 108 is connected to the VSS power supply line 102, the gate of the first PMOS transistor 107 and the first NMOS trans...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More