FinFET and preparation method thereof

A technology of fins and substrates, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of doping dose loss and affecting SSRW morphology, etc., to reduce device power consumption and improve carrier migration rate, to achieve the effect of the isolation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

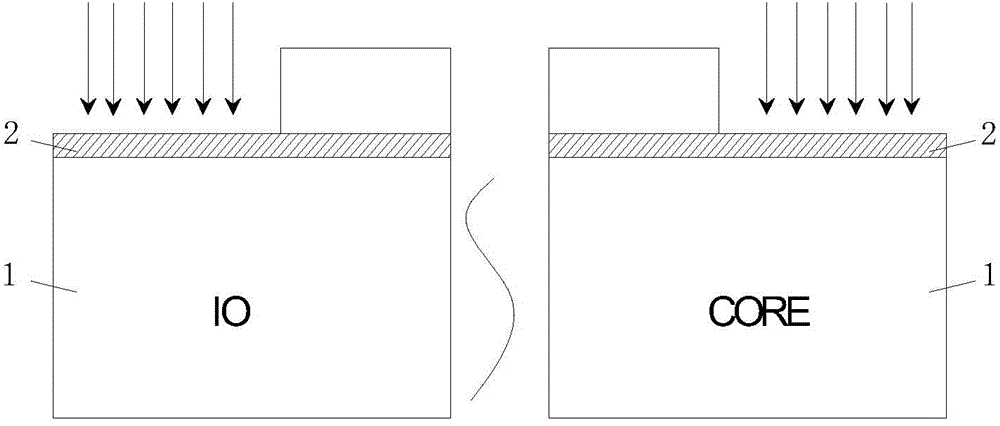

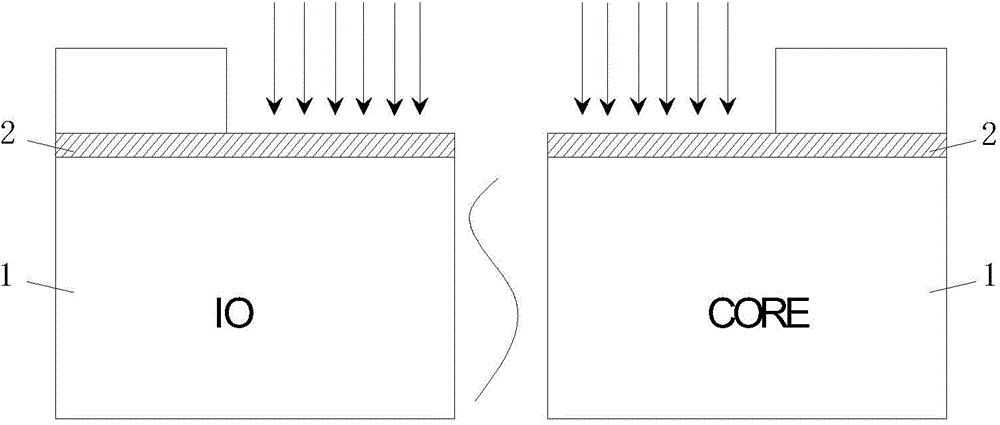

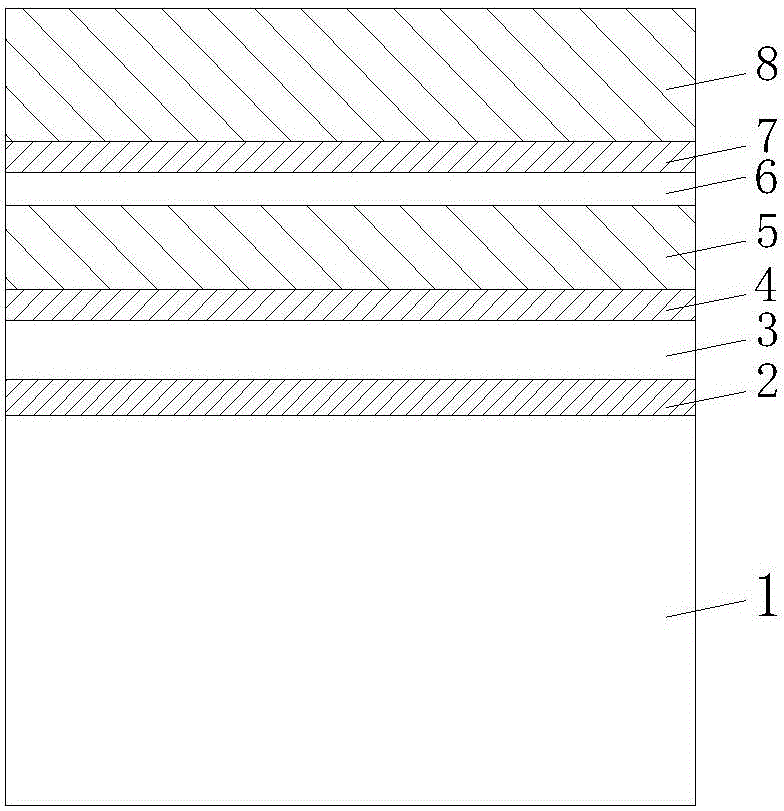

[0042] The present invention provides a FinFET preparation method. In the present invention, SSRW technology can be well applied to three-dimensional FinFET preparation. Refer to Figure 1-20 As shown, the specific steps are as follows,

[0043] Step S1: First, a semiconductor substrate 1 is provided, and a pad oxide layer 2 (PAD oxide) is prepared on the upper surface of the substrate. This substrate 1 includes IO (InputOutput, input and output) device area and core (CORE) device area, and IO device area and core device area all define NMOS area and PMOS area; The PMOS area is subjected to one or more ion implantation processes, specifically: using a photolithography process, using photoresist to block the IO device area and the PMOS area in the core device area, and then using the photoresist as a mask to cover the NMOS area. Ion implantation is performed in the region; after that, the same steps are performed, and the NMOS region is blocked by photoresist, and ion implantat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More