Dynamically-tuned-gyro digital rebalance loop based on FPGA (Field-Programmable Gate Array)

A dynamic tuning gyroscope and rebalancing technology, which is applied to rotating gyroscopes and other directions, can solve the problems of large size and complex rebalancing circuit, and achieve the effect of size reduction and flexible debugging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The technical solutions of the present invention will be further described in detail below through specific examples.

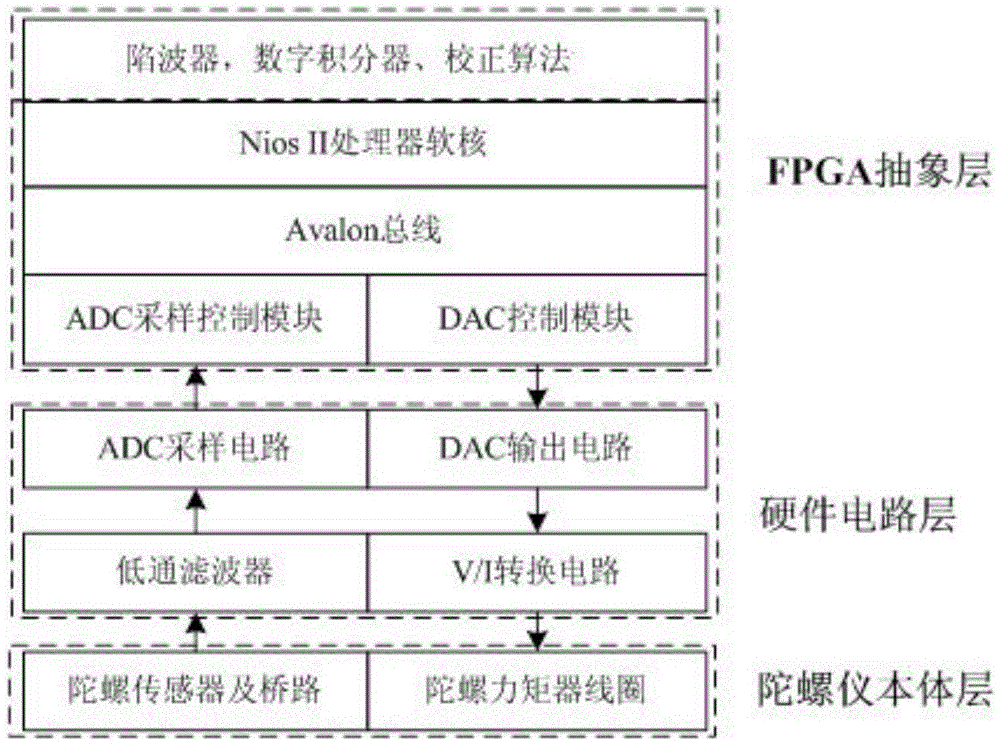

[0026] Such as figure 1 As shown, a kind of FPGA-based power tuning gyroscope digital rebalancing loop of the present invention comprises a gyroscope body layer, a hardware circuit layer, and an FPGA abstraction layer;

[0027] (1) The gyro body layer includes gyro sensors, bridges and gyro torquer coils;

[0028] The excitation power frequency of the dynamic gyro sensor is the system setting value, which is 43.2KHz in this embodiment; when the rotor is displaced relative to the housing, the gyro sensor outputs an AC signal containing rotor position information modulated by 43.2KHz, and the gyro sensor The output AC signal is amplified through the bridge;

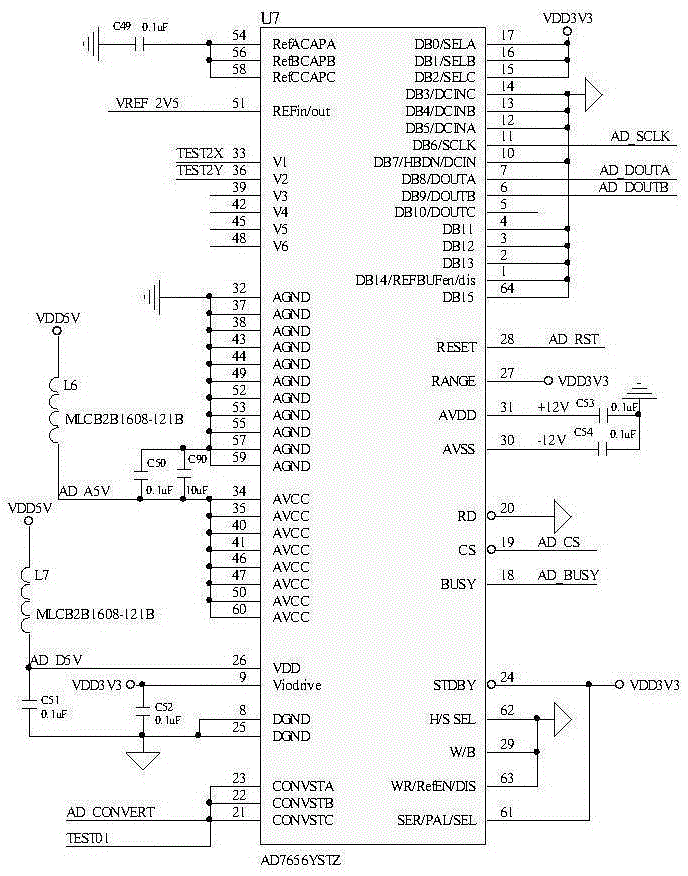

[0029] (2) The hardware circuit layer includes a low-pass filter, ADC sampling circuit, DAC output circuit and V / I conversion circuit; the FPGA abstraction layer includes NiosII processor, Avalon ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Frequency | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More