Method for manufacturing through-hole silicon via

一种穿透硅通孔、制造方法的技术,应用在半导体/固态器件制造、电气元件、电固体器件等方向,能够解决出现裂缝、功率损失增加、穿透硅通孔隔离难等问题,达到简单制造的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

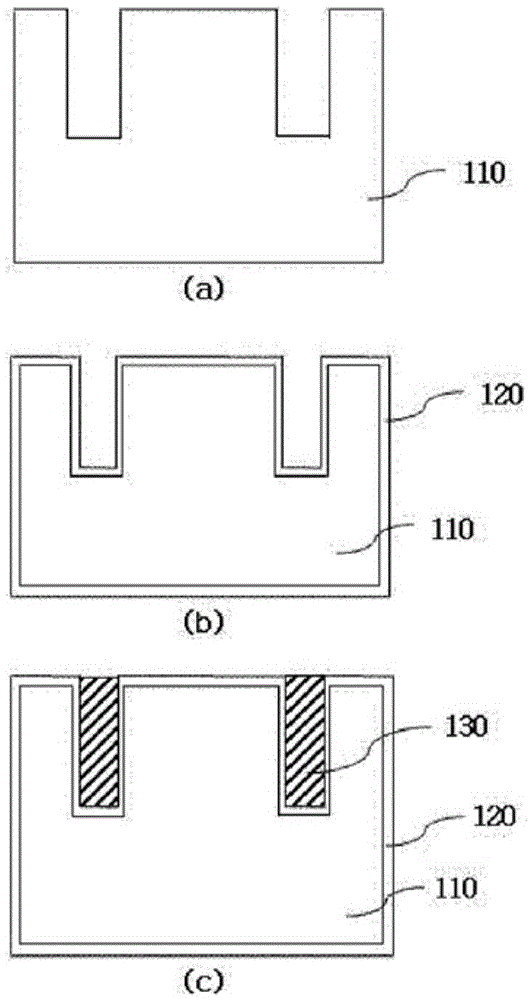

[0029] Hereinafter, the present invention will be described in more detail with reference to the accompanying drawings.

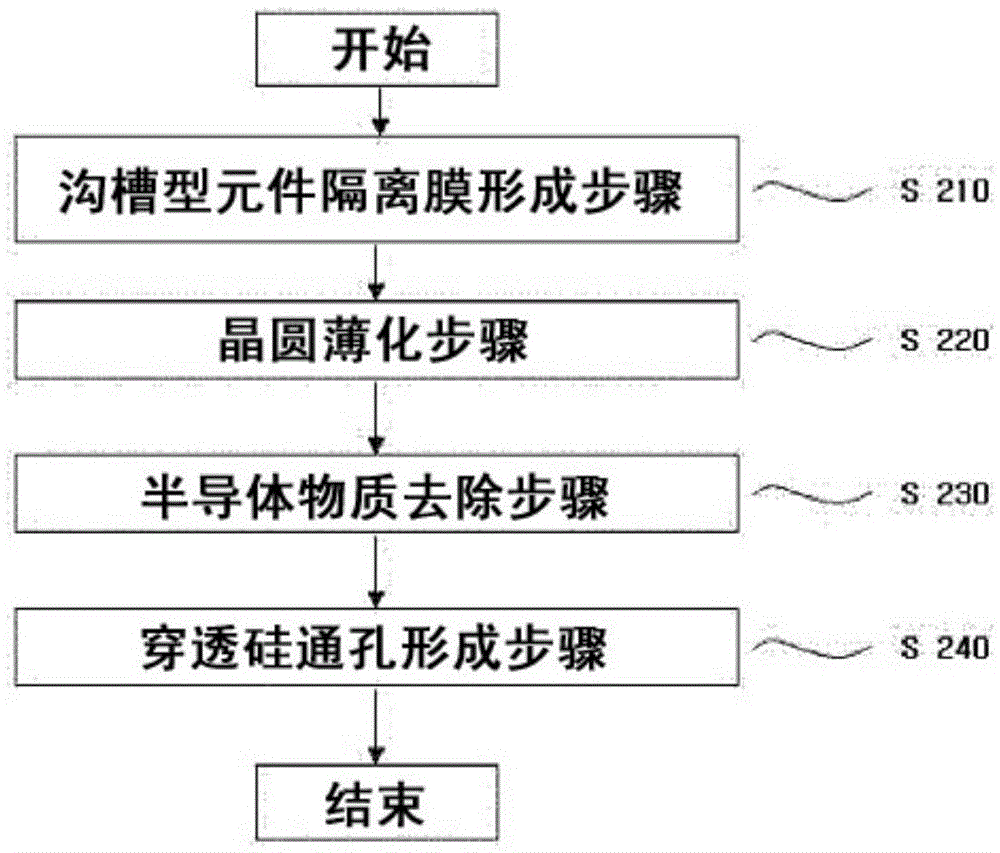

[0030] Figure 2 to Figure 3 It is a process flow diagram showing a manufacturing method of a TSV according to an embodiment of the present invention.

[0031] refer to figure 2 , the manufacturing method of the TSV according to an embodiment of the present invention includes the step of forming a trench-type device isolation film (S210), the step of wafer thinning (S220), the step of removing semiconductor substances (S230) and the step of TSV Hole forming step (S240).

[0032] Firstly, the step of forming a trench-type device isolation film ( S210 ) is to form a trench-type device isolation film on the first wafer by using a trench-type device isolation process.

[0033] That is, a trench-type element isolation film is formed at the position where the TSV is to be formed by using a trench-type element isolation process.

[0034] At this time, the tre...

PUM

| Property | Measurement | Unit |

|---|---|---|

| aspect ratio | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com