Rework method for wafer level chip packaging bumps

A chip packaging and wafer-level technology, which is applied in the manufacture of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., can solve problems such as high risk of wafer scrapping, high-risk abnormalities, and inability to meet SMT requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0031] A method for reworking wafer-level chip packaging bumps, comprising the following steps:

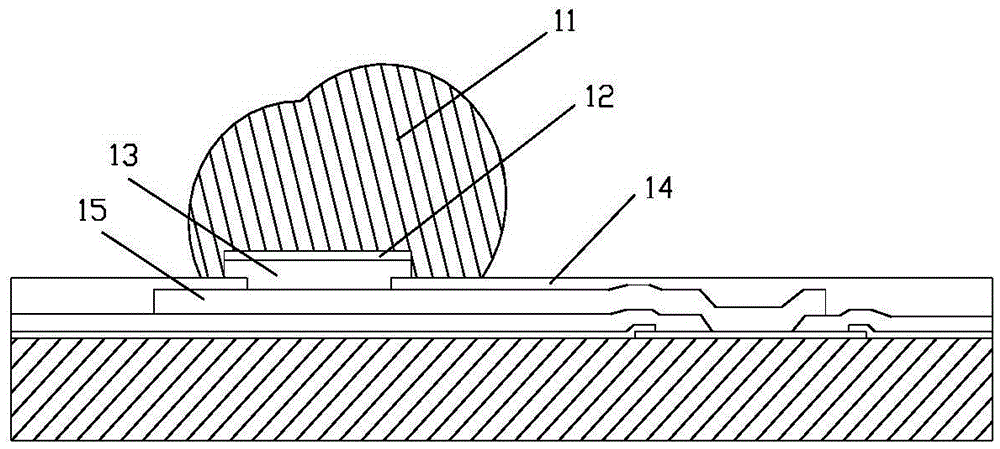

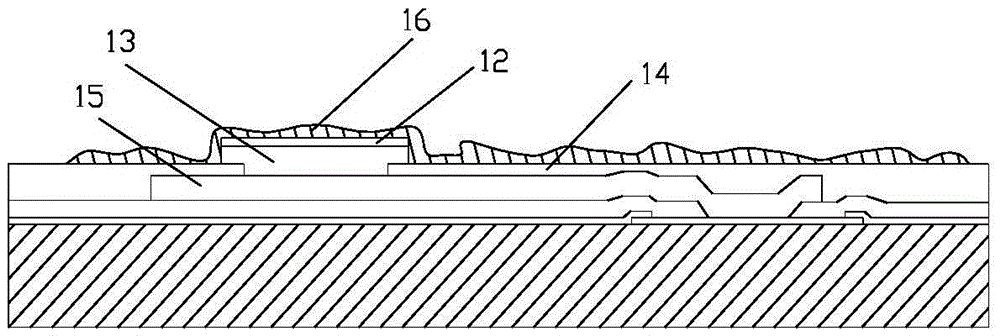

[0032] see figure 1 and figure 2 , (1) remove the bump: use the first wet etching solution to dissolve the bump 11 to form the surface solder attachment residue 16; the mass percentage of each substance in the first wet etching solution is: 15% nitric acid, 65% formazan cyclic acid, 20% pure water.

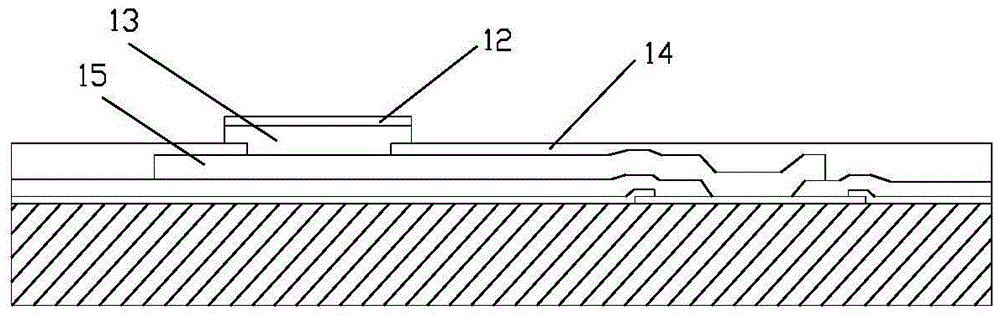

[0033] see figure 2 and image 3 , (2) Removal of surface solder adhesion residue 16: remove surface solder adhesion residue 16 by RF, Radio Frequency radio frequency back sputtering, after removing surface solder adhesion residue, expose bump solder 12 and passivation layer 14, bump pad 12 is provided with an IMC alloy layer 13; that is, only the bump pad 12 and the IMC alloy layer 13 are left at the original bump 11;

[0034] see image 3 and Figure 4 , (3) remove the bump pad 12 and the IMC alloy layer 13: carry out the copper etching of the bump pad by the second wet etc...

Embodiment 2

[0038] The method is the same as that of Example 1, except that the mass percentages of the substances in the first wet etching solution are: 10% nitric acid, 60% methyl cyclonic acid, and 30% pure water.

Embodiment 3

[0040] The method is the same as that of Example 1, except that the mass percentages of the substances in the first wet etching solution are: 12% nitric acid, 70% methyl cyclonic acid, and 18% pure water.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More