Low-trigger-voltage SCR (semiconductor control rectifier) device used for ESD (electro-static discharge) protection

A low trigger voltage, ESD protection technology, applied in the direction of electric solid devices, electrical components, semiconductor devices, etc., can solve the problem of reducing the trigger voltage of SCR devices, and achieve the effect of reducing the trigger voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

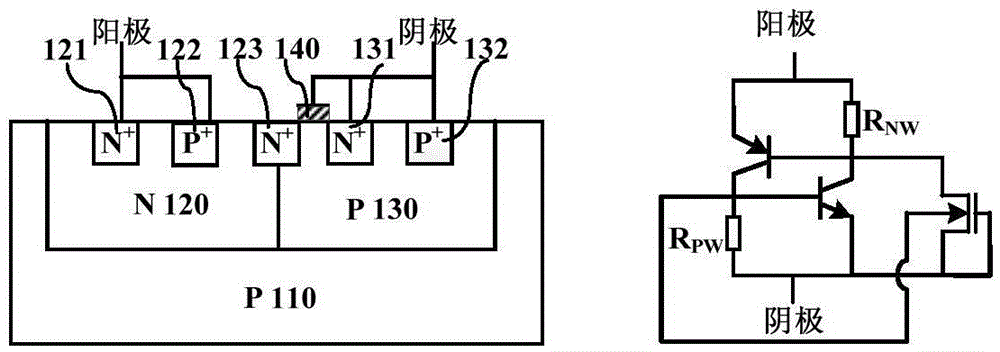

[0026] This embodiment provides a novel low trigger voltage SCR device, the structure and equivalent circuit of the SCR device are as follows figure 2 As shown, its structure includes:

[0027] p-type silicon substrate 110;

[0028] A well region is formed on the p-type silicon substrate 110, the well region includes an n-type well region 120 and a p-type well region 130, and the well region 120 is adjacent to the well region 130;

[0029] The n-type well region 120 is provided with an n-type heavily doped region 121 and a p-type doped region 122, and the n-type heavily doped region 121 and the p-type heavily doped region 122 are connected to the anode;

[0030] The p-type well region 130 is provided with an n-type heavily doped region 131 and a p-type heavily doped region 132, and the n-type heavily doped region 131 and the p-type heavily doped region 132 are connected to the cathode;

[0031] The n-type heavily doped region 123 is bridged between the n-type well region 12...

Embodiment 2

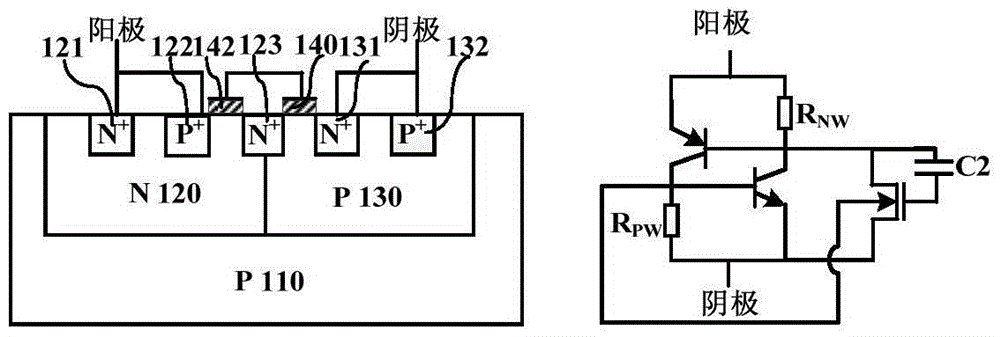

[0036] This embodiment provides a novel low trigger voltage SCR device, the structure and equivalent circuit of the SCR device are as follows image 3 As shown, in its structure, the gate oxide layer region 142 on the silicon surface of the n-type well region 120 is arranged between the p-type heavily doped region 122 and the n-type heavily doped region 123, and the surface of the gate oxide layer region 142 is a polysilicon layer It is connected to the polysilicon layer on the surface of the gate oxide region 140 through a metal layer.

[0037] The SCR device is composed of a parasitic PNP transistor, a parasitic NPN transistor and a parasitic N-channel MOSFET device. Among them, p-type heavily doped region 122, n-type well region 120, p-type well region 130 and p-type heavily doped region 132 form a PNP transistor; n-type heavily doped region 131, p-type well region 130, n-type Well region 120 and n-type heavily doped region 121 form an NPN transistor; n-type heavily doped ...

Embodiment 3

[0043] This embodiment provides a novel low trigger voltage SCR device. In the SCR device structure, the gate oxide region on the silicon surface of the n-type well region 120 is arranged in the n-type heavily doped region 121 close to the n-type well region and the p-type well region. The polysilicon layer on the surface of the gate oxide region is connected to the polysilicon layer on the surface of the gate oxide region 140 through a metal layer.

[0044] To sum up, the present invention provides a new type of low trigger voltage SCR device for ESD protection. Through the design of the internal structure, only a gate oxide layer structure is added on the basis of the existing LVTSCR device, and an RC is introduced inside the device. (Resistance-Capacity) path, without changing the area of the device, the purpose of further reducing the trigger voltage of the SCR device is realized.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More