High-speed serial bus storage device provided with multiple high-speed interfaces

A high-speed serial bus and storage device technology, applied in the input/output process of data processing, instruments, electrical digital data processing, etc., can solve the problems of increased power consumption of disk arrays, slow read and write speeds, and low stability , to achieve the effect of guaranteeing reliability, improving reading and writing speed, and rich resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

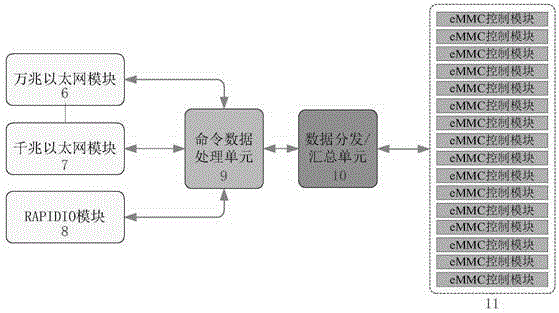

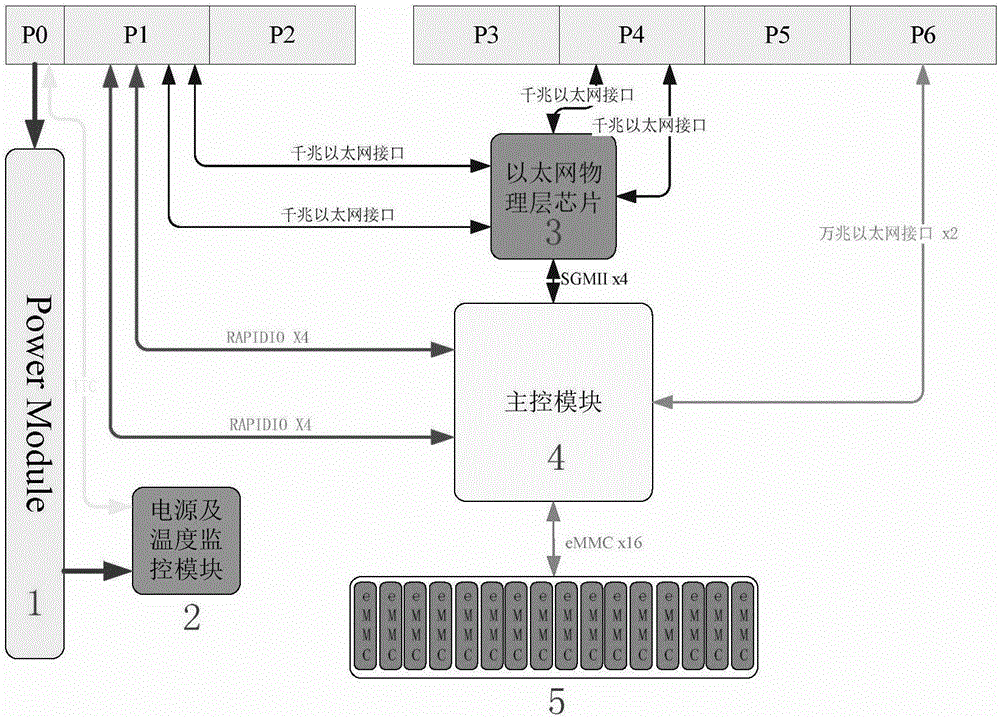

[0023] Preferably, the main control module 4 of the present invention adopts an FPGA chip, and the storage unit adopts an EMMC chip, and there are four groups of four chips in total.

[0024] According to the usage of different network interfaces, the usage efficiency is improved. Preferably, the main control module leads two RAPIDIO interfaces, two 10 Gigabit Ethernet interfaces, and 4 Gigabit Ethernet interfaces to the outside of the board.

[0025] In order to better monitor the working conditions of the power supply, the power supply and temperature monitoring module obtains power supply data through the combination of precision resistors and INA230, and obtains temperature data through the TMP100 chip. The power supply and temperature data communicate with the MCU through the IIC bus, and the summarized monitoring The data is sent to the host computer through IIC or serial port.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com