Memory control circuit and memory

A technology for controlling circuits and memory, which is applied in static memory, digital memory information, information storage, etc. It can solve the problems of reduced reading speed, increased local source line voltage, and reduced conduction current of storage cells, so as to improve the reading speed , the effect of increasing the current and reducing the voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

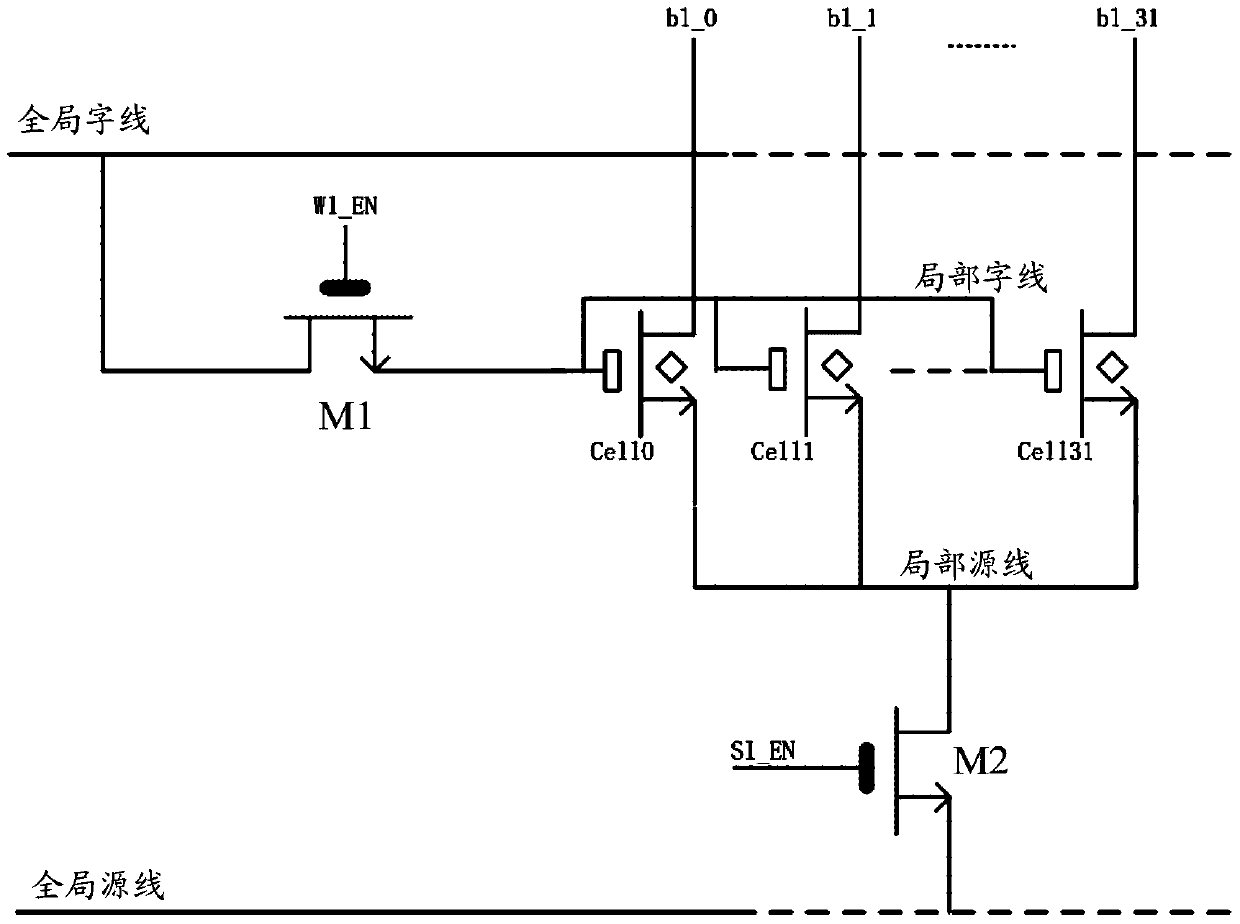

[0023] As mentioned in the background art, in the prior art, due to the small size of the word line gating transistor M1 and the source line gating transistor M2, their current conduction capability is weak; , due to the weak conduction capability of the source line gating tube M2, the local source line voltage rises, the voltage difference between the drain and source of the memory cell decreases, and the conduction current of the memory cell becomes smaller, resulting in a decrease in the read speed and address The read time (Taa) required from input to data output becomes longer, reducing the efficiency of the memory.

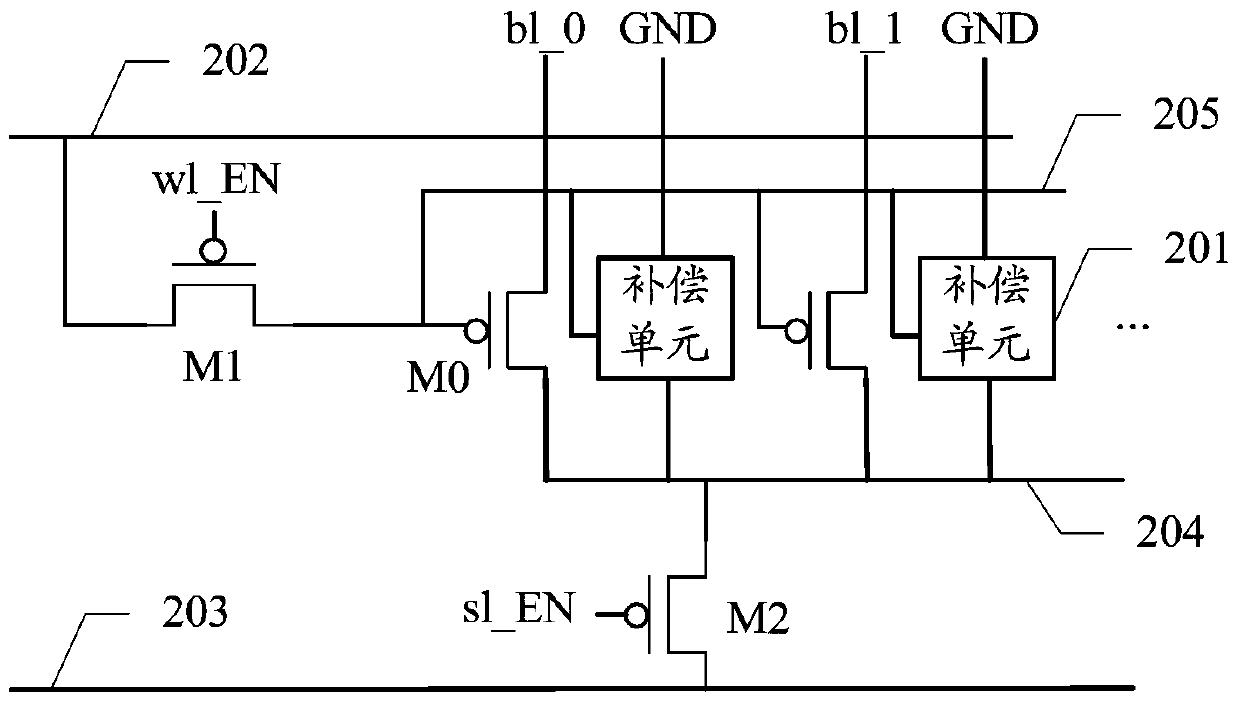

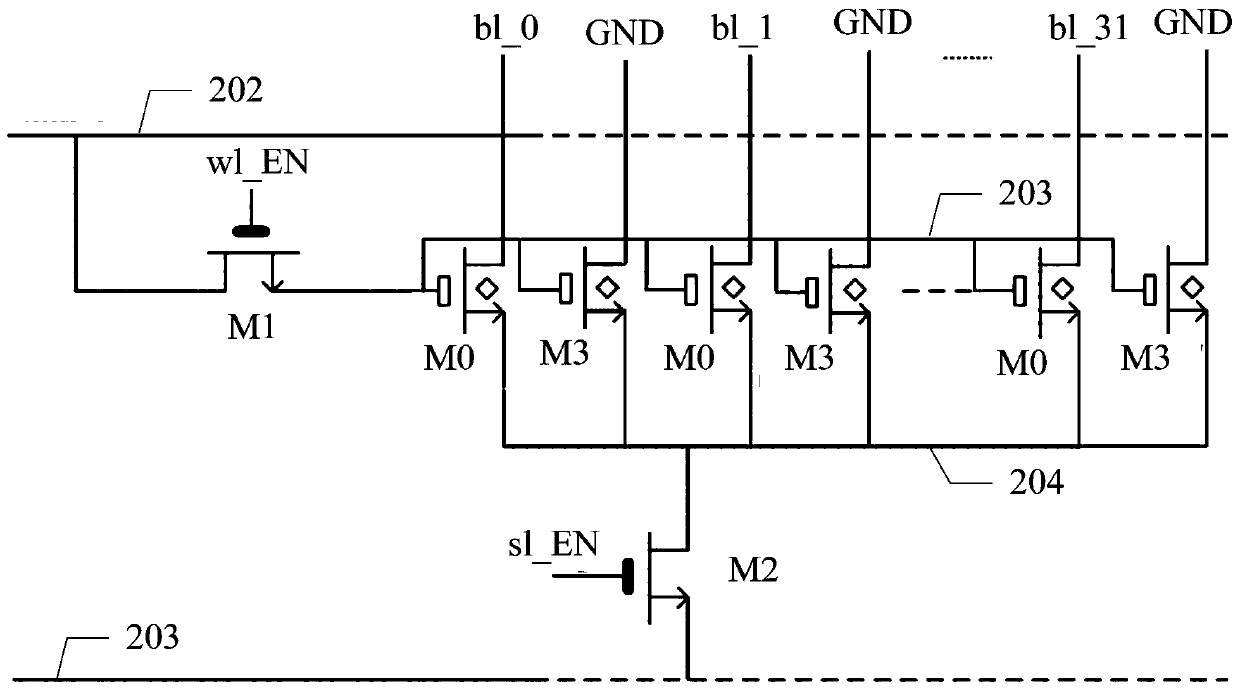

[0024] In order to improve the read speed of the memory, the size of the source line gating transistor M2 can be increased to increase its current conduction capability; however, due to the limitation of the memory chip area, the size increase range of the source line gating transistor M2 is limited. In the embodiment of the present invention, by setting the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More