A zero-bias testing method for an accelerometer signal processing circuit

A technology of signal processing circuit and accelerometer, which is applied in the direction of speed/acceleration/shock measurement, speed/acceleration/shock measurement equipment testing/calibration, measuring device, etc. It can solve the problem of low test efficiency and improve test efficiency. The effect of reducing test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0023] Zero-bias stability test method for monolithic circuits:

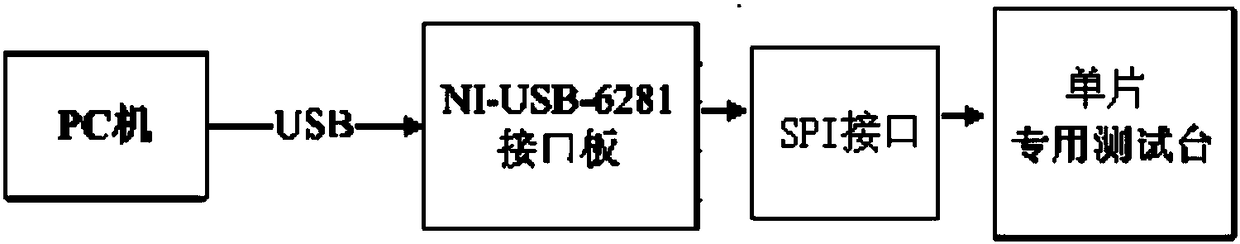

[0024] Using the combination of a single-chip dedicated test bench and the NI-USB-6281 interface board, the relevant parameters of the circuit can be set and adjusted through a PC, so that the corresponding output terminals of the circuit will change. The NI-USB-6281 interface board and the circuit are connected through the SPI interface, and the circuit EEPROM is erased, read and written by the special software in the PC. Test principle according to figure 1 shown.

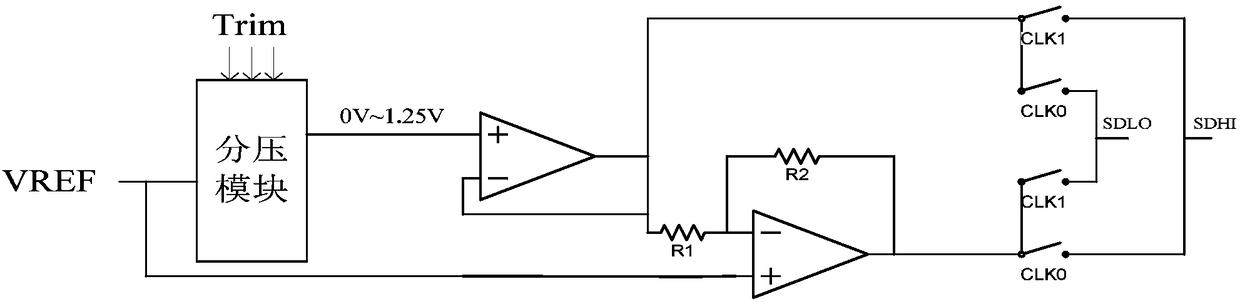

[0025] Use the special test software developed by LABVIEW to control the NI-USB-6281 interface board on the PC, and operate the EEPROM of the circuit through the SPI interface. Use a voltmeter to monitor the open-loop output voltage VOUT_OL, and adjust the parameters TrimCap1 and TrimCap2 through Address 000 in the software to make the VOUT_OL value 2.5±0.01V.

[0026] Using the virtual instrument as the platform, use the NI-USB-6281 high-speed ...

Embodiment 2

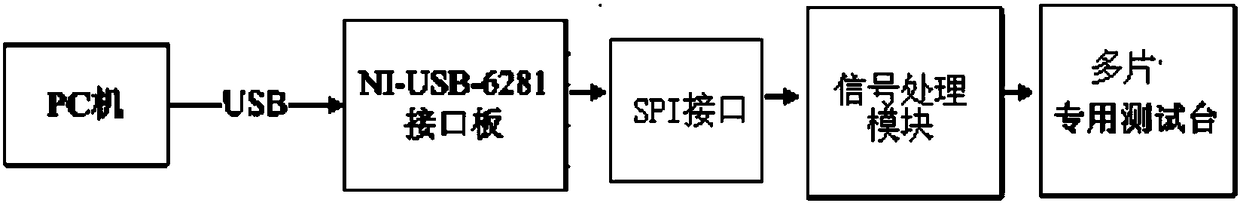

[0028] Zero-bias stability test method for multi-chip circuits:

[0029] The current test software is partly processed by a single chip based on MATLAB, which requires 8 times of modification of the MATLAB program to process the 8 accelerometer signal processing circuits. The test process is complicated, and the previous transformation has little effect. In order to improve the test efficiency, the processing program of the zero bias stability of the accelerometer signal processing circuit is packaged into an operation interface for testers. As long as the zero bias data storage address of the previous 8 bias accelerometer circuit stability test is correctly entered, the 8 bias data can be automatically obtained. Bias stability index of chip gyroscope.

[0030] Using the combination of multi-chip special test bench and NI-USB-6281 interface board, the relevant parameters of the accelerometer signal processing circuit can be set and adjusted through the PC to change the corresp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com