Logical block address-to-physical block address mapping method for high-capacity solid-state disk

A technology of logic mapping and solid-state hard disk, which is applied in the direction of electrical digital data processing and instruments, and can solve problems such as complex design, large mapping table, and high power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not used to limit the present invention.

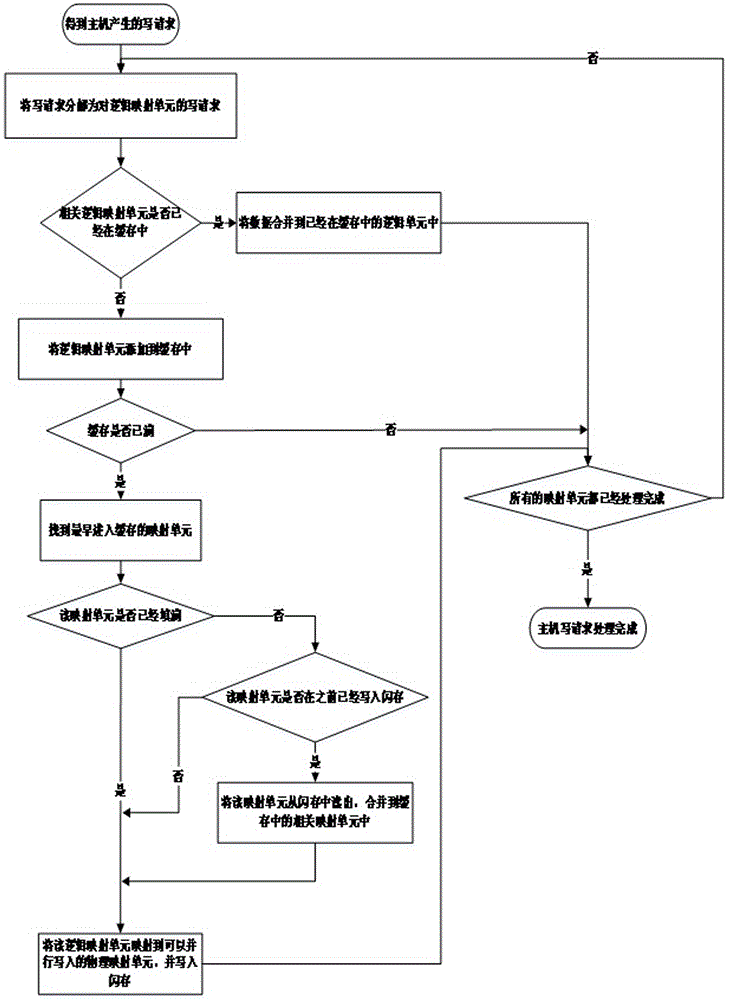

[0030] Such as figure 1 As shown, a method for mapping a large-capacity solid state drive from a logical address to a physical address includes the following steps:

[0031] Step 1. Obtain the write request generated by the host;

[0032] Step 2. Decompose the write request obtained above into write requests to the logical mapping unit, and go to step 3;

[0033] Step 3. Determine whether the above logical mapping unit is already in the cache. If the logical mapping unit is in the cache, merge the write request data for the logical mapping unit decomposed in step 2 into the logical mapping unit in the cache, and go to step 9. If the logical mapping unit is not in the cache, go...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More