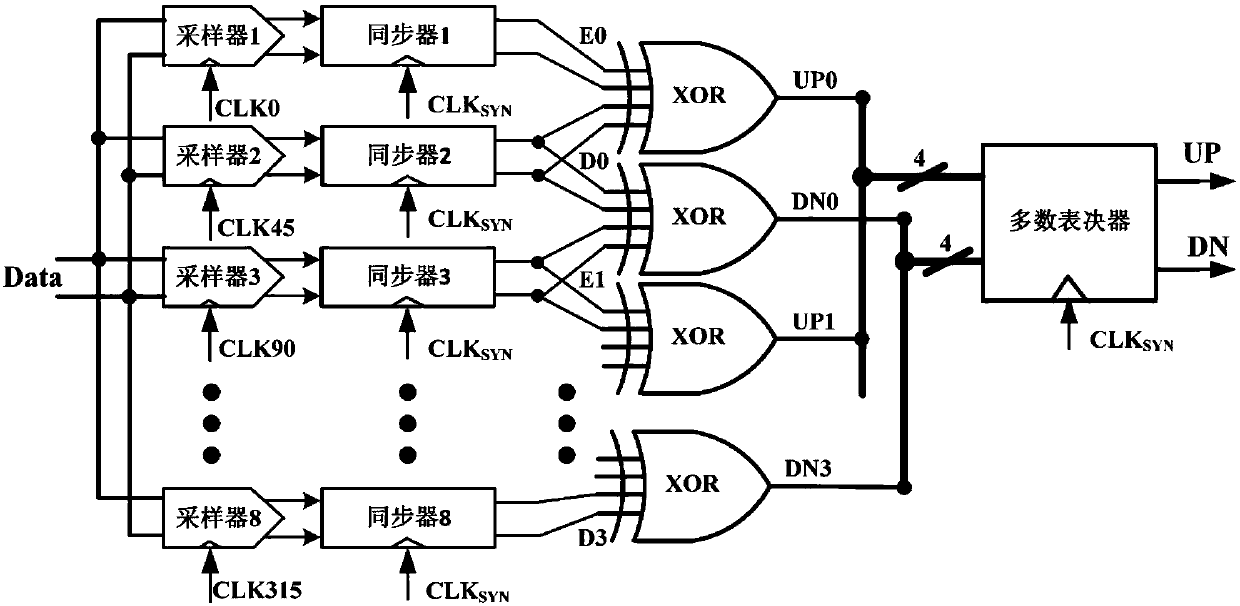

A Bang-bang Phase Detector Applied in Subrate Clock Data Recovery Circuit

A rate clock and recovery circuit technology, applied in the direction of automatic power control, electrical components, etc., can solve the problems of phase deviation, increase the area and power design complexity, affect the jitter performance of the clock data recovery circuit, and reduce the operating frequency. , the effect of reducing the number of polyphase clocks and improving jitter performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

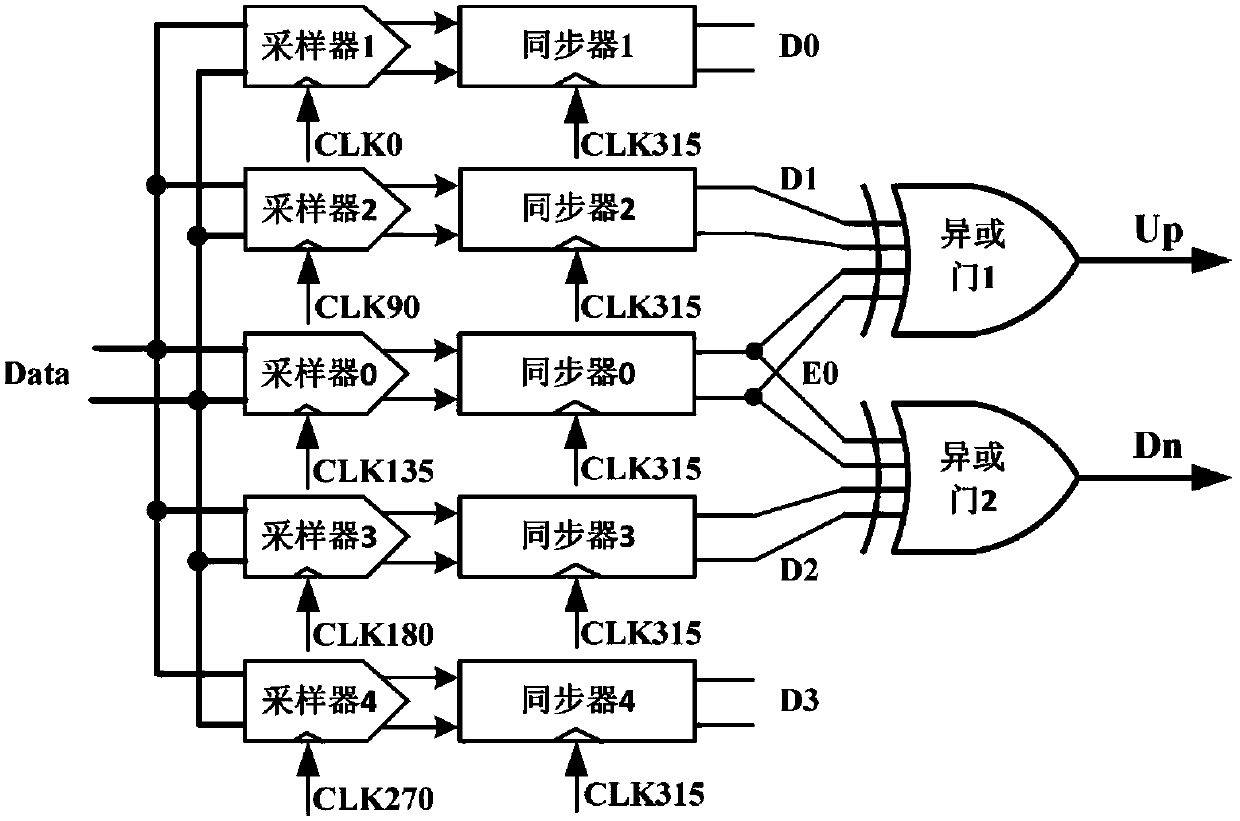

[0028] refer to figure 2 A Bang-Bang phase detector applied to a sub-rate clock data recovery circuit in this embodiment is specifically a Bang-Bang phase detector applied to a 1 / 4 rate clock data recovery circuit, that is, N=4.

[0029] The four data samplers used in this embodiment are respectively sampler 1, sampler 2, sampler 3 and sampler 4, and the four data synchronizers used are respectively synchronizer 1, synchronizer 2, synchronizer 3 and sampler 4. Synchronizer 4, the edge sampler at figure 2 Labeled as Sampler 0, the edge synchronizer is in figure 2 Marked as synchronizer 0, the two XOR gates are XOR gate 1 and XOR gate 2 respectively.

[0030] Sampler 1, sampler 2, sampler 3, and sampler 4 sample the input data Data under the action of data sampling clocks CLK0, CLK90, CLK180, and CLK270 with phases of 0, 90, 180, and 270, respectively. The input data Data is sampled under the action of the edge sampling clock CLK135 with a phase of 135. Synchronizer 1, Sy...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More