Insulated gate bipolar transistor structure and manufacturing method thereof

A technology of bipolar transistors and insulated gates, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve difficult problems and achieve low on-state voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0088] The invention will be described using n-channel devices, but it will be understood in the following description that the invention is equally applicable to p-channel devices. In the specification of the present invention, the heavily doped n-type region is marked as n + , and the heavily doped p-type region is labeled p + , in silicon, unless otherwise stated, heavily doped regions typically have 19 cm -3 with 1×10 21 cm -3 Doping concentration between. In the specification of the present invention, the lightly doped n-type region is marked as n - , and the lightly doped p-type region is labeled p - , in silicon, unless otherwise stated, lightly doped regions typically have 13 cm -3 with 1×10 17 cm -3 Doping concentration between.

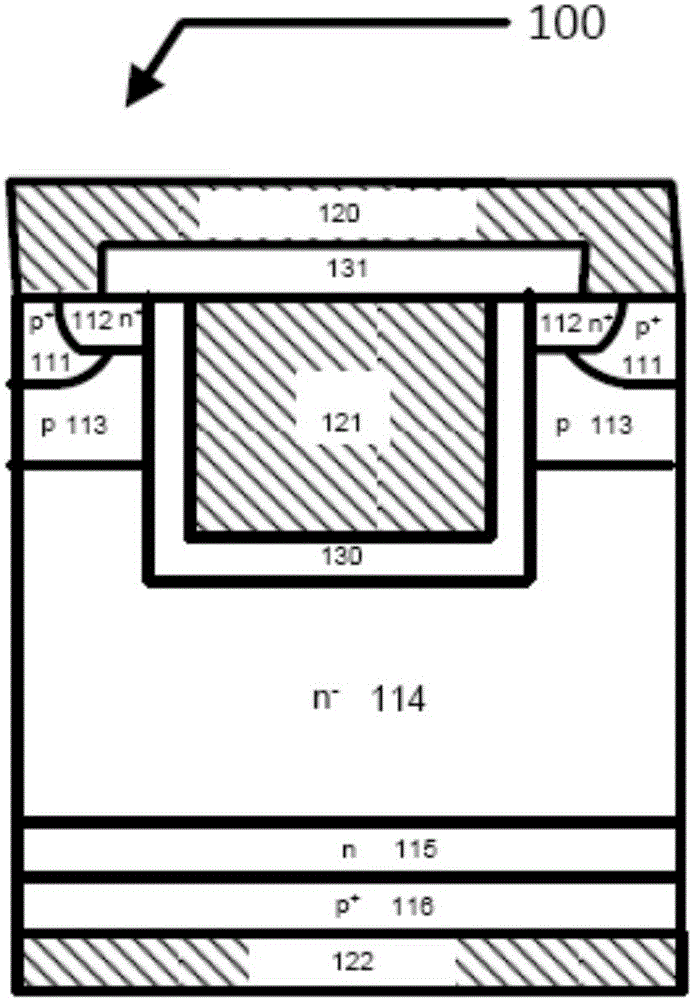

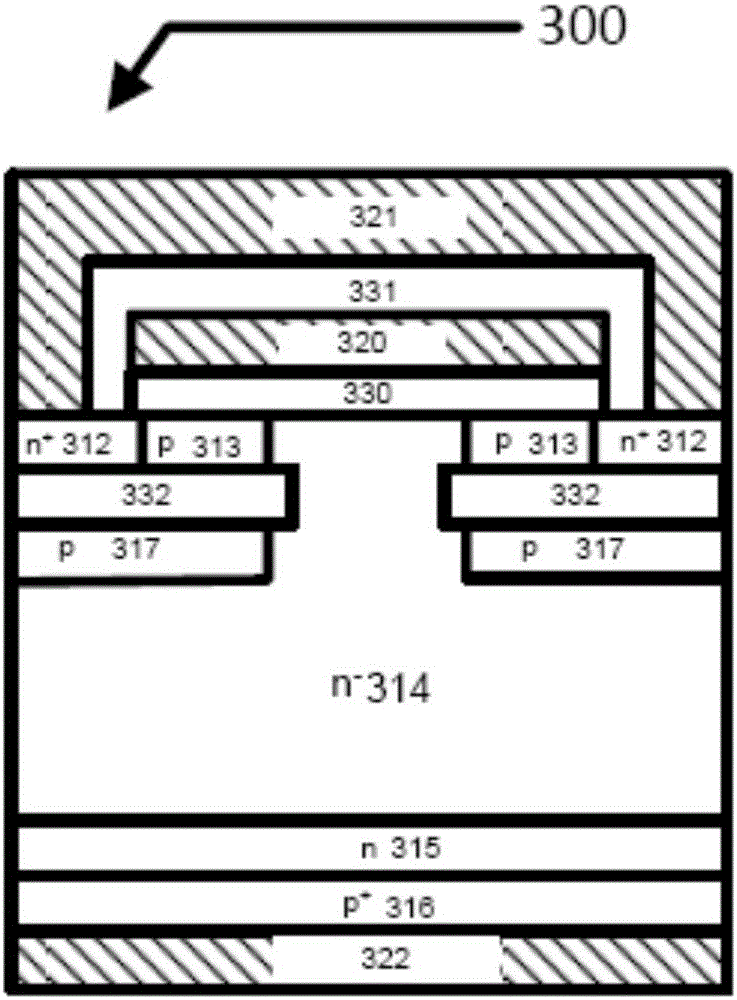

[0089] image 3 is a cross-sectional view of the invention implemented in IGBT device 300, Figure 4 is a top view of the same device 300 . Device 300 includes: a collector (322) at the bottom; a p + collector area (316); loca...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More