A Low Trigger Voltage Bidirectional SCR Device Based on Buried Layer Triggering

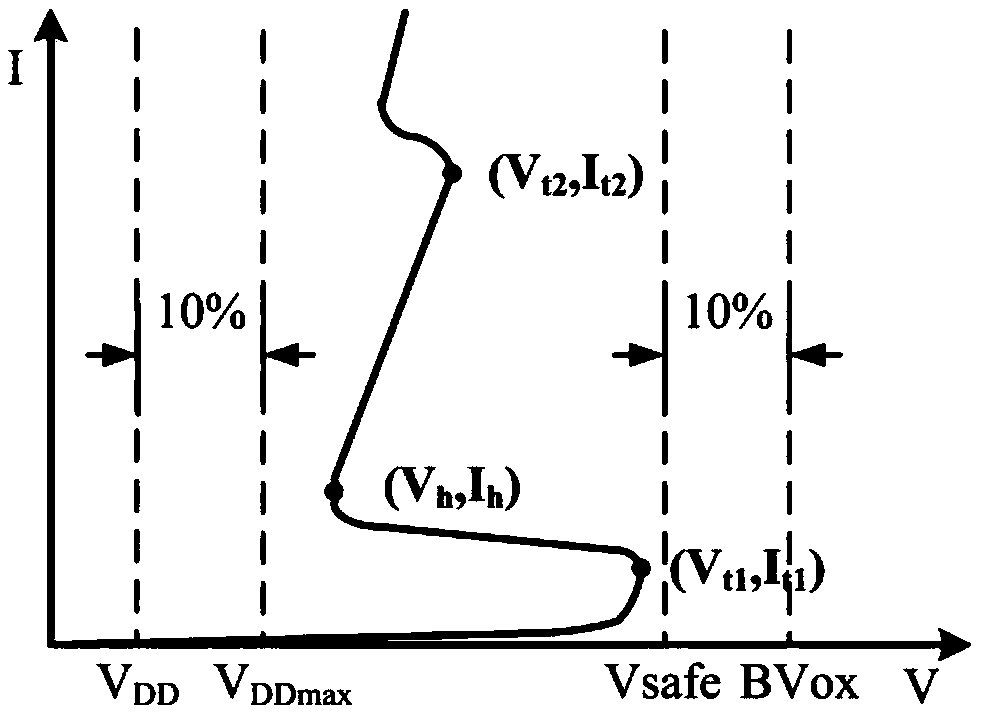

A low trigger voltage, device technology, applied in the electronic field, can solve the problems of unable to realize ESD protection, SCR can not achieve voltage clamping, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

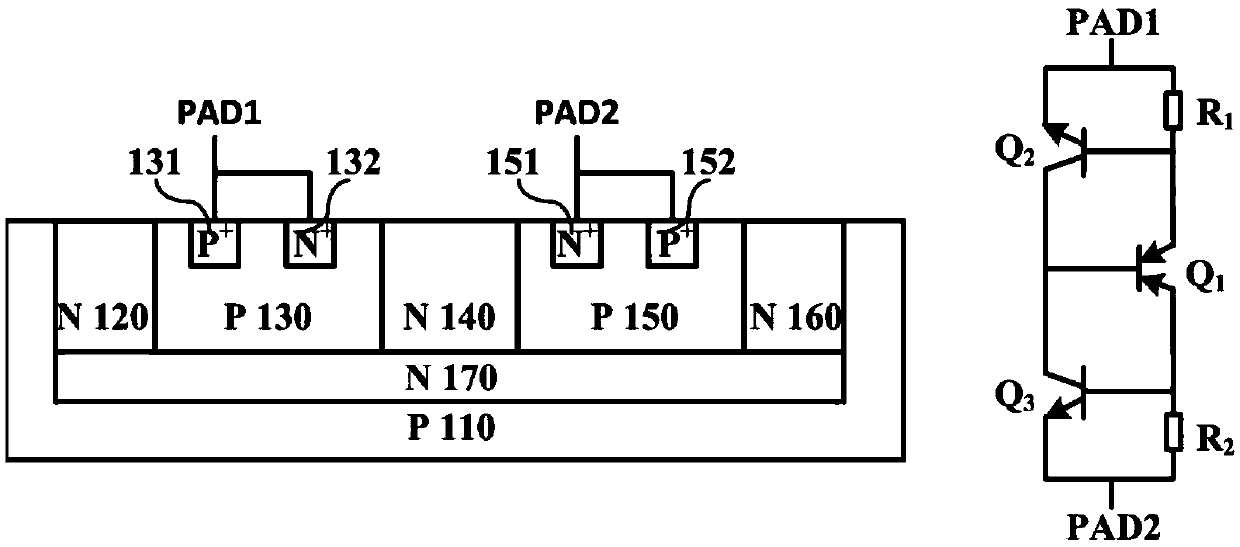

[0021] This embodiment provides a low-trigger-voltage bidirectional SCR device based on buried-layer triggering. Its structural schematic diagram and equivalent circuit diagram are shown in image 3 As shown, it consists of 1 master device, n trigger devices on the left side of the master device and m trigger devices on the right side of the master device, where n≥1, m≥1;

[0022] The main device has a symmetrical structure, including a p-type silicon substrate 110; an n-type heavily doped buried layer 170 is formed on the silicon substrate 110; n-type wells adjacent to each other from left to right are formed on the buried layer 170 Region 120, p-type well region 130, n-type well region 140, p-type well region 150 and n-type well region 160; n-type well region 120 and n-type well region 160 are respectively provided with n-type heavily doped regions 121, 161; the p-type well region 130 is sequentially provided with a p-type heavily doped region 131, an n-type heavily doped re...

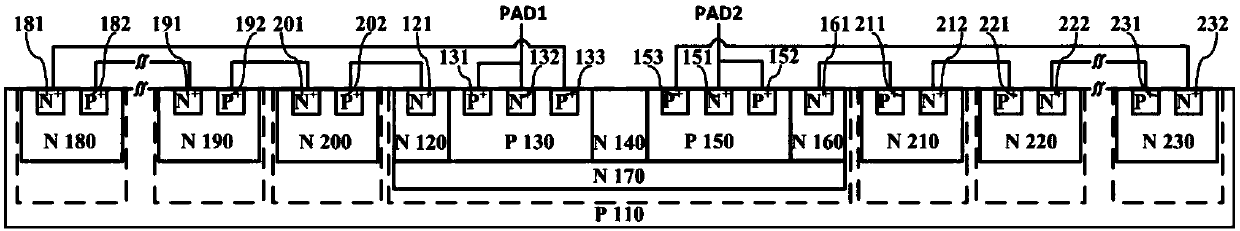

Embodiment 2

[0040] This embodiment provides a low-trigger-voltage bidirectional SCR device based on buried-layer triggering. Its structural schematic diagram and equivalent circuit diagram are shown in Figure 4 As shown, it consists of 1 main device, n trigger devices on the left side of the main device and m trigger devices on the right side of the main device, where n≥1, m≥1; the trigger device structures and devices on both sides of the main device The inter-connection relationship is the same as that of Embodiment 1, and will not be repeated here. The difference is that: the p-type well region 130 of the main device is sequentially provided with a p-type heavily doped region 133, a p-type heavily doped Region 131, n-type heavily doped region 132, p-type heavily doped region 131 and n-type heavily doped region 132 are all connected to PAD1; the p-type well region 150 is provided with n-type heavily doped The impurity region 151 , p-type heavily doped region 152 , p-type heavily doped ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More