Patents

Literature

31results about How to "Effective electrostatic protection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Liquid crystal display

InactiveUS6914643B1Solve the lack of functionNot disadvantageous in of controllingNon-linear opticsElectrical conductorLiquid-crystal display

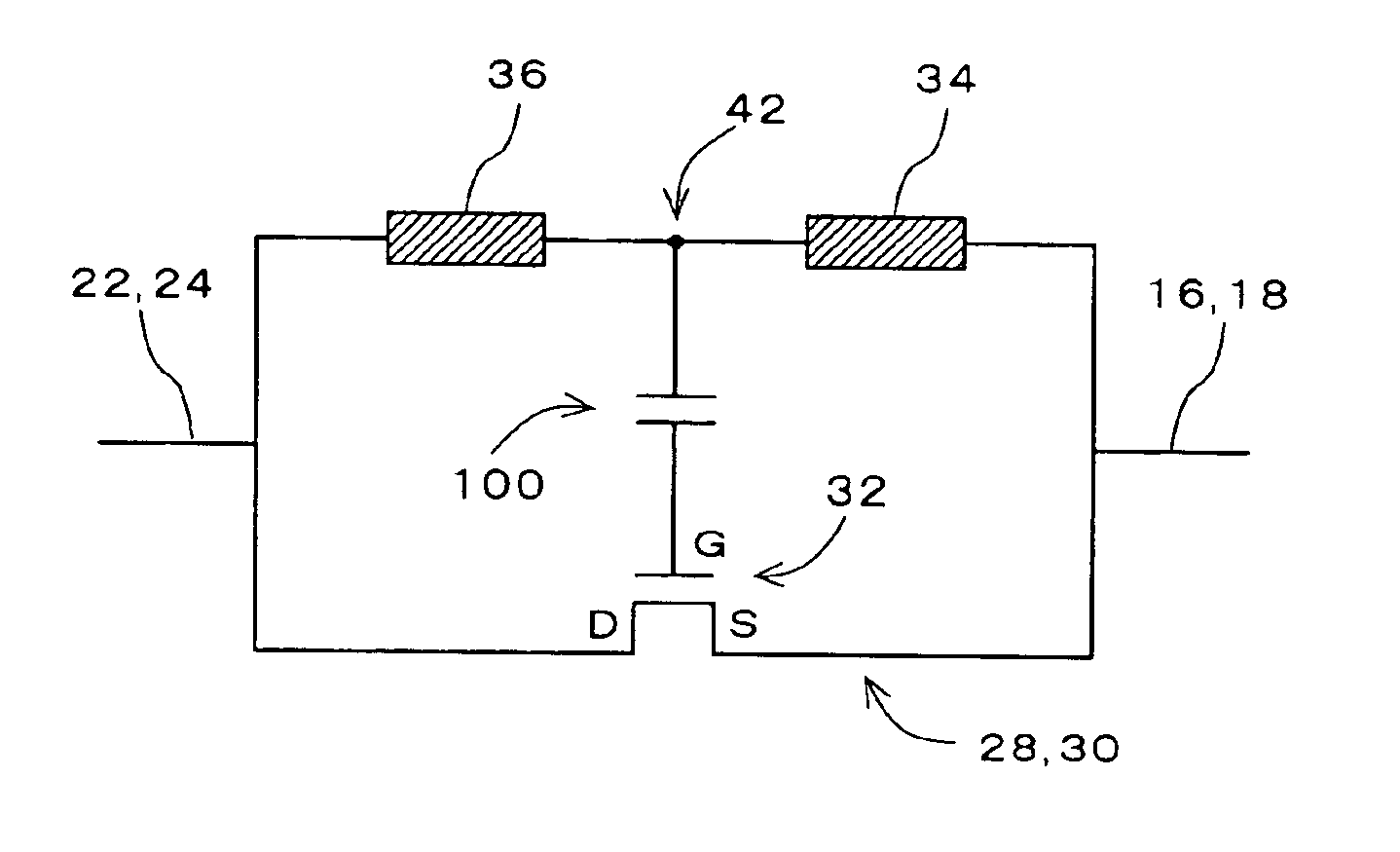

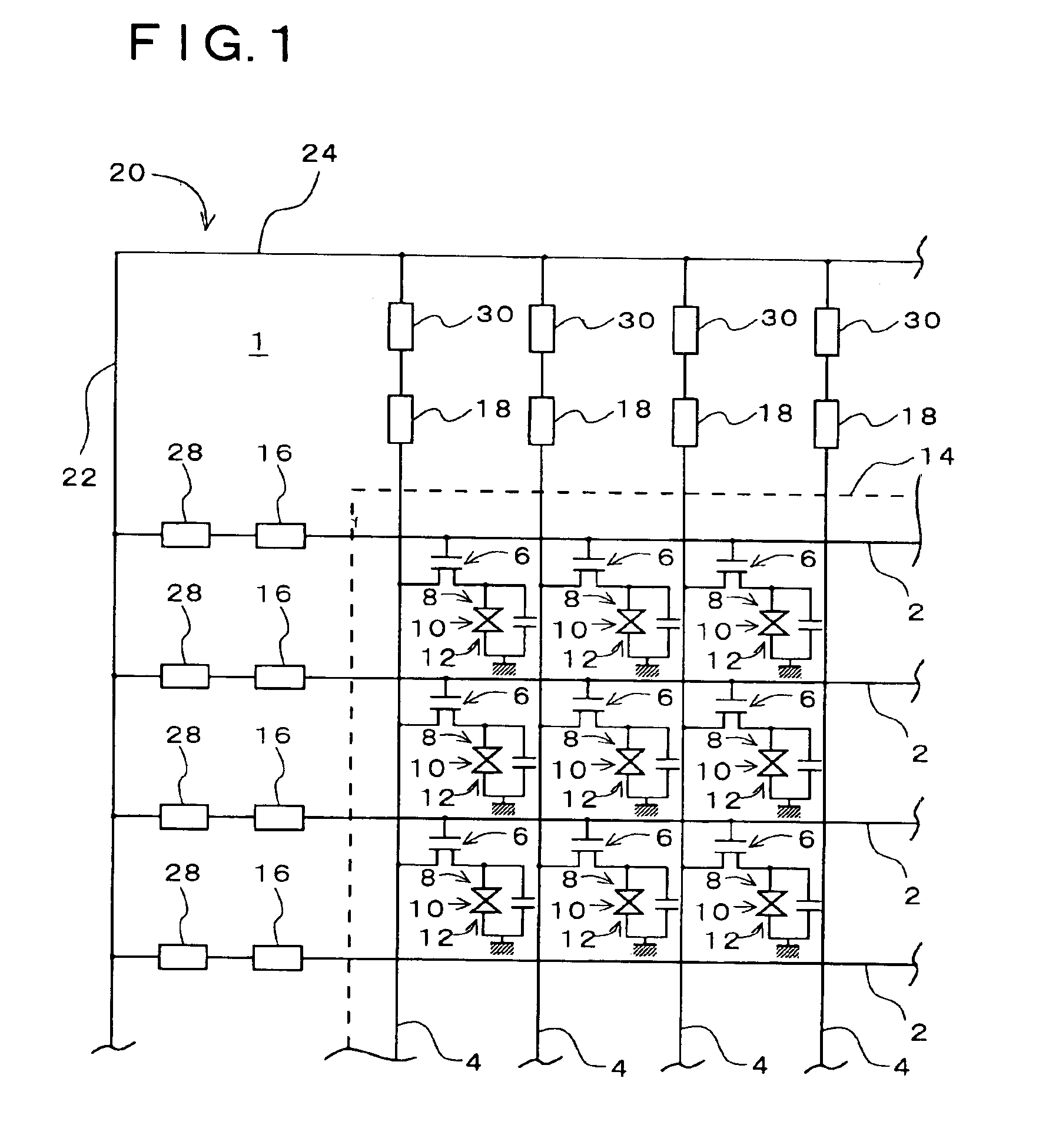

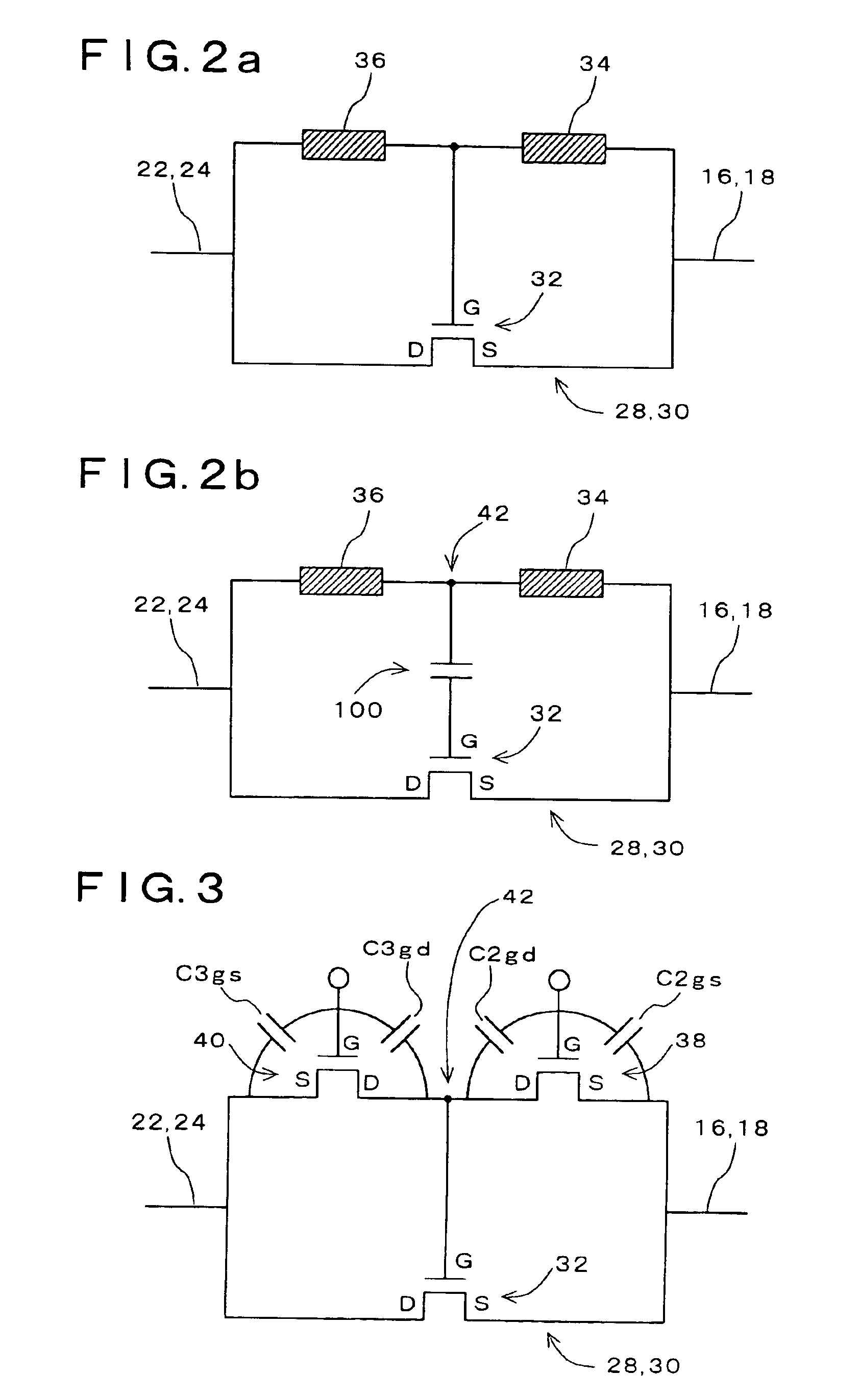

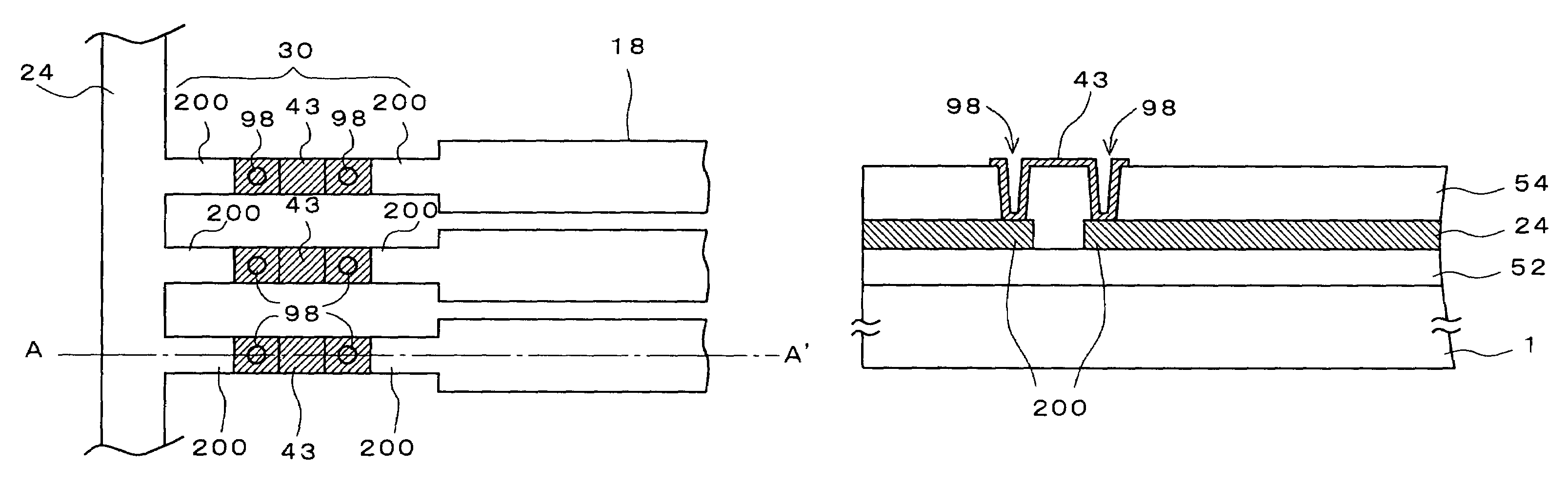

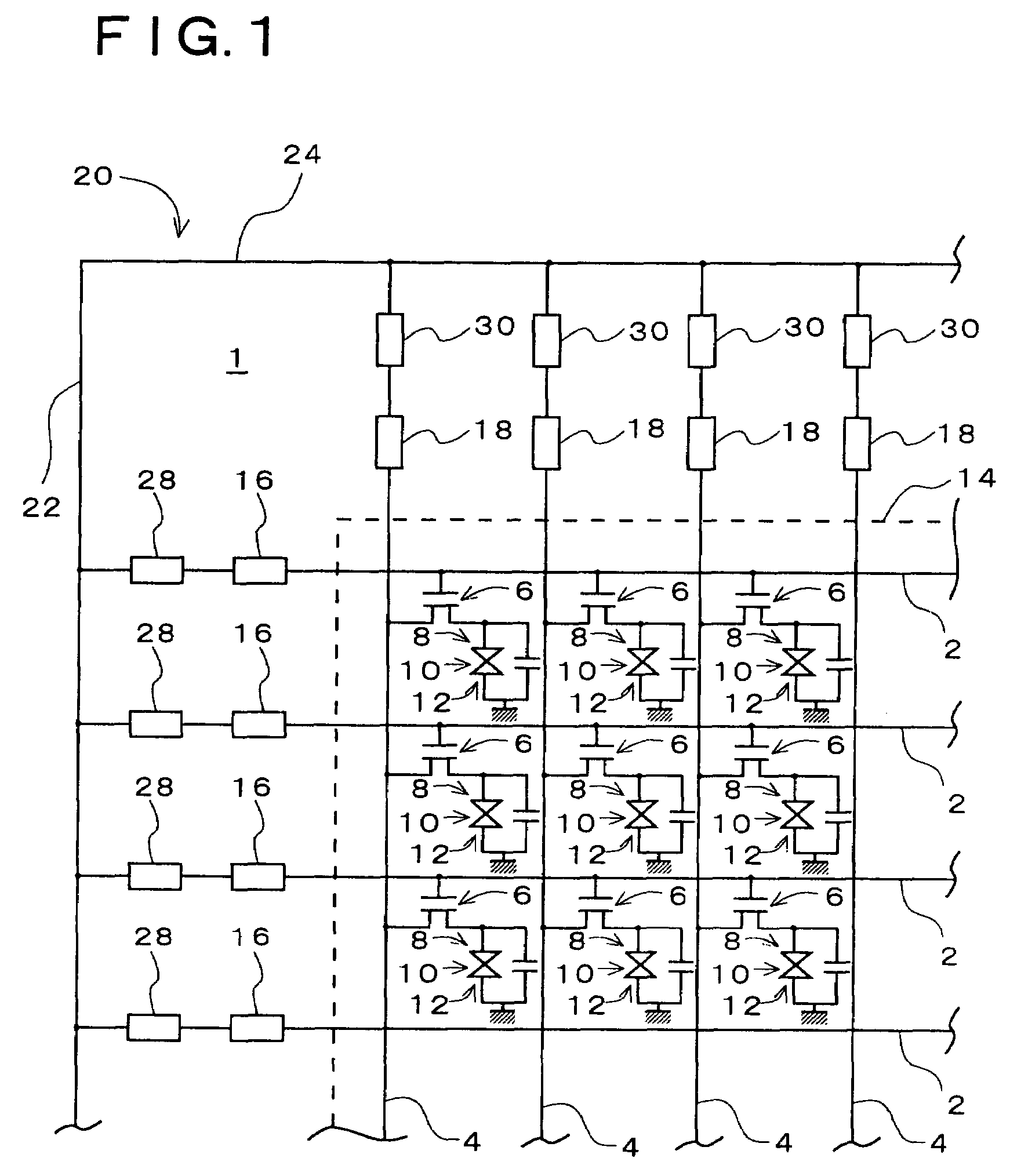

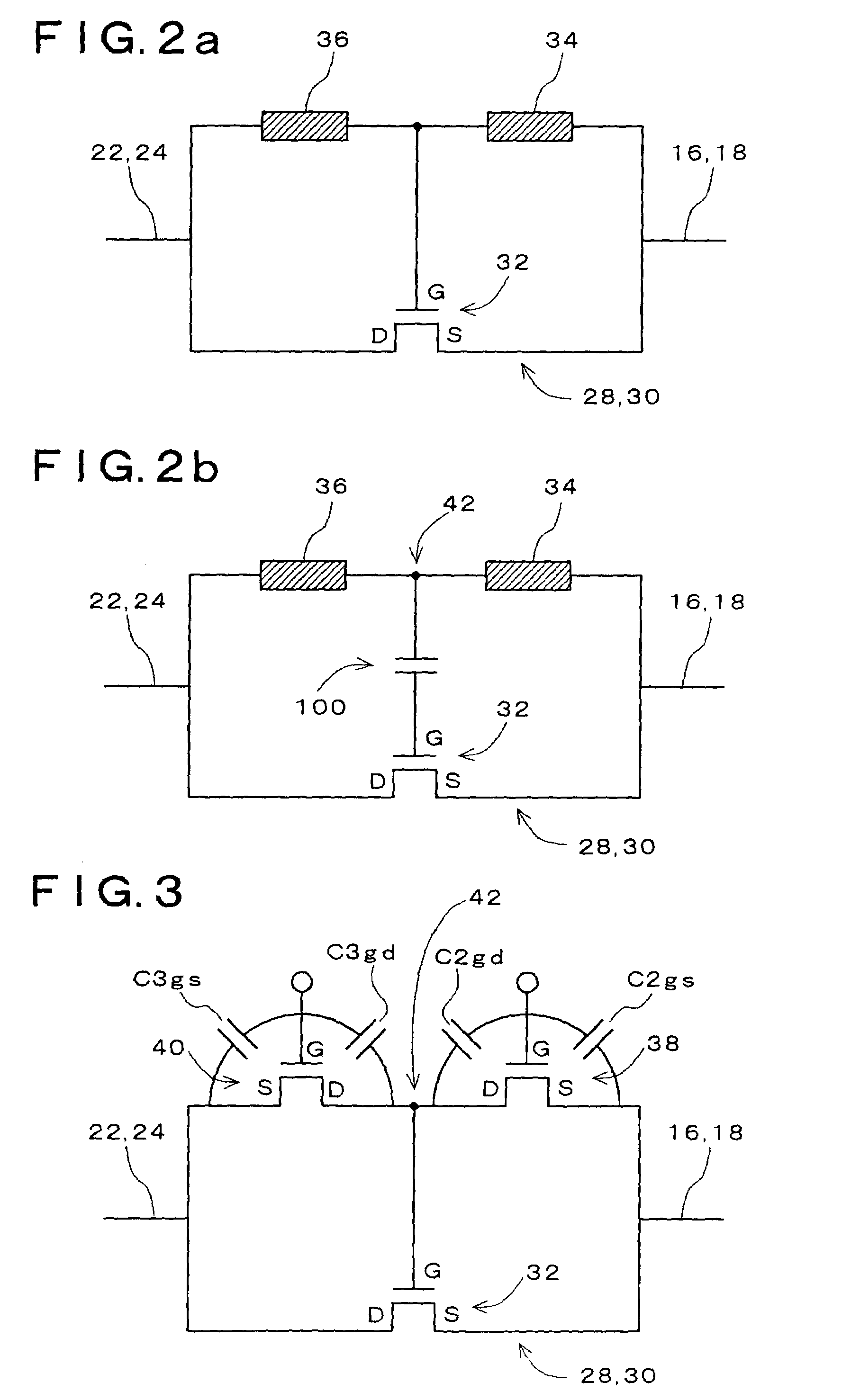

The present invention relates to a liquid crystal display provided with an electrostatic protection element and an object of the present invention is to provide the liquid crystal display provided with superior redundancy and at the same time a sufficient protection function against static electricity in which relatively low voltage generates for a long period of time. Electrostatic protection element sections 28 and 30 are provided with a first TFT 32 having a source electrode (S) and a drain electrode (D) where the source electrode (S) is connected to external output electrodes 16 and 18 and the drain electrode (D) is connected to common wirings 22 and 24, a second TFT 38 having a conductor 42, a source electrode (S), a drain electrode (D) and a gate electrode (G) where the conductor 42 is connected to the gate electrode (G) of the first TFT 32, the source electrode (S) is connected to the external output electrodes 16 and 18, the drain electrode (D) is connected to the conductor 42 and the gate electrode (G) is electrically floated, and a third TFT 40 having a source electrode (S), a drain electrode (D) and a gate electrode (G) where the source electrode (S) is connected to the common wirings 22 and 24, the drain electrode (D) is connected to the conductor 42 and the gate electrode is electrically floated.

Owner:SHARP KK

Liquid crystal display comprising an electrostatic protection element formed between adjacent bus lines

InactiveUS7342617B2Solve the lack of functionNot disadvantageous in of controllingNon-linear opticsElectrical conductorLiquid-crystal display

The present invention relates to a liquid crystal display provided with an electrostatic protection element and an object of the present invention is to provide the liquid crystal display provided with superior redundancy and at the same time a sufficient protection function against static electricity in which relatively low voltage generates for a long period of time. Electrostatic protection element sections 28 and 30 are provided with a first TFT 32 having a source electrode (S) and a drain electrode (D) where the source electrode (S) is connected to external output electrodes 16 and 18 and the drain electrode (D) is connected to common wirings 22 and 24, a second TFT 38 having a conductor 42, a source electrode (S), a drain electrode (D) and a gate electrode (G) where the conductor 42 is connected to the gate electrode (G) of the first TFT 32, the source electrode (S) is connected to the external output electrodes 16 and 18, the drain electrode (D) is connected to the conductor 42 and the gate electrode (G) is electrically floated, and a third TFT 40 having a source electrode (S), a drain electrode (D) and a gate electrode (G) where the source electrode (S) is connected to the common wirings 22 and 24, the drain electrode (D) is connected to the conductor 42 and the gate electrode is electrically floated.

Owner:SHARP KK

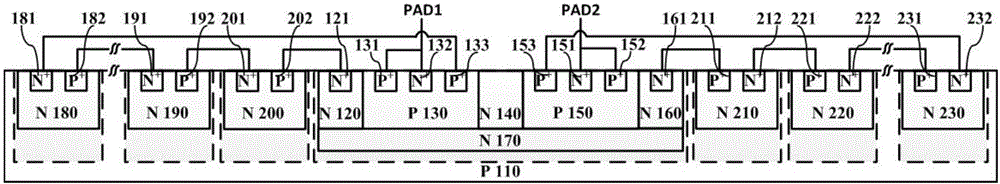

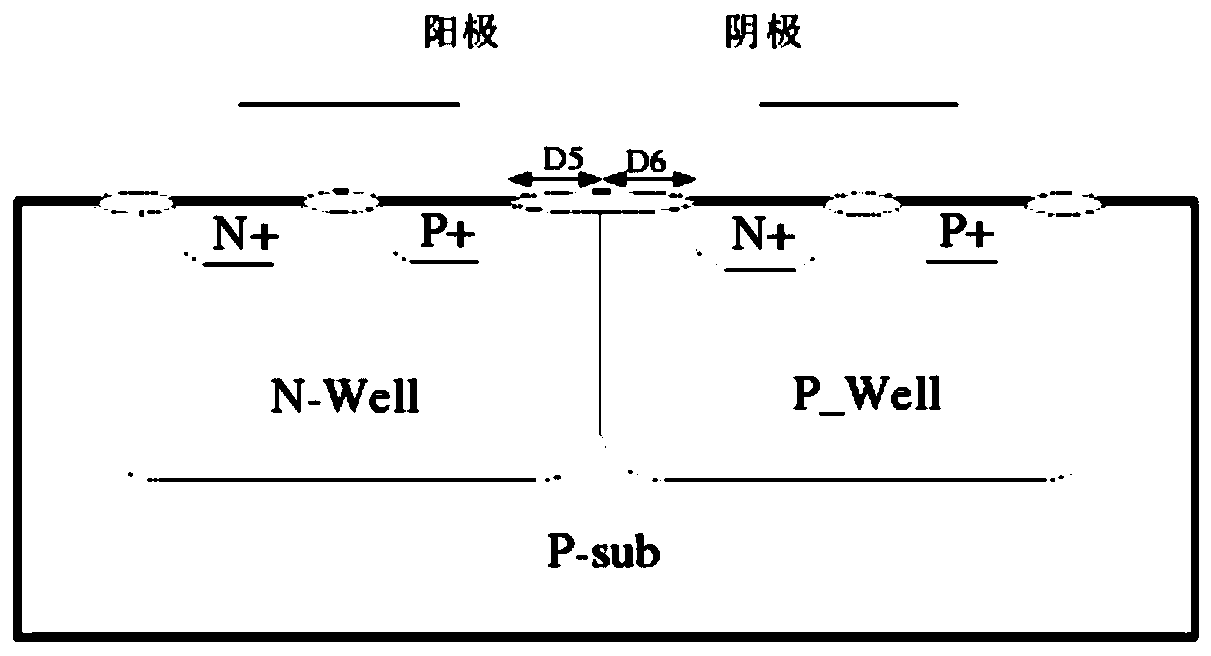

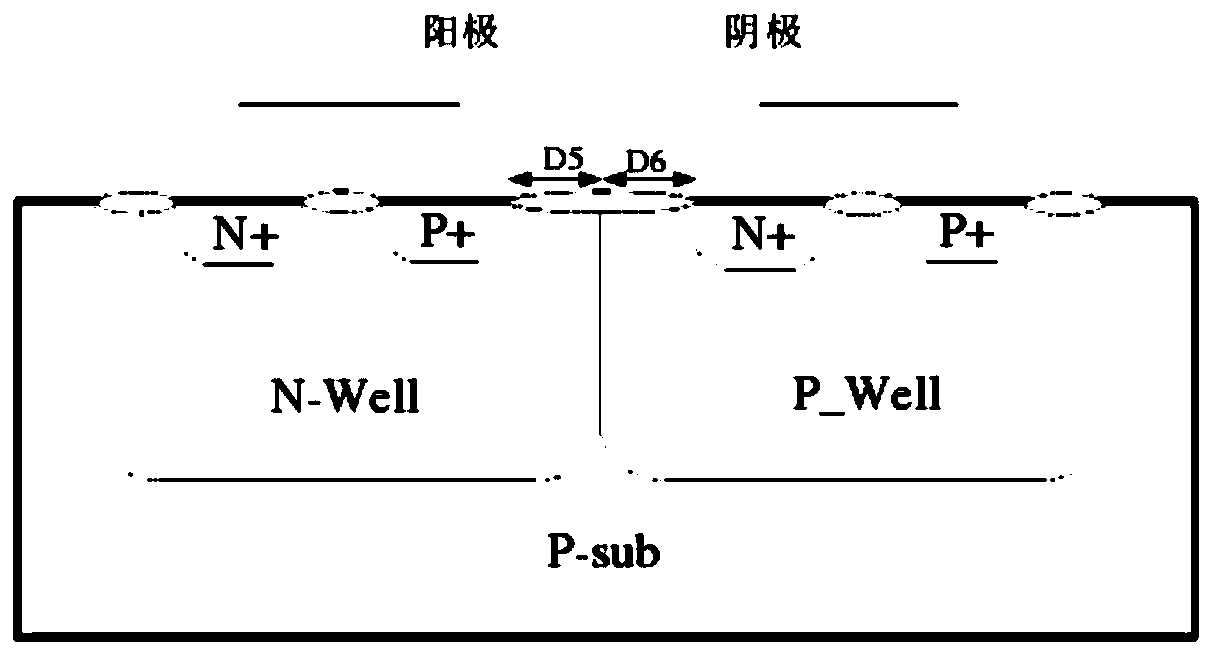

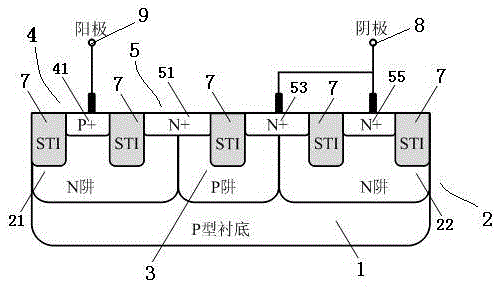

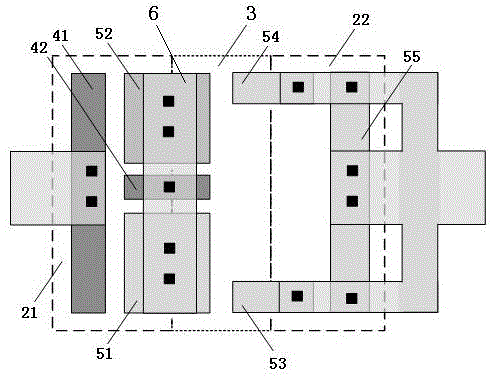

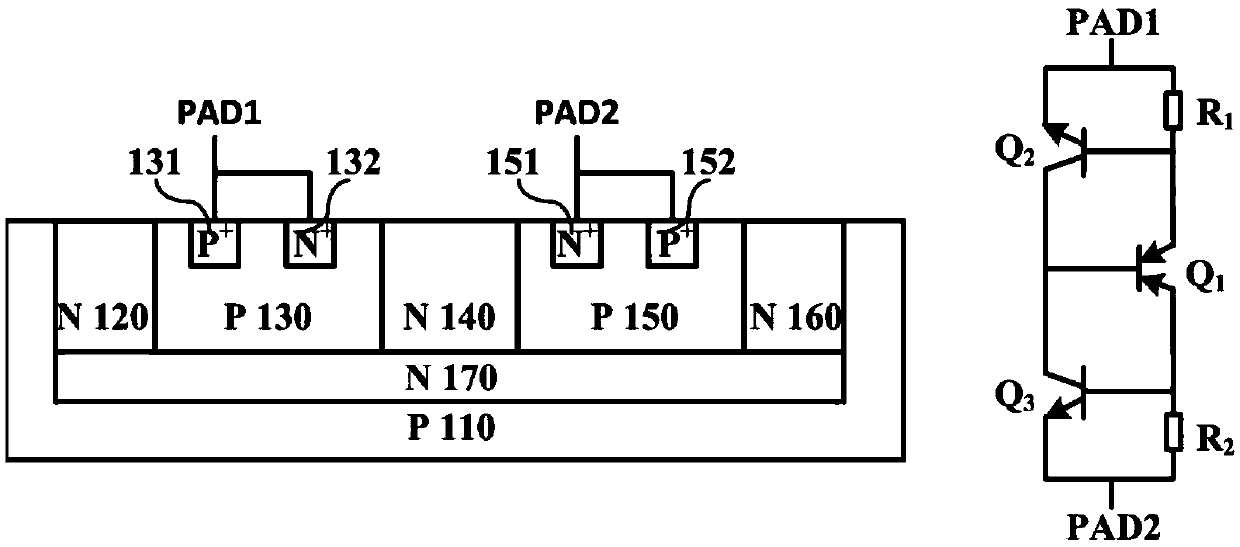

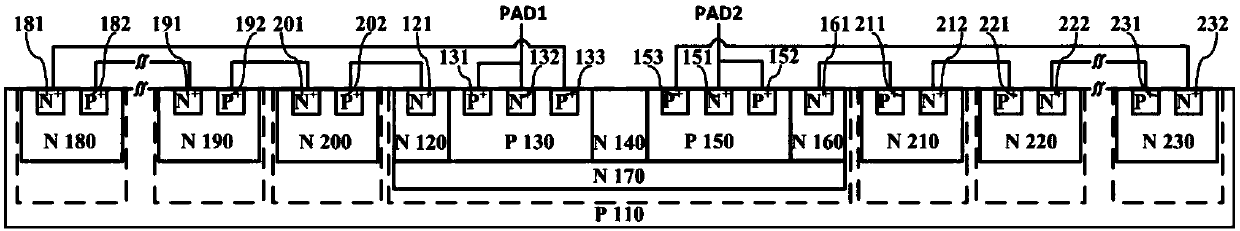

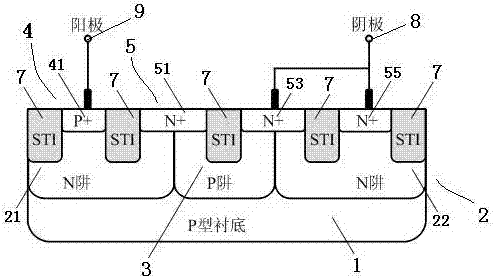

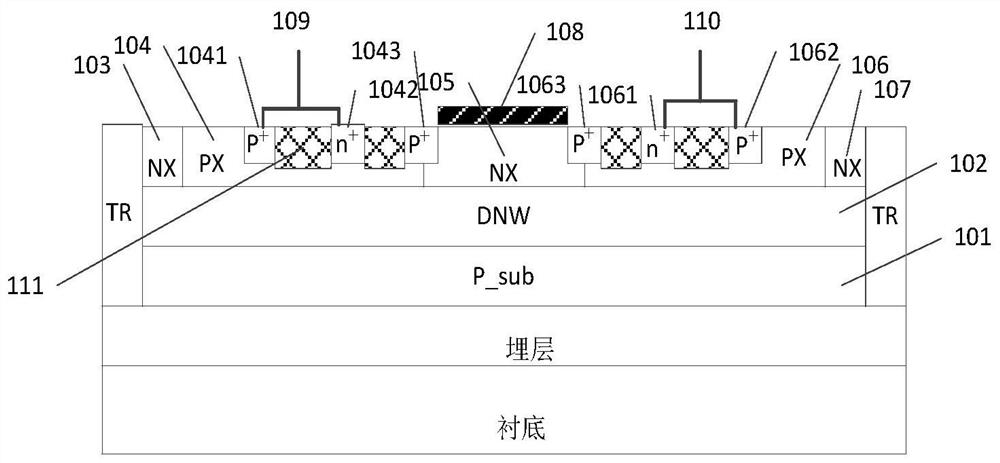

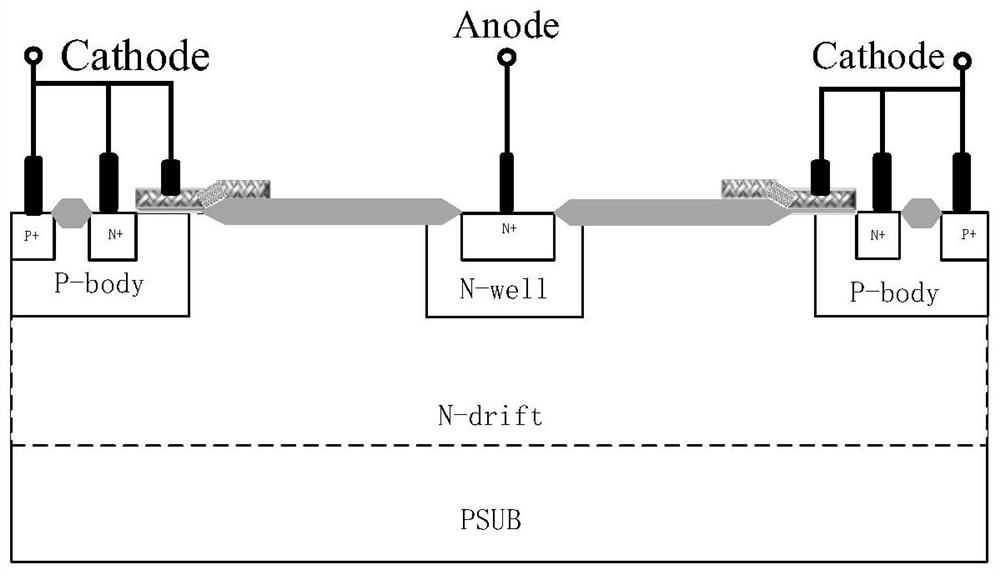

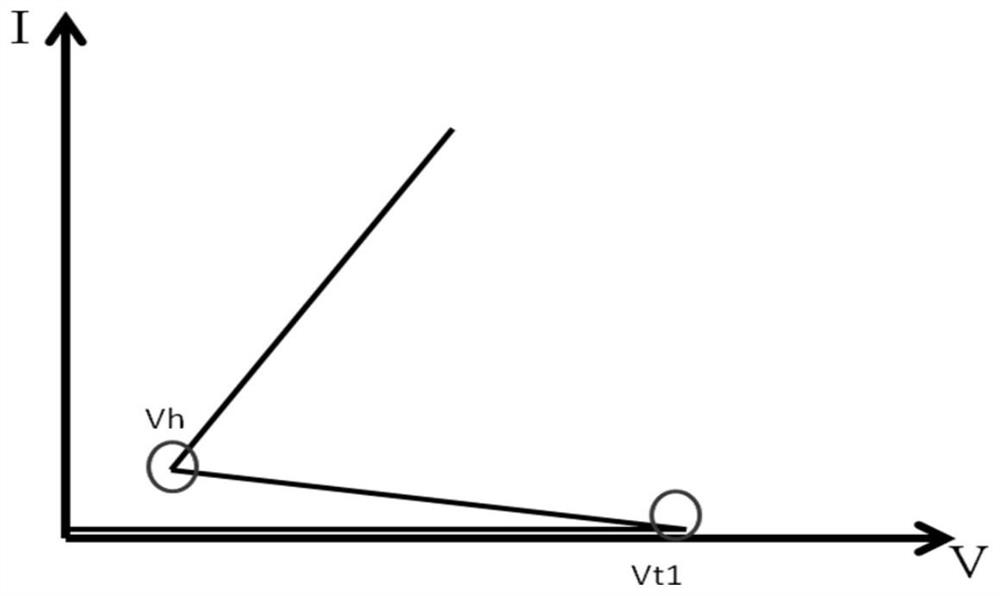

Low-trigger voltage bidirectional SCR device based on buried layer trigger

ActiveCN106206569AOpen fastEffective electrostatic protectionSolid-state devicesDiodeIsolation effectLow voltage

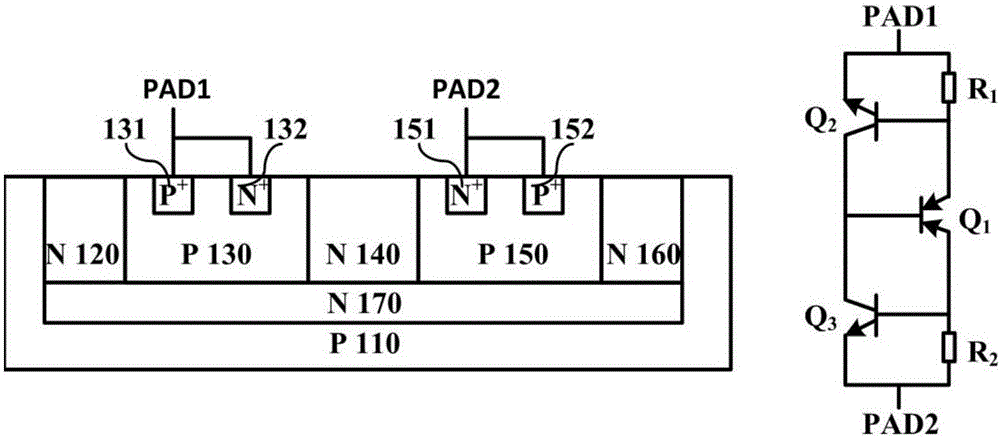

The invention belongs to the technical field of electronics, and provides a low-trigger voltage bidirectional SCR device based on buried layer trigger for lowering the trigger voltage of the bidirectional SCR device. The bidirectional SCR device is composed of one main device, n trigger devices and m trigger devices at two sides of the main device; the trigger device is a diode device, and the adjacent trigger devices are connected in series; a first conductive type heavily-doped region is respectively arranged in each of the first conductive type well region A and the first conductive type well region C in the bidirectional SCR structure through the main device, a closed first conductive type heavily-doped buried layer only with the isolation effect in the basic bidirectional SCR is connected with the trigger diode strings out of two sides to form a low-voltage trigger channel with the buried layer and the diode strings, thereby lowering the trigger voltage of the bidirectional SCR device; and meanwhile, the trigger voltage is adjustable through the adjustment of the number of the trigger device; the starting speed of the device is effectively improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

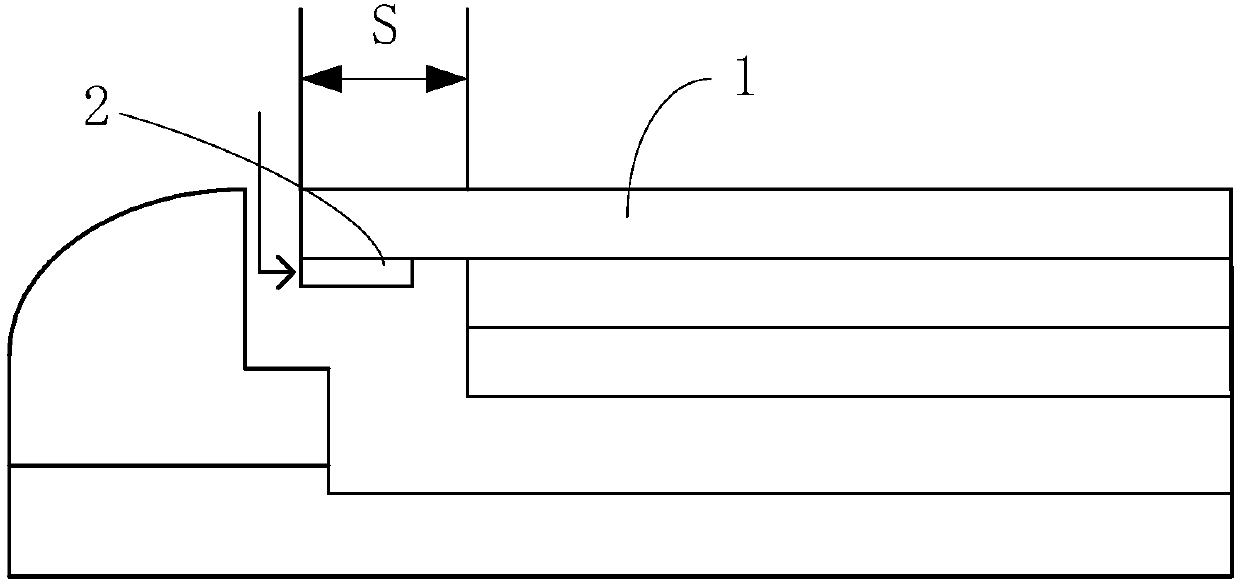

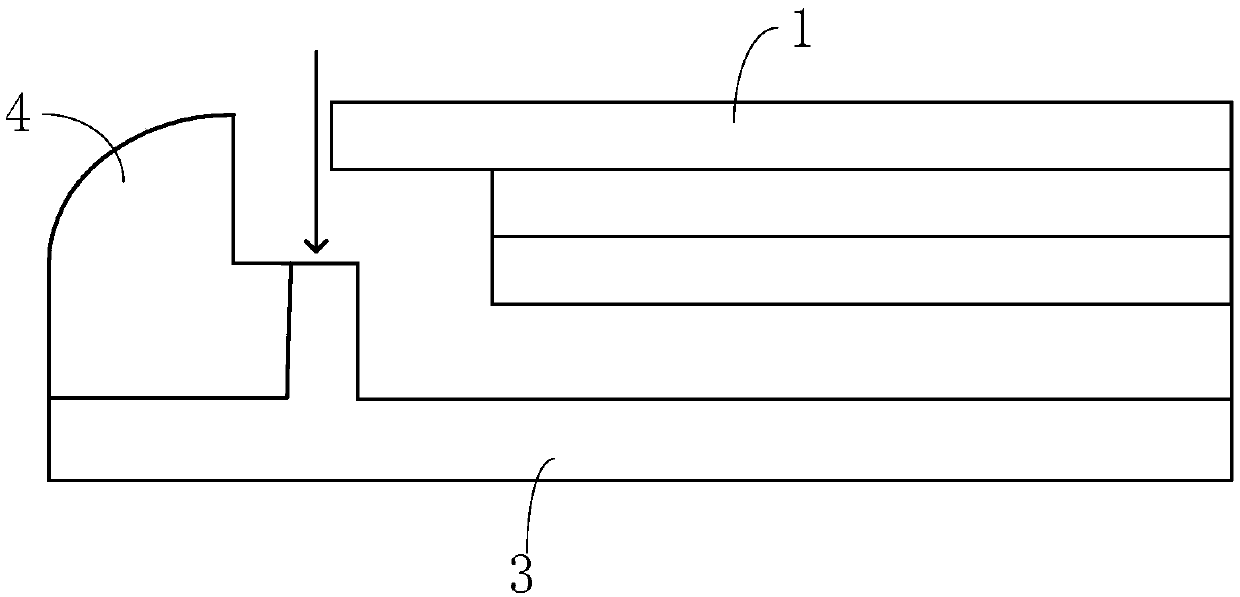

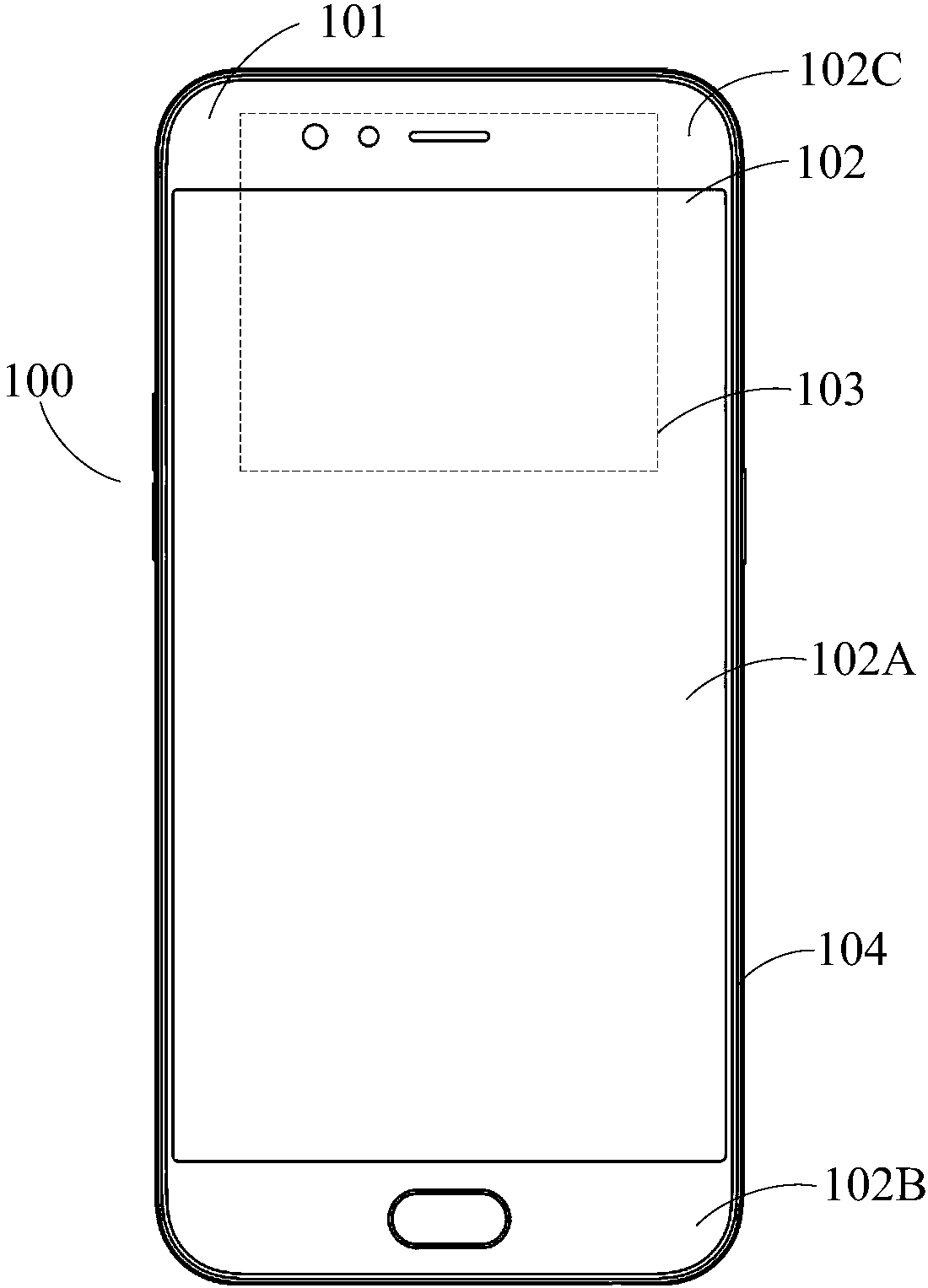

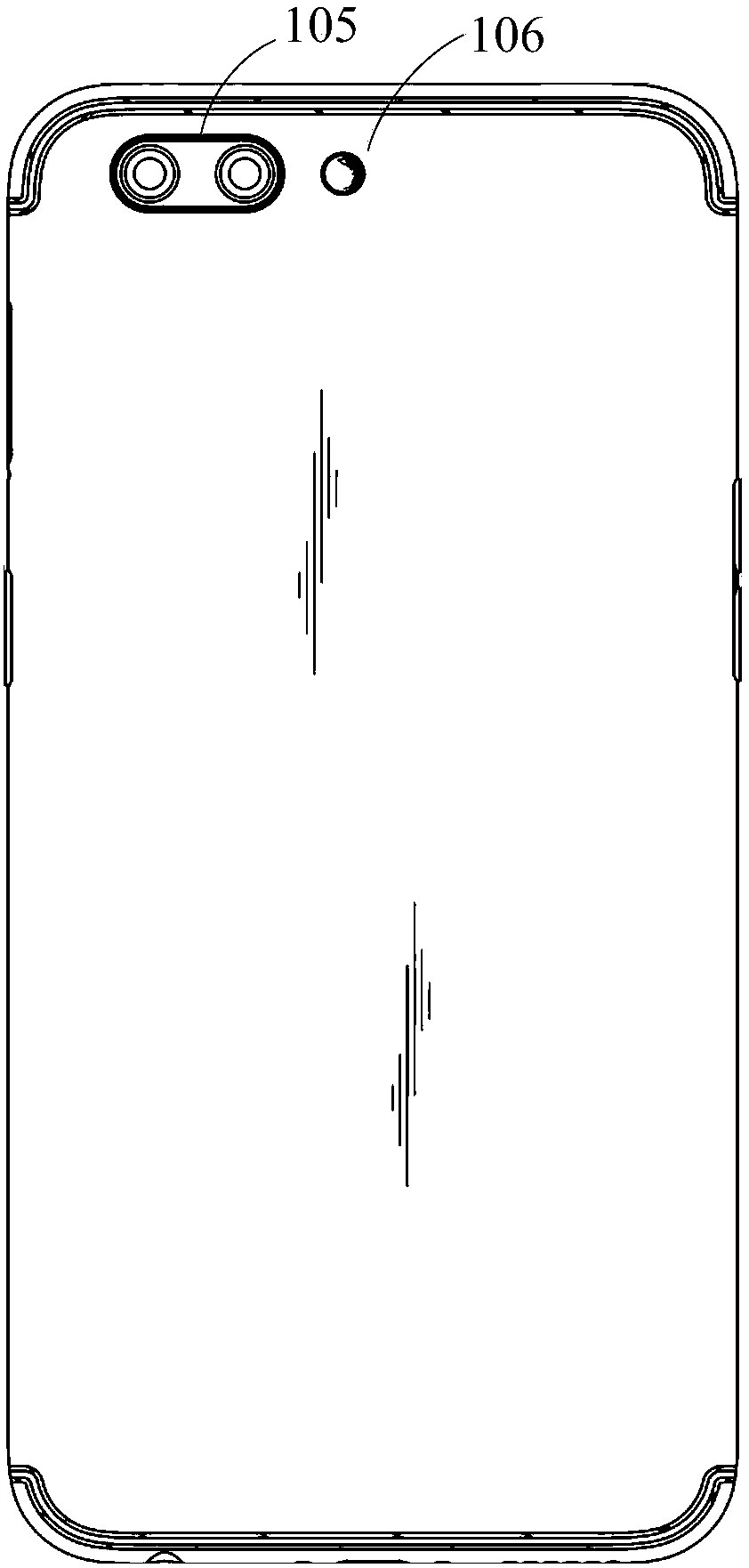

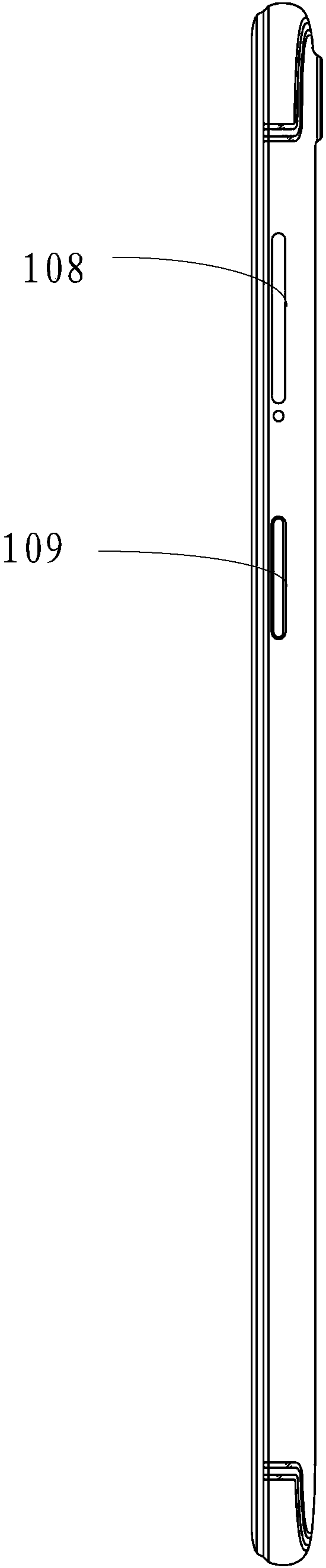

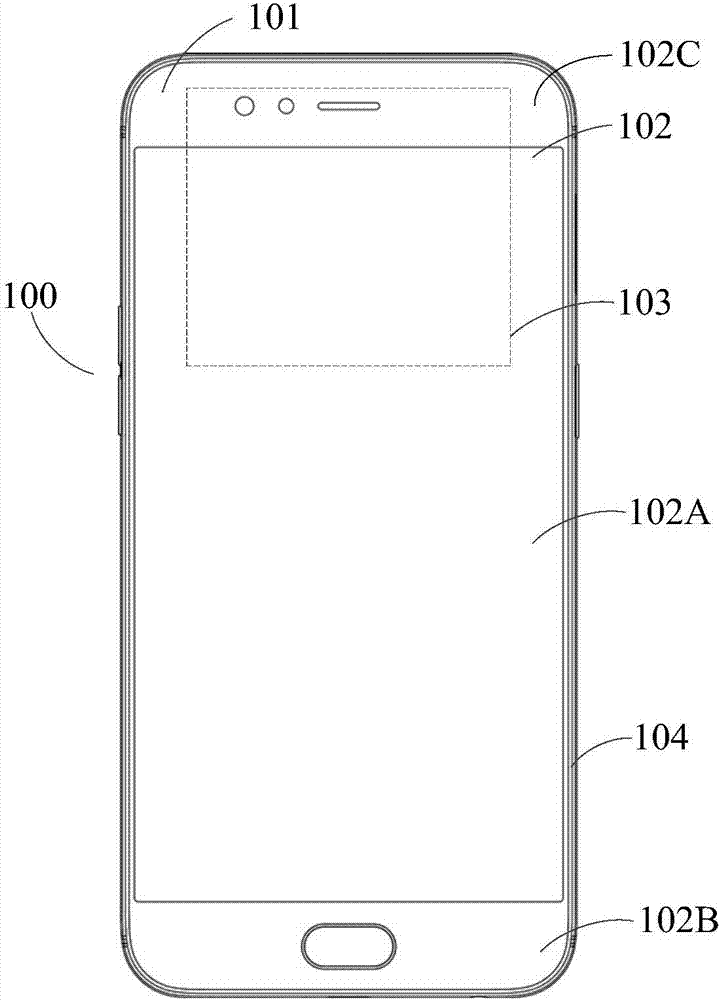

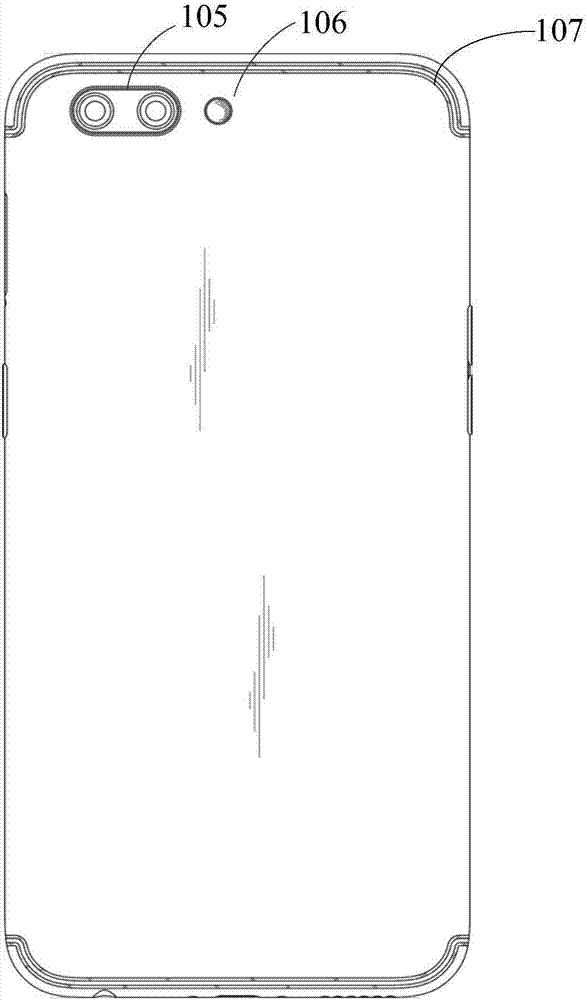

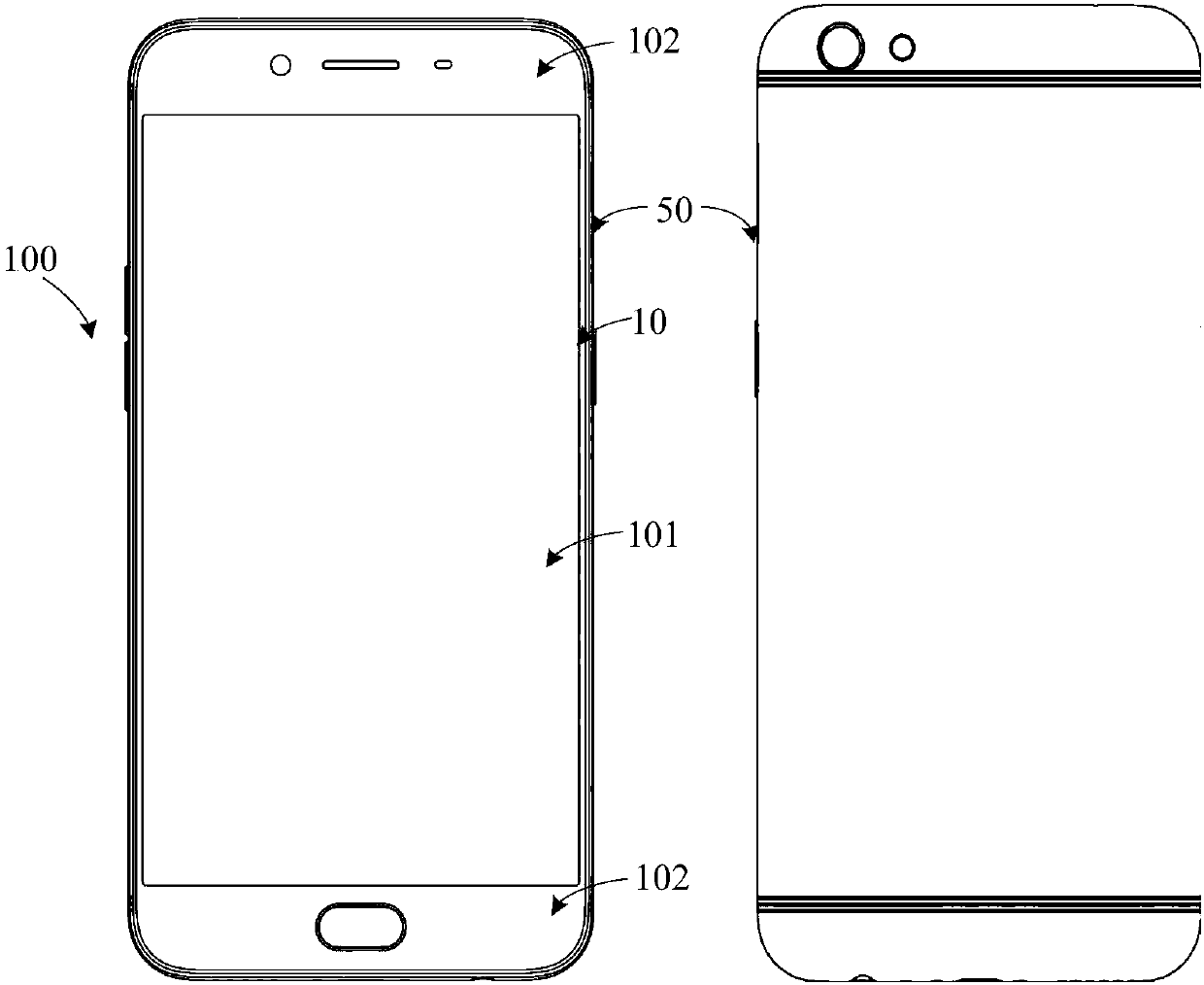

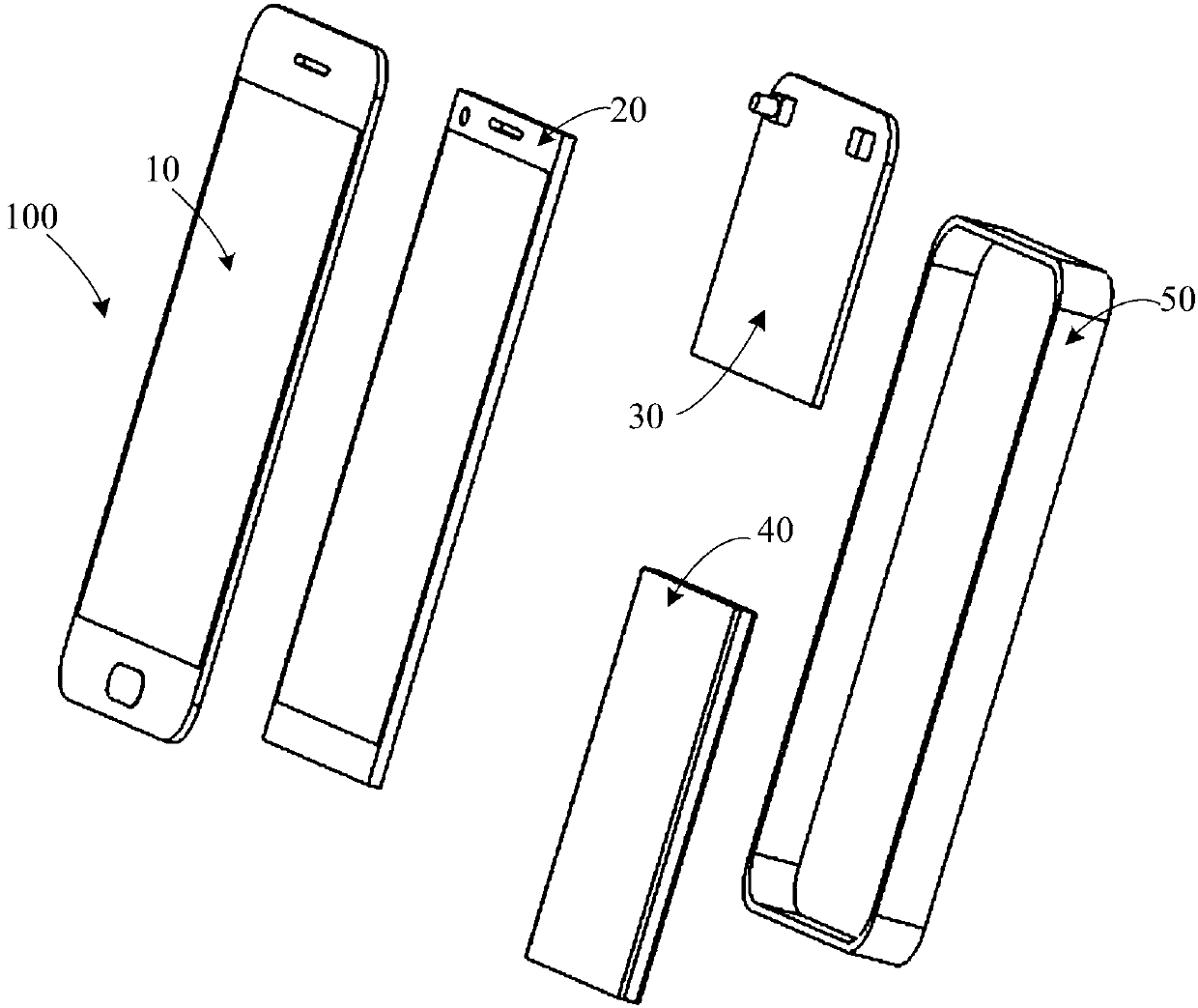

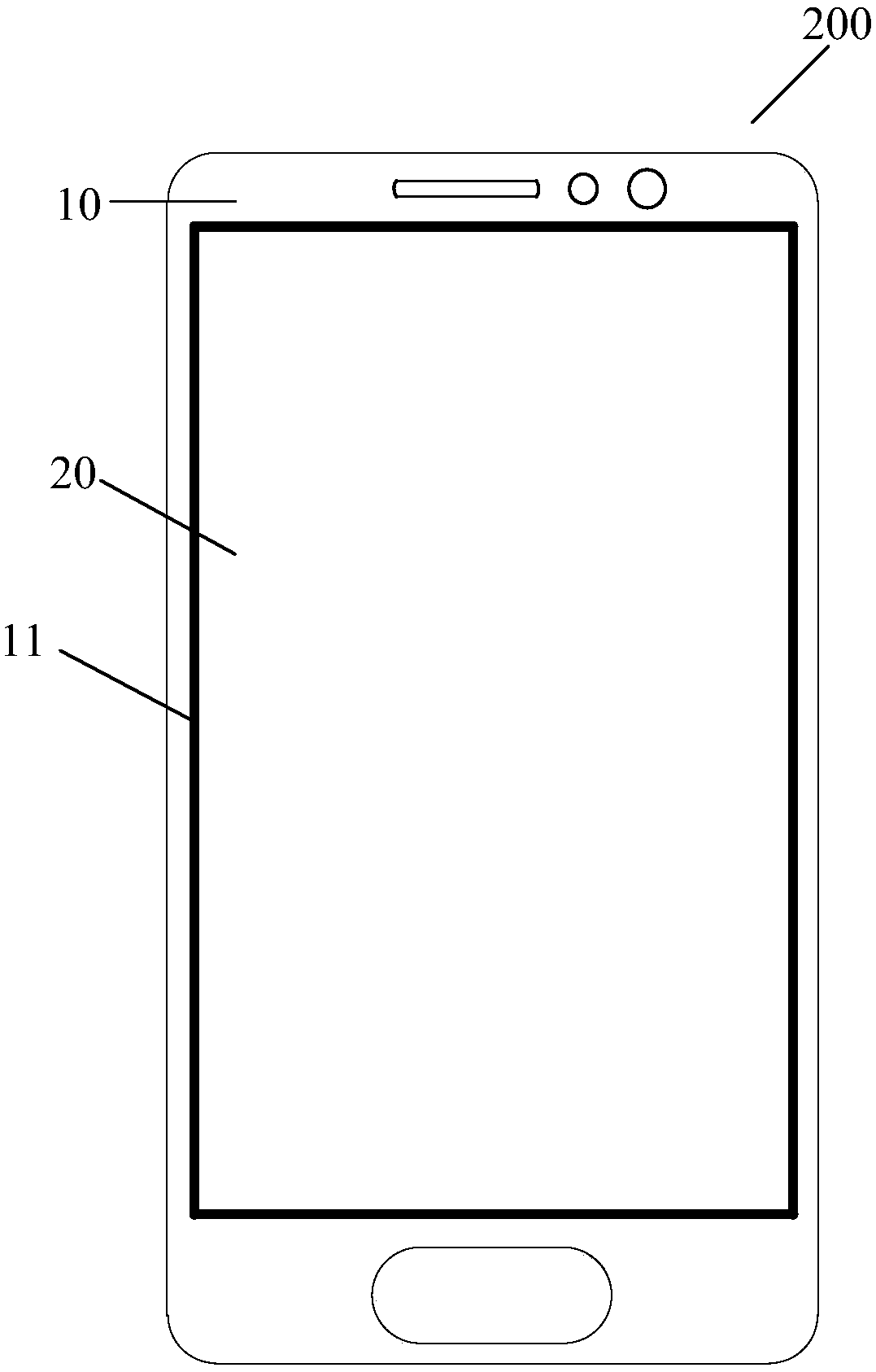

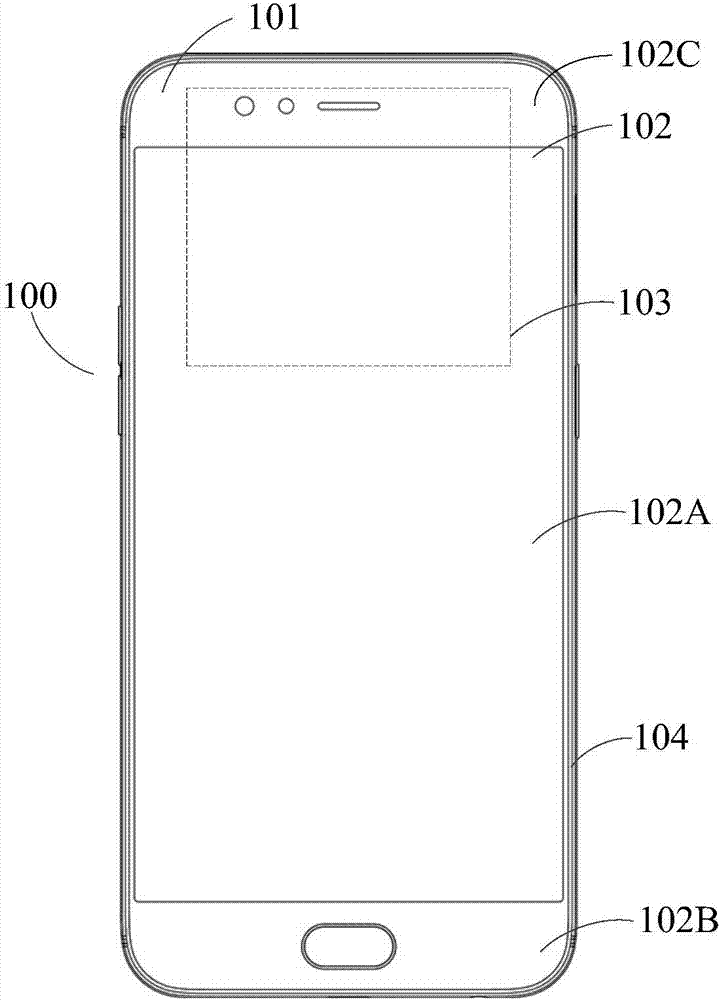

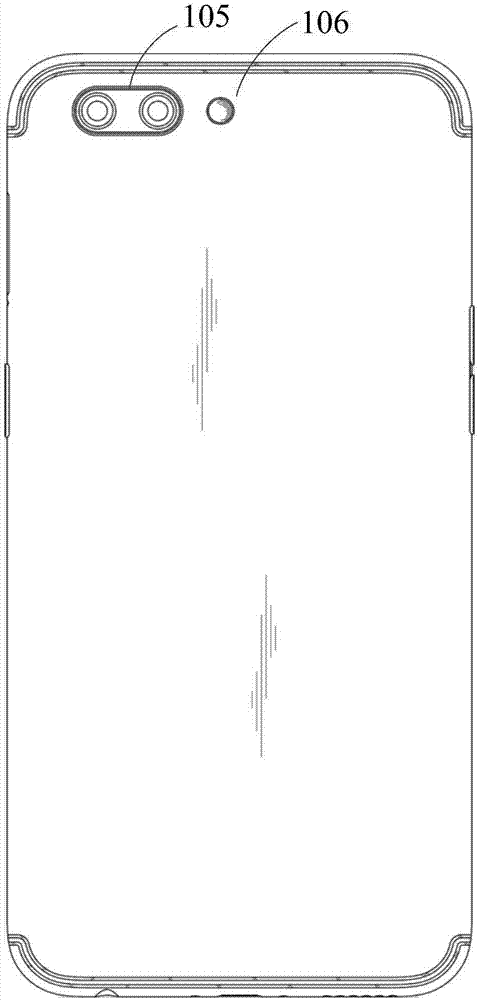

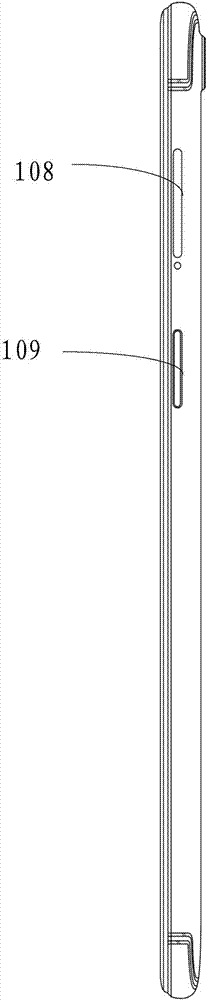

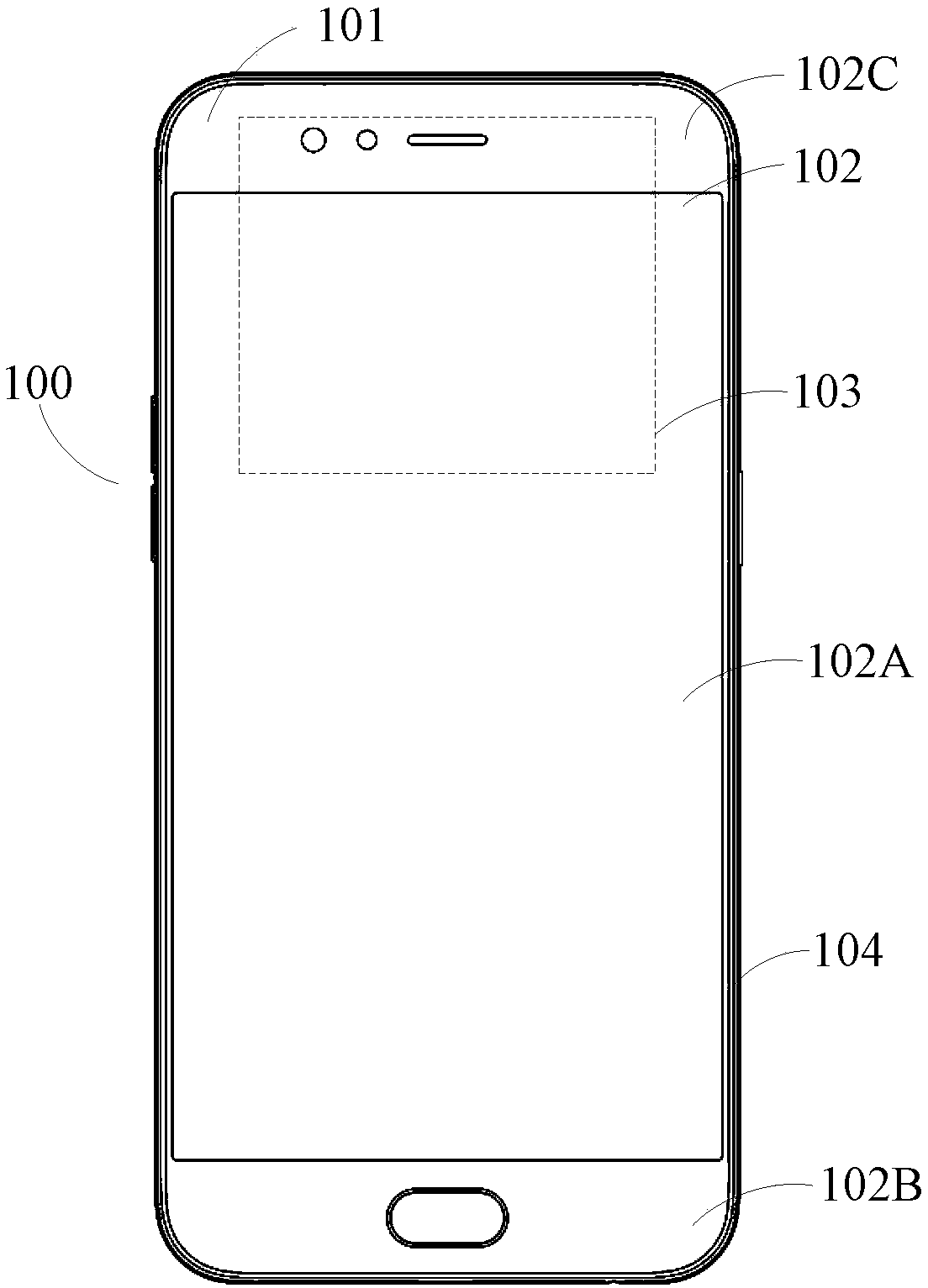

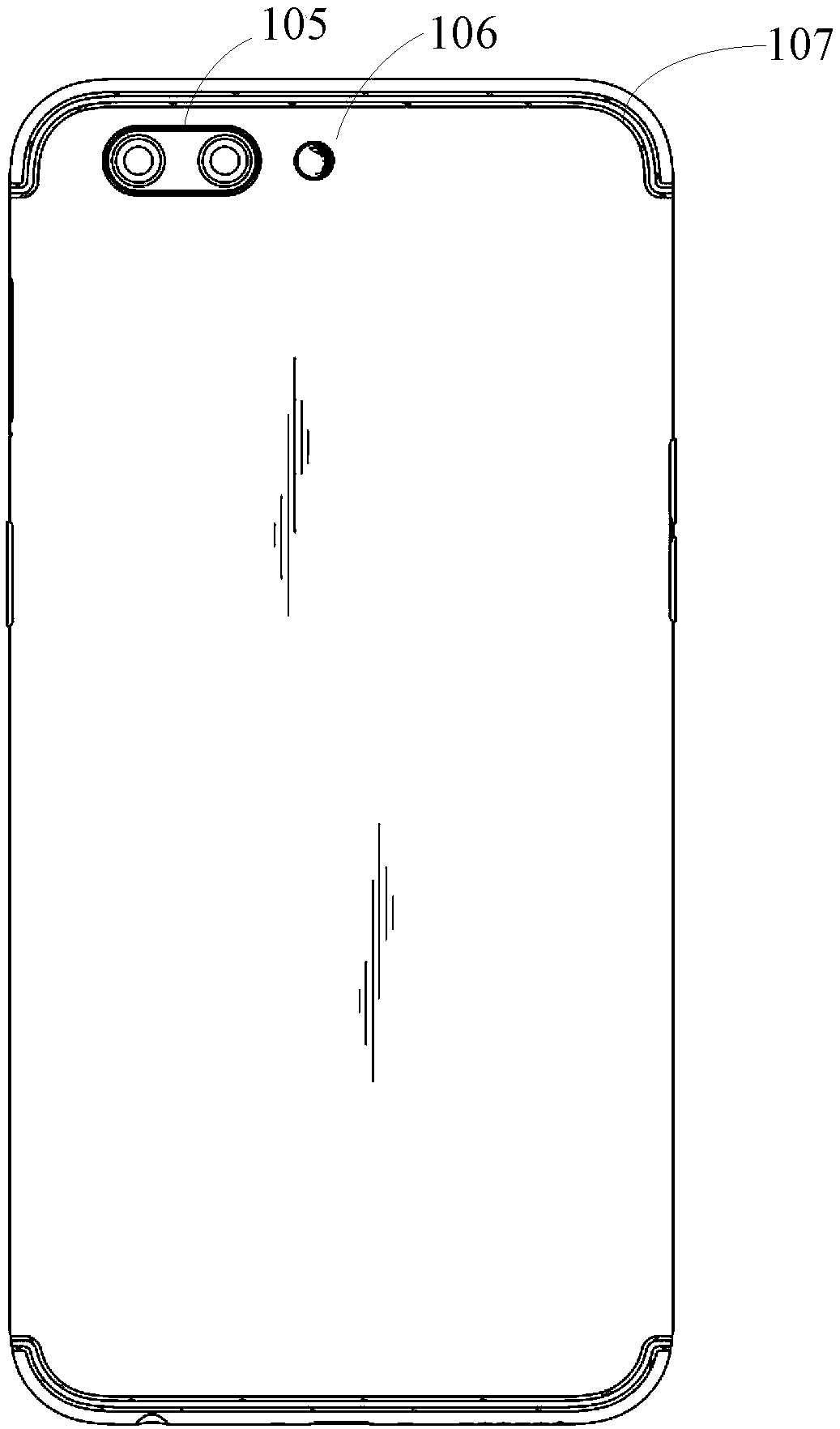

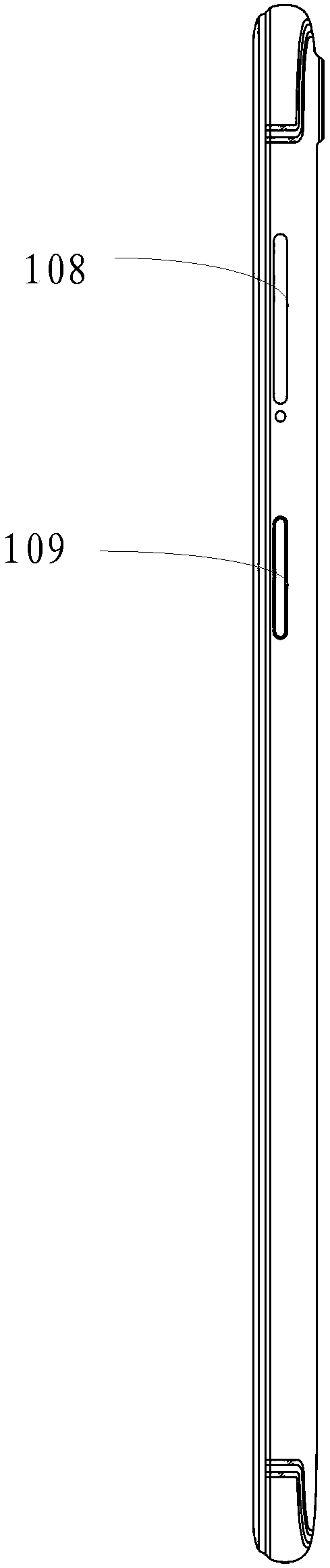

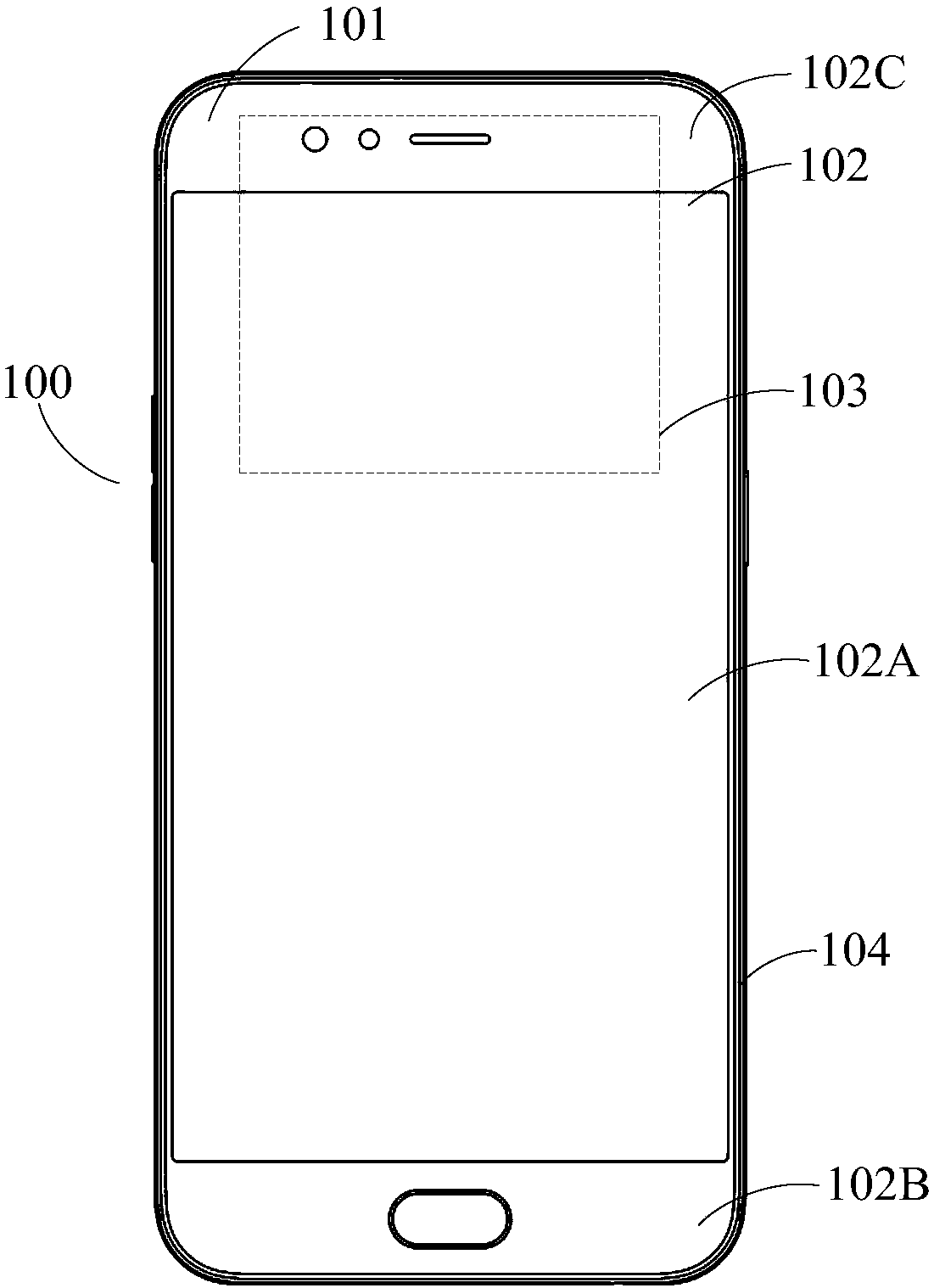

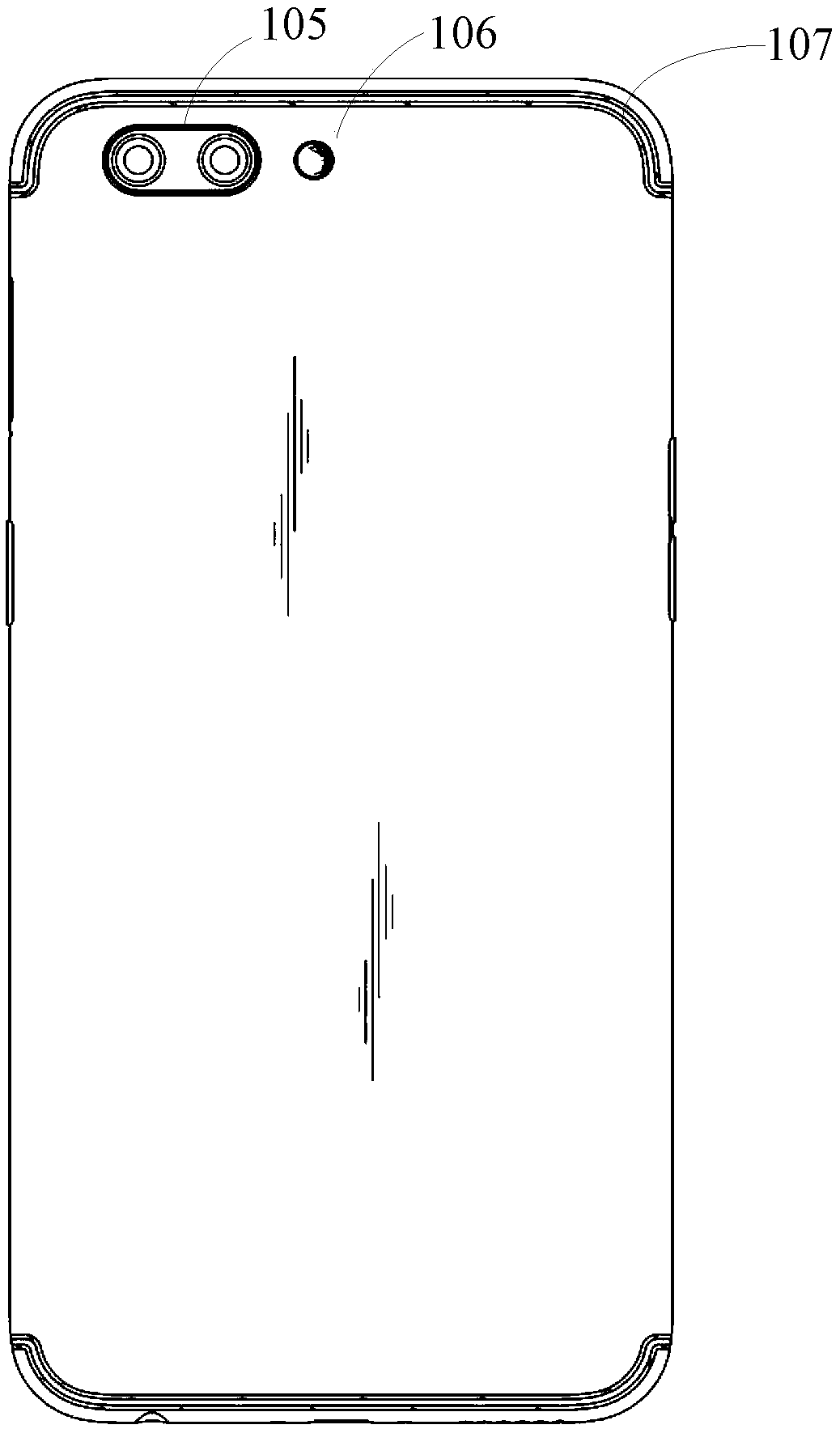

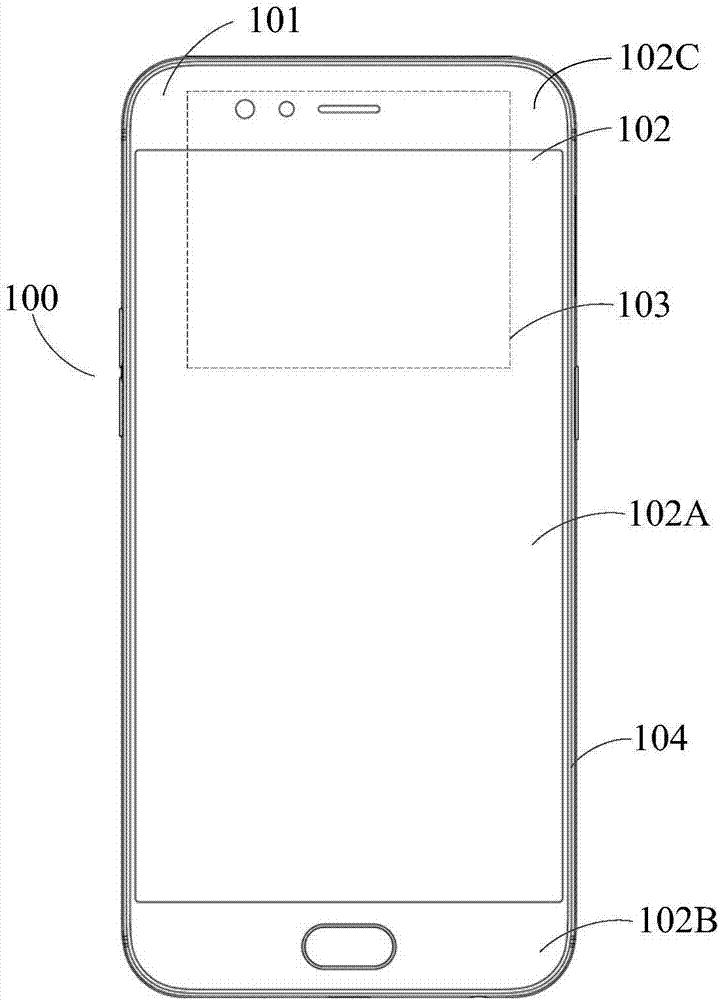

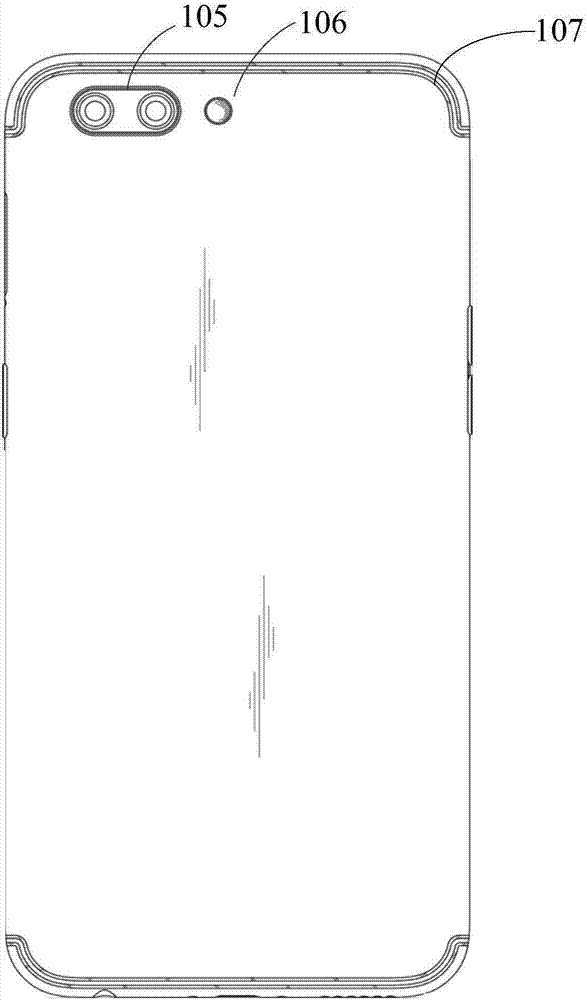

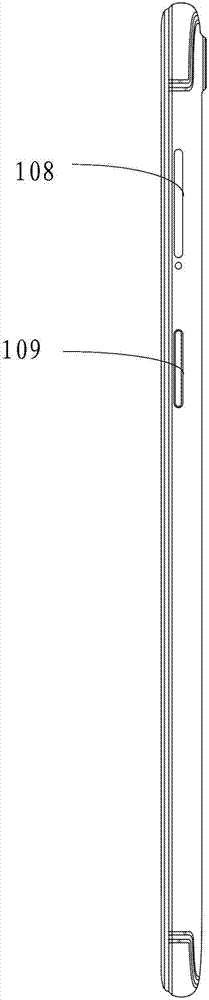

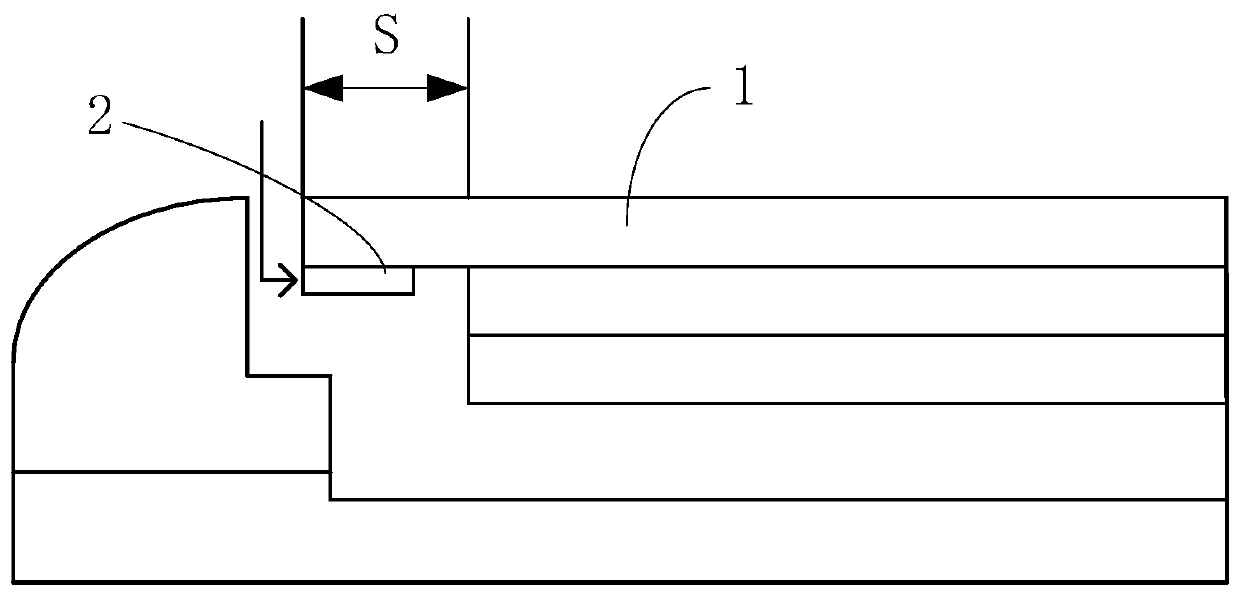

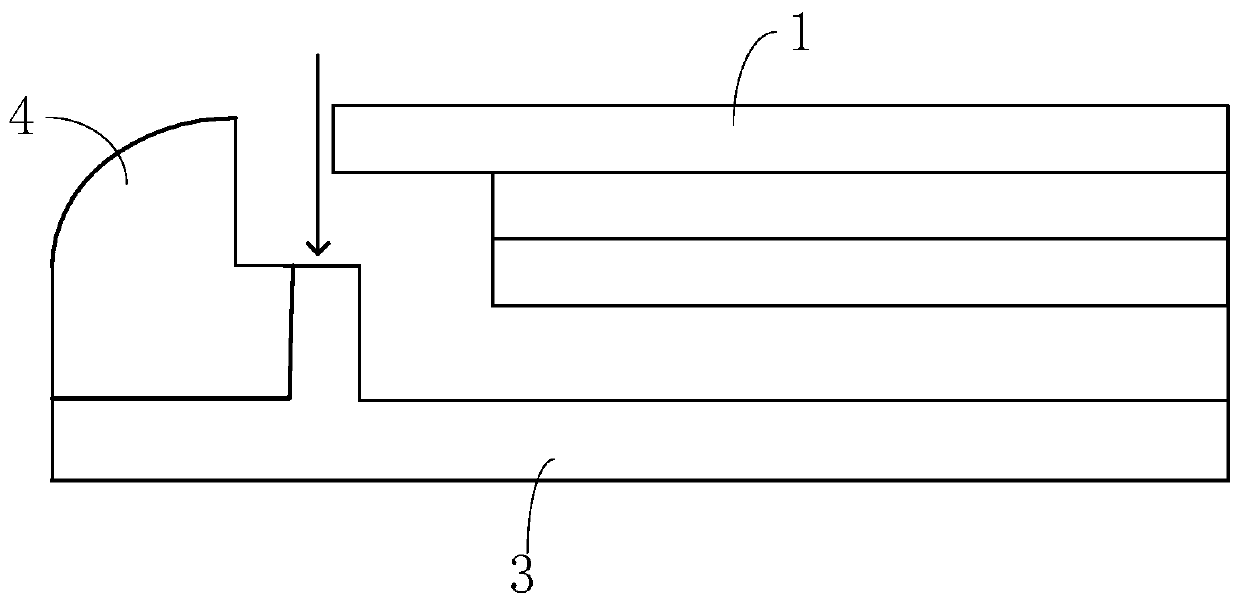

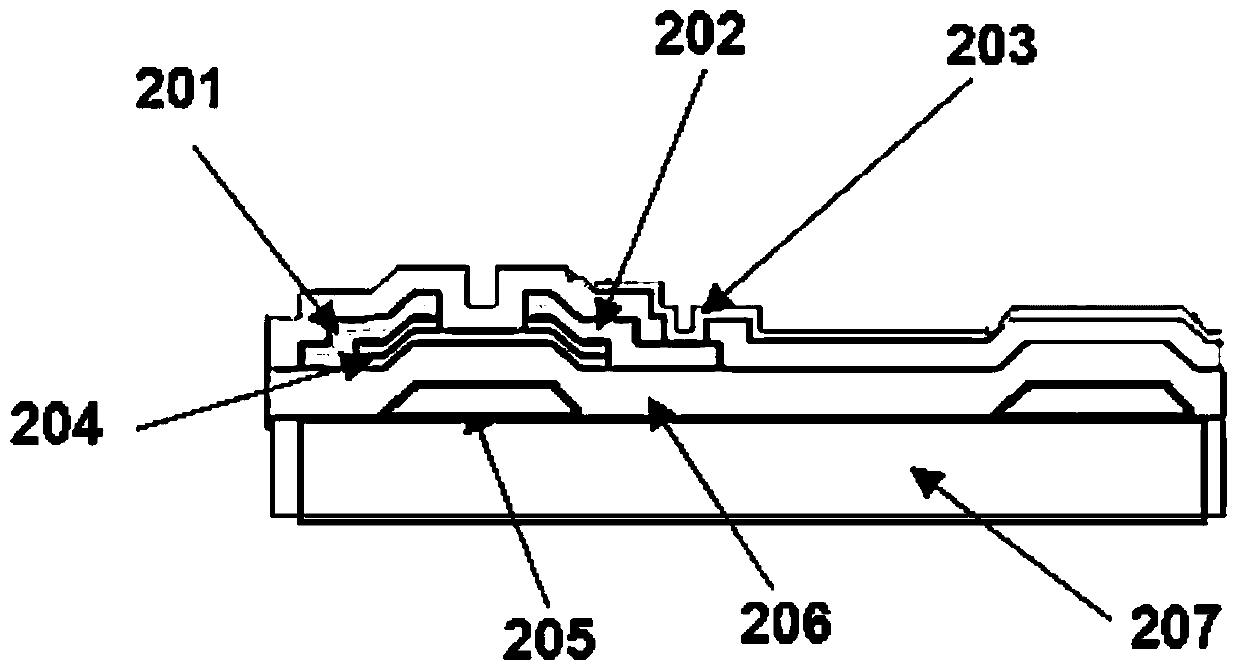

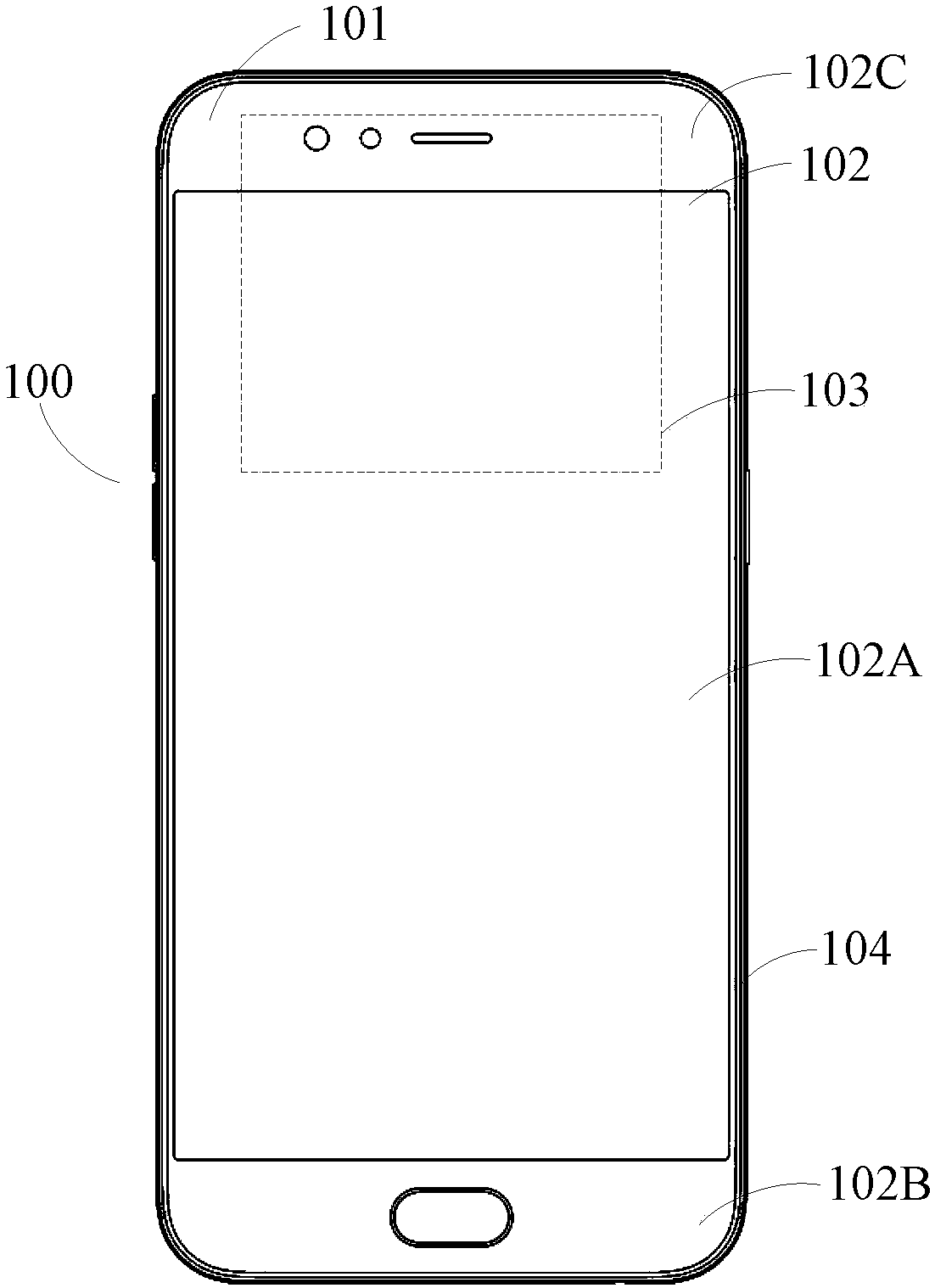

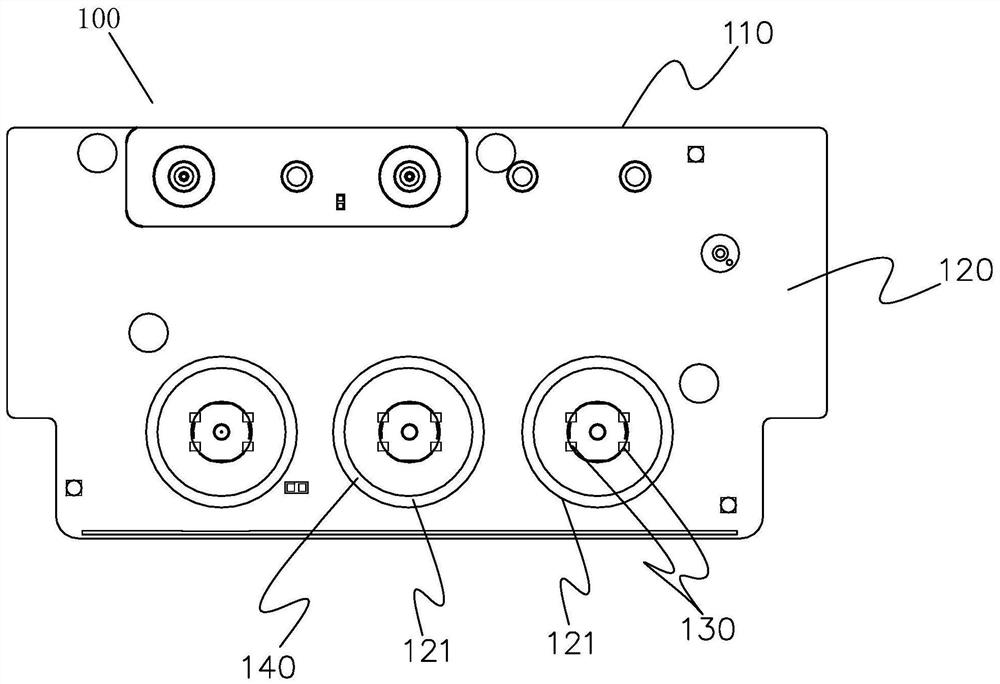

Terminal device

ActiveCN108023978AEffective electrostatic protectionEnsure the consistency of electrostatic protectionTelephone set constructionsTerminal equipmentComputer terminal

The object of the invention is to provide a terminal device. The terminal device comprises a screen module; a bracket disposed on the periphery of the screen module; and a grounded metal middle framelocated on one side of the back face of the screen module; an inner side face of the bracket is a metal surface, and a gap is reversed between the inner surface of the bracket and the metal middle frame; and electrostatic protection structure is arranged between the metal surface of the bracket and the metal middle frame, and the electrostatic protection structure can enable electrostatic conduction between the metal surface of the bracket and the metal middle frame. The electrostatic problem on the side edge of the screen module can be effectively solved, an effective electrostatic protectionfunction can be performed on the side edges of the screen module, and the antenna performance is ensured.

Owner:VIVO MOBILE COMM CO LTD

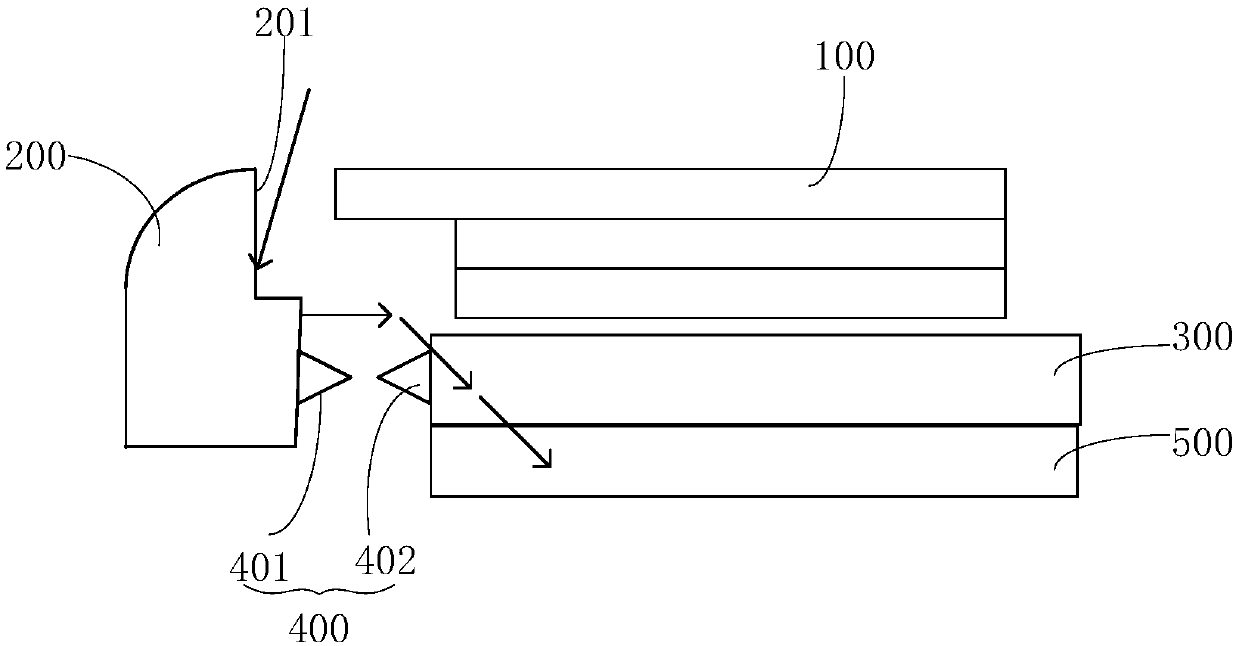

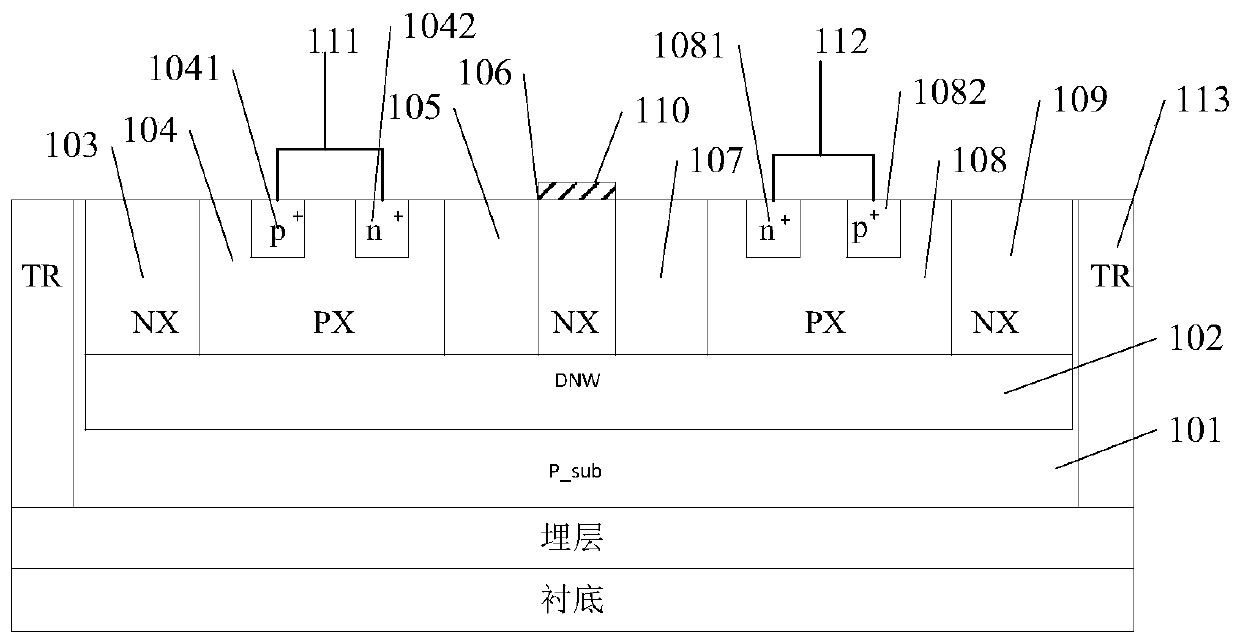

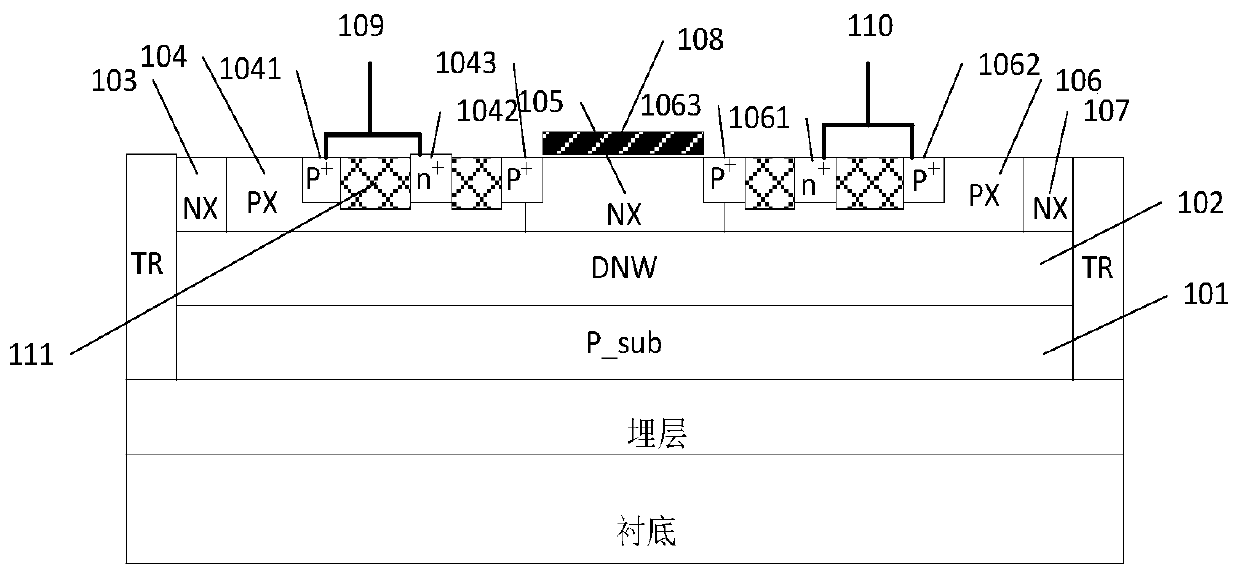

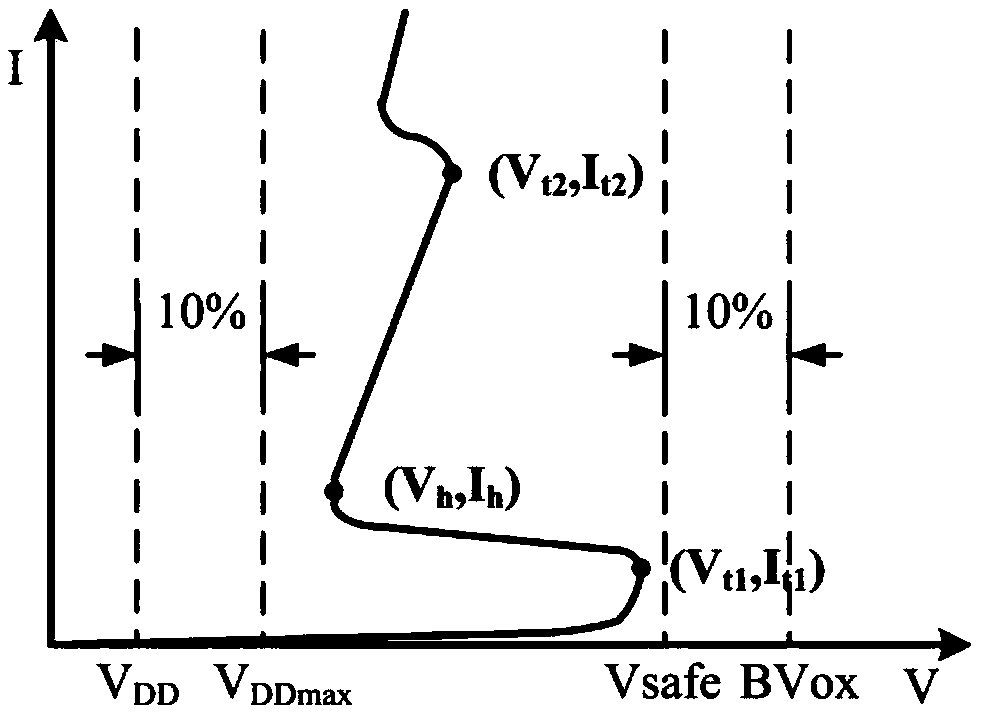

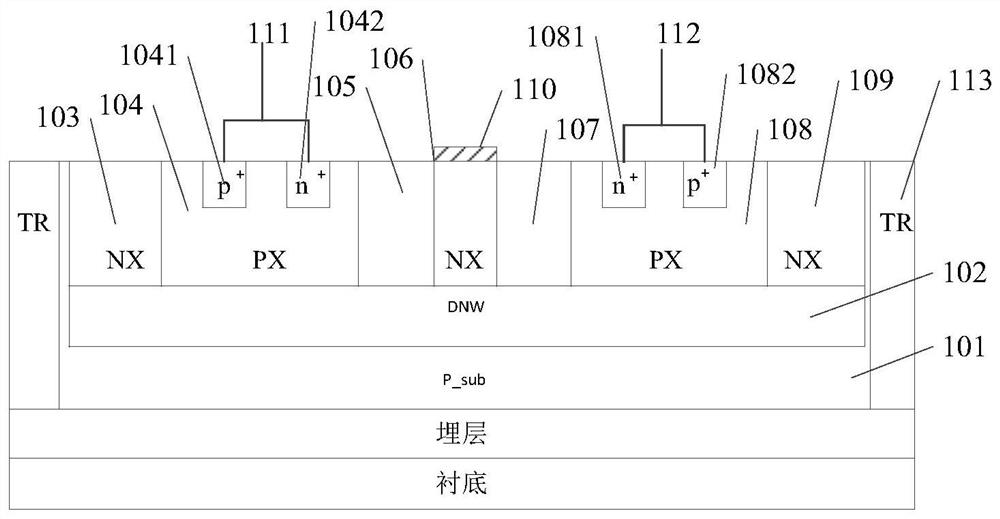

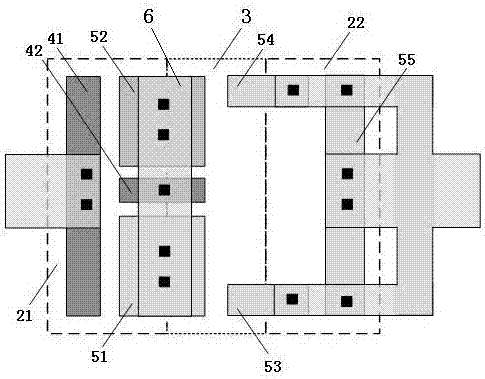

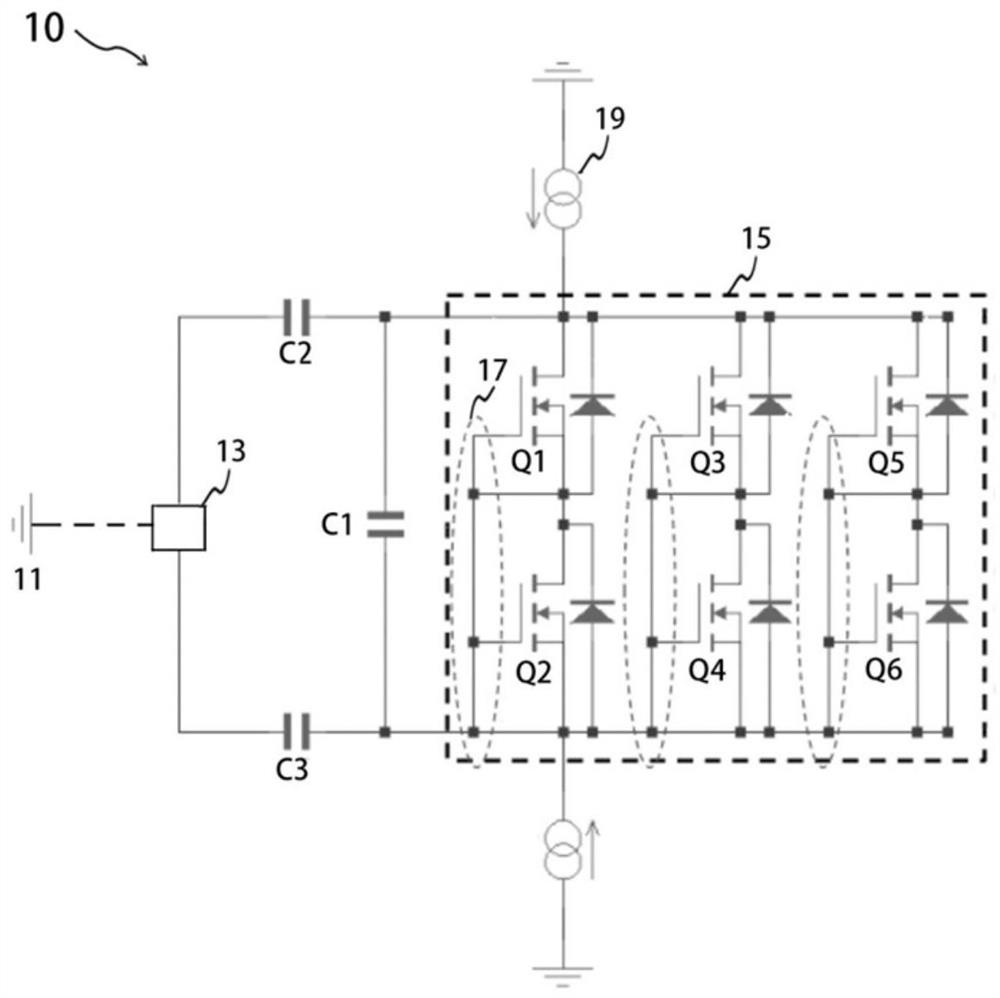

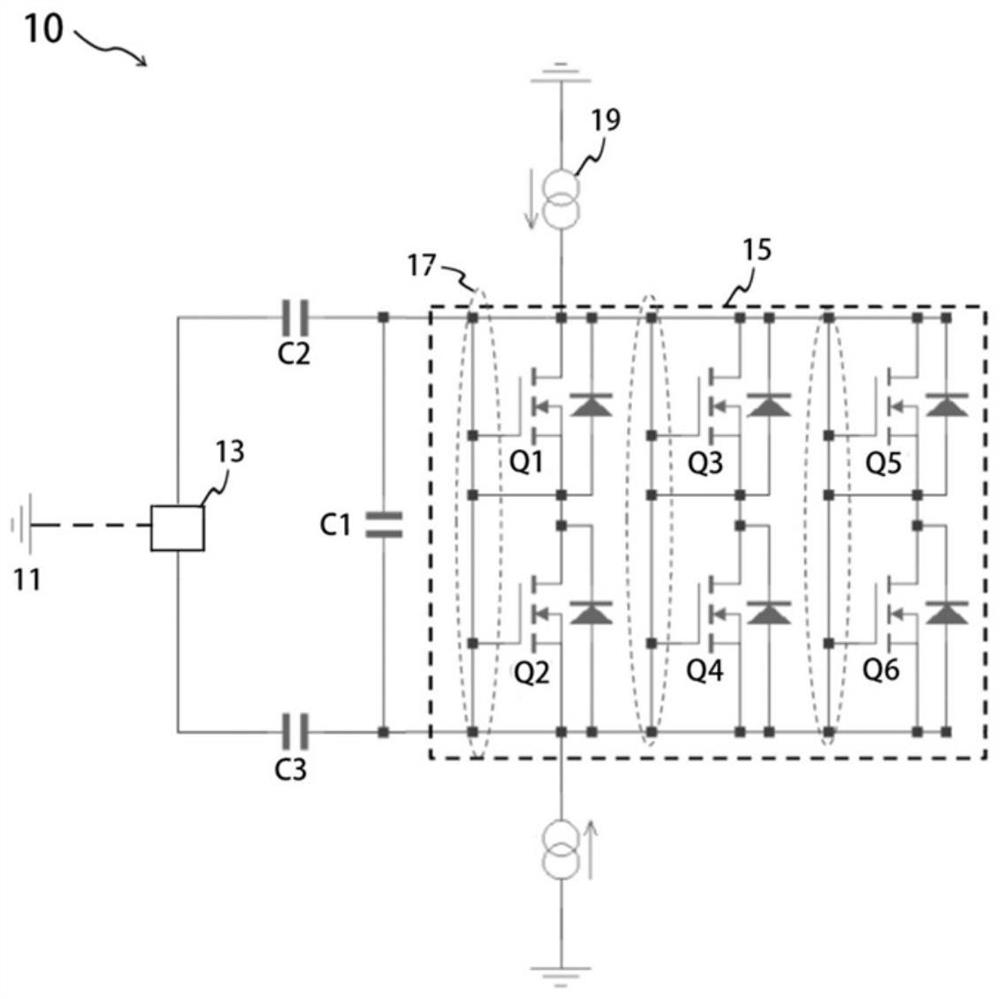

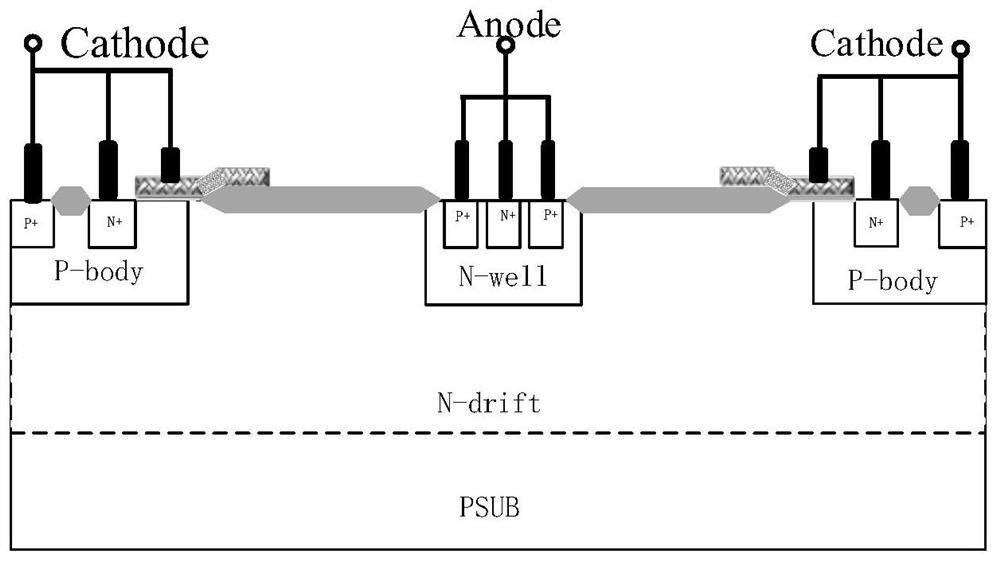

ESD protection device of SOI power switch

ActiveCN109742071AReduce ion concentrationIncrease holding voltageSolid-state devicesSemiconductor devicesGate oxideSemiconductor

The invention relates to the technical field of semiconductor devices, and in particular relates to an ESD protection device of an SOI power switch. The ESD protection device comprises a P-type substrate; an N-type deep trap on the P-type substrate; a first N trap, a first P trap, a first P-type intrinsic doping area, a second N trap, a second P-type intrinsic doping area, a second P trap and a third N trap sequentially arranged on the N-type deep trap, wherein the first P trap and the second N trap are isolated by the first P-type intrinsic doping area; the second N trap and the second P trapare isolated by the second P-type intrinsic doping area; the first P trap comprises a first P+ injection area and a first N+ injection area; the second P trap comprises a second N+ injection area anda second P+ injection area therein; a gate oxide layer is arranged on the second N trap; the first P+ injection area and the first N+ injection area are connected with an positive electrode; and thesecond N+ injection area and the second P+ injection area are connected with a cathode. The maintaining voltage of the device is improved, the triggering voltage of the device is reduced, and the bidirectional protection performance is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

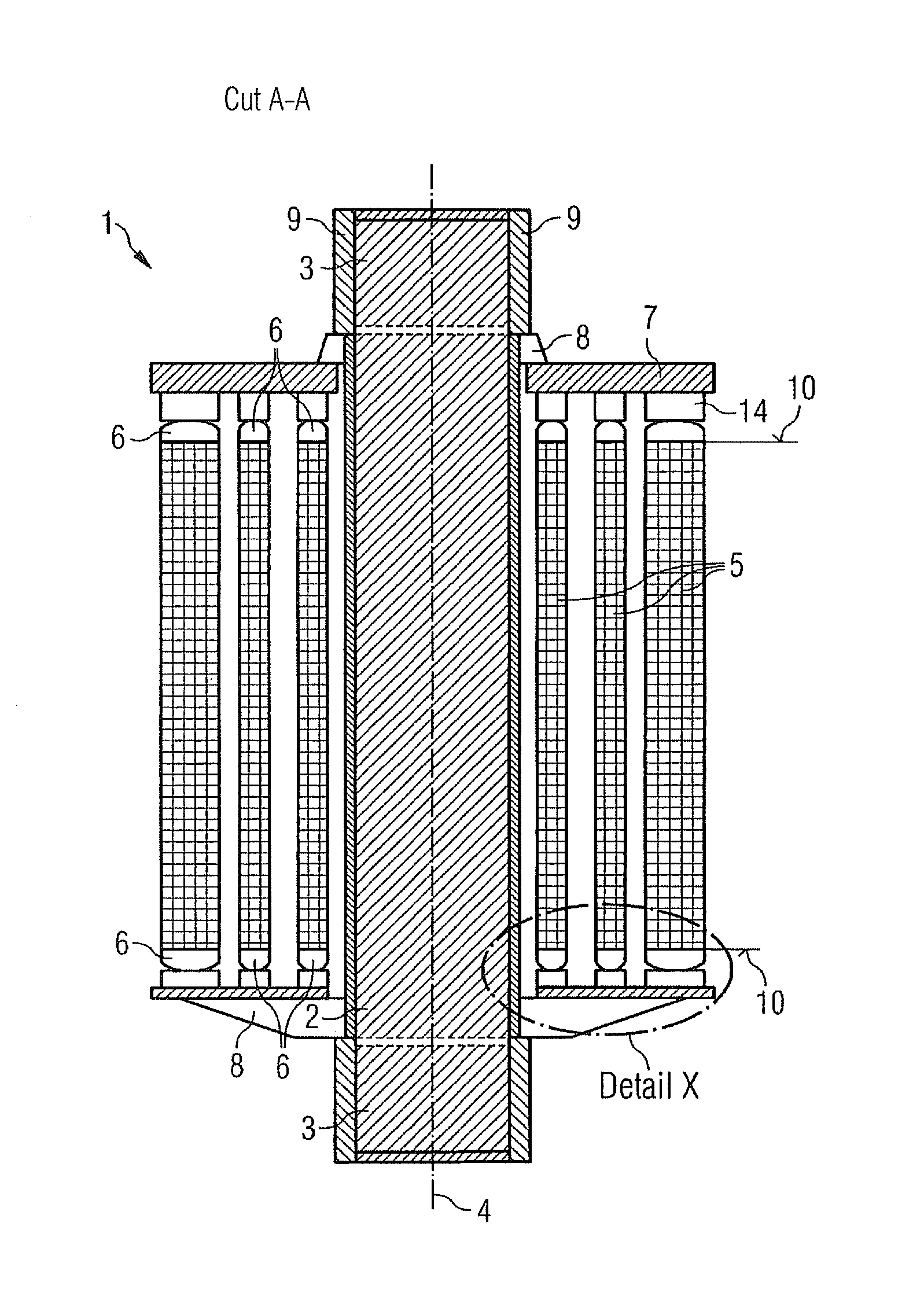

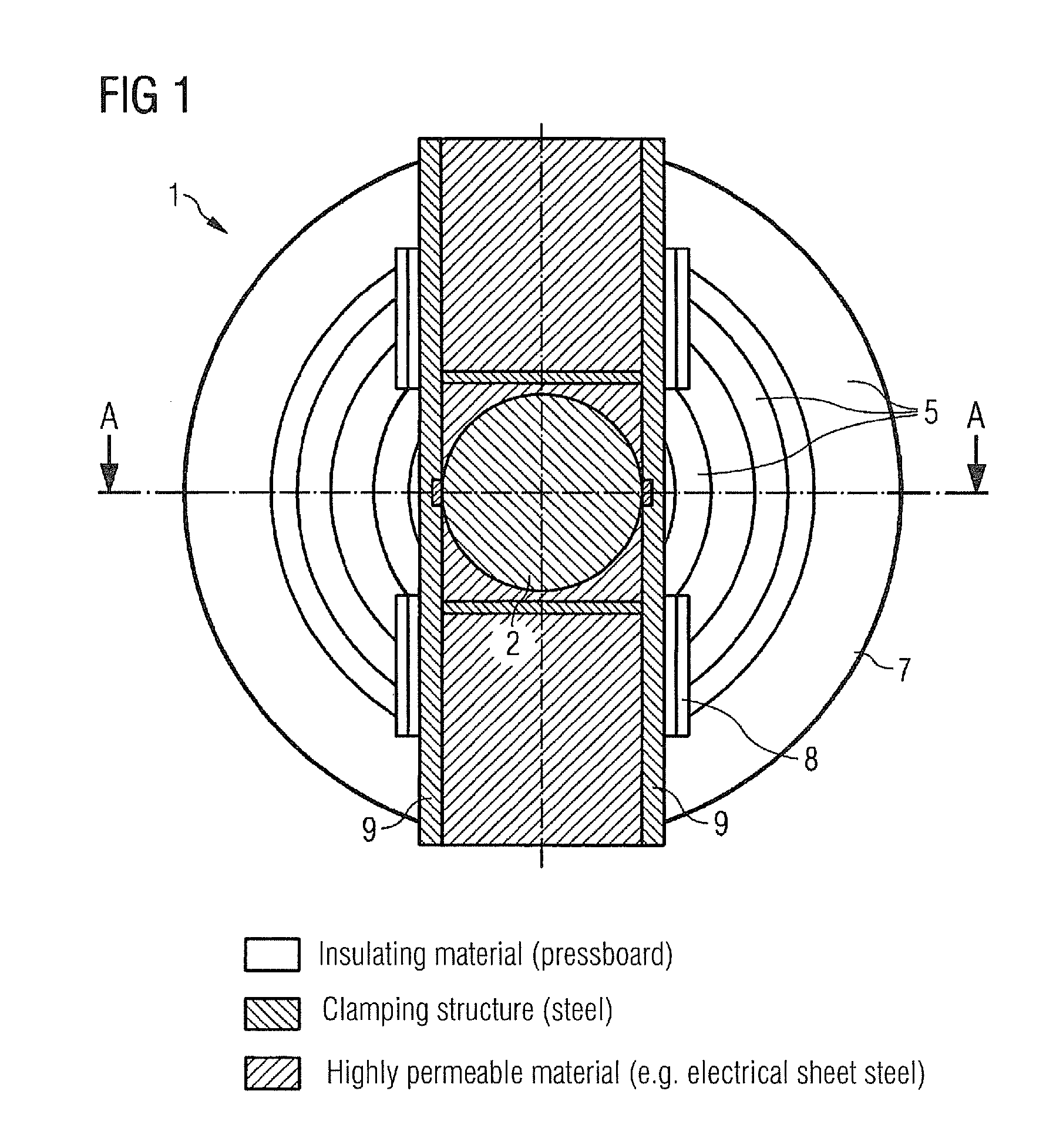

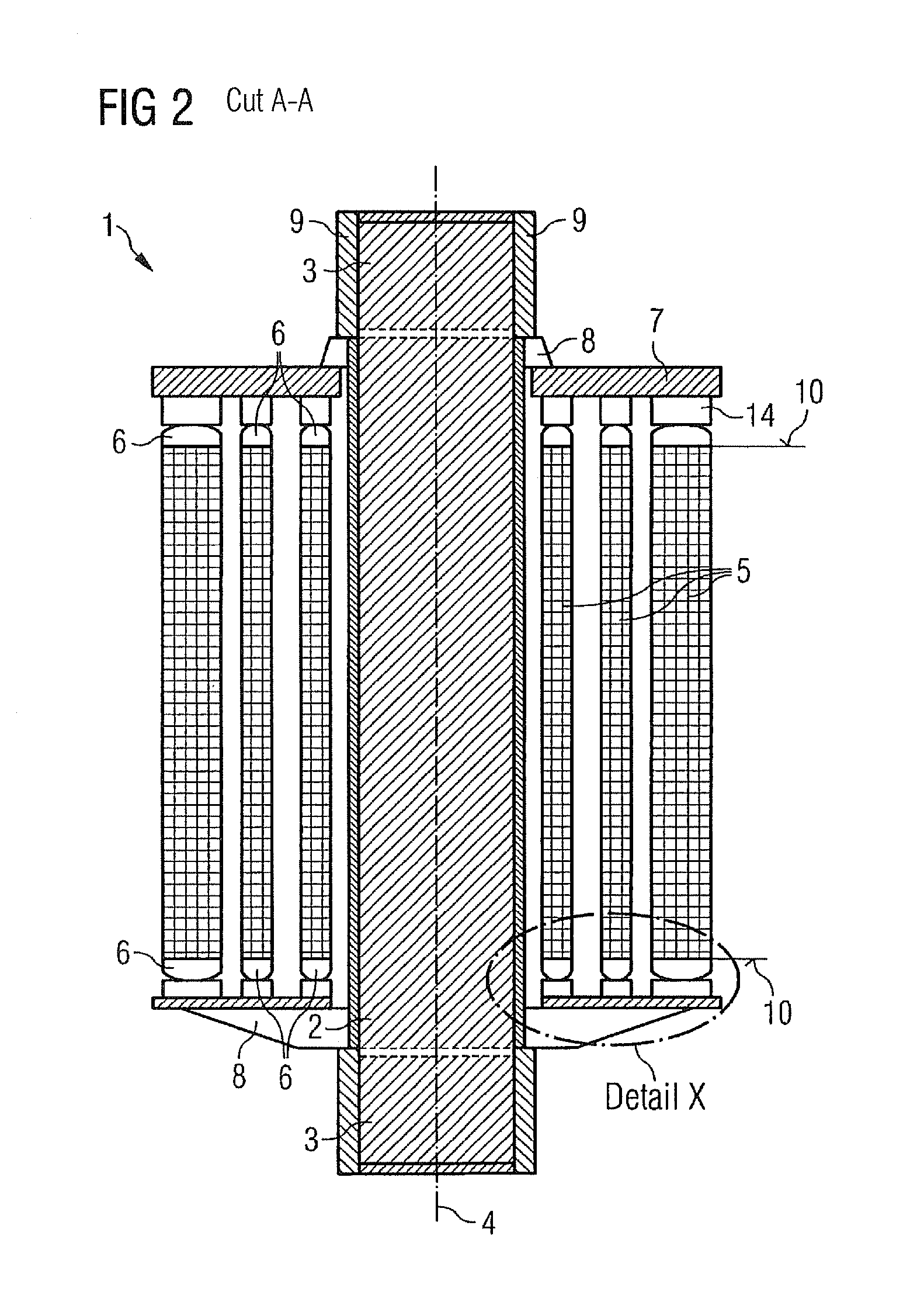

Winding arrangement for a transformer or for a throttle

InactiveUS20110316662A1Effective electrostatic protectionEasy to operateTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresTransformerConvex side

A winding arrangement for a transformer or for a reactor is provided. The winding arrangement includes an annular winding cover part disposed on the front face of a winding, wherein a side surface of the winding cover part overlaps a front surface of the winding, wherein the annular winding cover part is designed to be magnetically conductive at least in a partial area and comprises a convex side surface facing away from the winding.

Owner:SIEMENS AG OESTERR

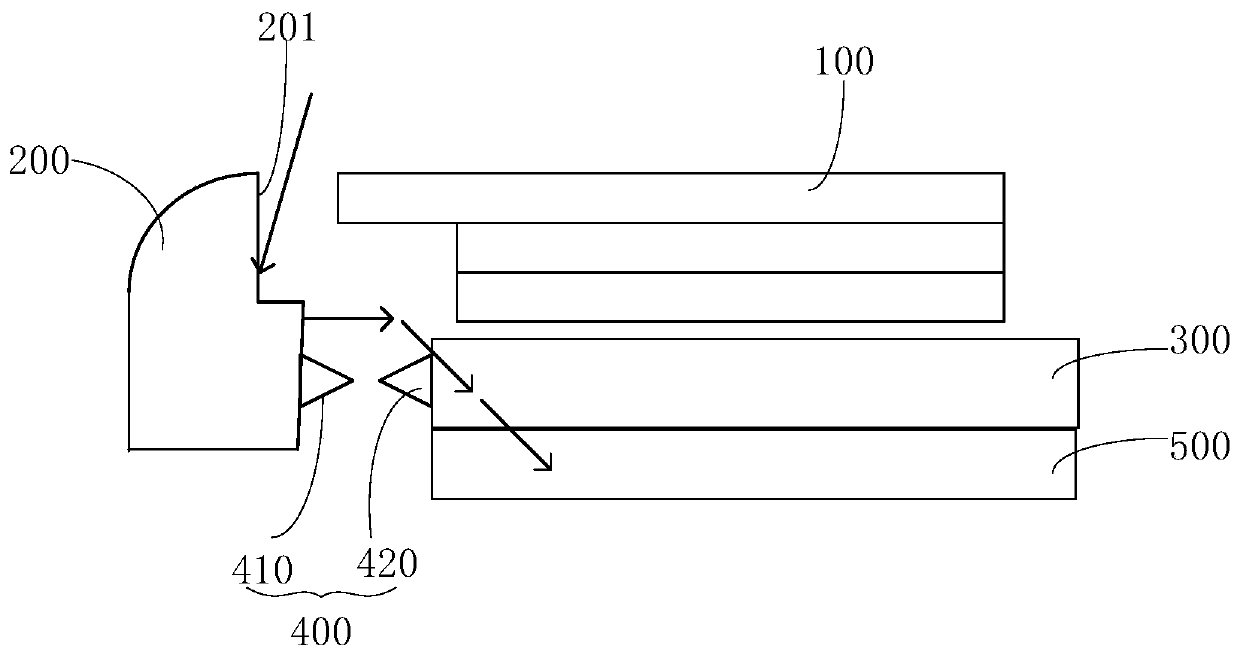

Electrostatic protection apparatus, radio frequency circuit and electronic equipment

InactiveCN107565530AImprove electrostatic discharge abilityEffective electrostatic protectionTransmissionEmergency protective arrangements for limiting excess voltage/currentHemt circuitsControl theory

Embodiments of the invention disclose an electrostatic protection apparatus, a radio frequency circuit and electronic equipment. The electrostatic protection apparatus comprises a front end interface,an electrostatic protection circuit and a back end circuit; the electrostatic protection circuit is positioned between the front end interface and the back end circuit; one end of the electrostatic protection circuit is connected with the front end interface while the other end is connected with the back end circuit; and the electrostatic protection circuit consists of an electrostatic dischargecircuit and a <pi>-shaped filtering circuit in connection, and is used for performing discharging of the electrostatic current transmitted by the front end interface. By virtue of the scheme, the electrostatic discharge capability of the electronic equipment can be improved, damage and interference to the back end circuit from electrostatic can be lowered, and effective electrostatic protection isprovided for the electronic equipment.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Electro static protection apparatus, radio-frequency circuit and electronic device

InactiveCN107425876AImprove electrostatic discharge abilityEffective electrostatic protectionElectrostatic discharge protectionSolid-state devicesEmbedded systemRadio frequency circuits

The embodiment of the invention discloses an electro static protection apparatus, a radio-frequency circuit and an electronic device. The electro static protection apparatus comprises a front-end interface, an electro static protection circuit and a rear-end circuit; the electro static protection circuit is positioned between the front-end interface and the rear-end circuit; one end of the electro static protection circuit is connected with the front-end interface, and the other end of the electro static protection circuit is connected with the rear-end circuit; and the electro static protection circuit consists of an electro static discharge circuit and a resistor by connection, and is used for discharging an electro static current transmitted by the front-end interface. The electro static protection apparatus provided by the invention can provide effective electro static protection for the electronic device.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Electrostatic protection component and electronic device

InactiveCN107704146AImprove electrostatic discharge abilityReduce distractionsDigital data processing detailsTelephone set constructionsEngineeringConductive materials

Embodiments of the invention disclose an electrostatic protection component and an electronic device. The electrostatic protection component comprises a glass cover plate and a touch screen located onone side of the glass cover plate, wherein the edge, fitting the touch screen, of the glass cover plate is coated with a first conductive material for connecting static electricity entering the touchscreen from the edge of the glass cover plate to the ground and guiding the static electricity to outside. Effective electrostatic protection can be provided for the touch screen.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

ESD protection device of SOI power switch

ActiveCN109786374AIncrease holding voltageLower the trigger voltageSolid-state devicesSemiconductor devicesEngineeringGate oxide

The invention relates to the technical field of semiconductor devices, in particular to an ESD protection device of an SOI power switch. The ESD protection device comprises a P-type substrate, an N-type deep well, a first N well, a first P well, a second N well, a second P well and a third N well, wherein the N-type deep well is arranged on the P-type substrate; the first N well, the first P well,the second N well, the second P well and the third N well are arranged on the N-type deep well in sequence; the width range of the second N well is 2-8 microns; the first P well internally comprisesa first P+ injection area and a first N+ injection area; a second P+ injection area crosses between the first P well and the second N well; the second P well internally comprises a second N+ injectionarea and a fourth P+ injection area; a third P+ injection area crosses between the second N well and the second P well; a gate oxide with a length range of 0.25-6 microns is arranged o the second N well; the first P+ injection area and the first N+ injection area are connected to an anode; and the second N+ injection area and the fourth P+ injection area are connected with a cathode. The ESD protection device is capable of improving the maintaining voltage of the device, reducing the triggering voltage of the device and improving the protection performance.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Electrostatic protection device, radio frequency circuit and electronic equipment

InactiveCN107453344AImprove electrostatic discharge abilityImprove stabilityEmergency protective arrangements for limiting excess voltage/currentTelephone set constructionsElectrostatic dischargeElectronic equipment

An embodiment of the invention discloses an electrostatic protection device, a radio frequency circuit and electronic equipment. The electrostatic protection device comprises a front end interface, an electrostatic protection circuit and a rear end circuit. The electrostatic protection circuit is located between the front end interface and the rear end circuit. One end of the electrostatic protection circuit is connected to the front end interface and the other end is connected to the rear end circuit. The electrostatic protection circuit is formed by an electrostatic discharge circuit and a T-shaped filter circuit which are connected together and is used for discharging a static current transmitted by the front end interface. In the scheme, an electrostatic discharge capacity of the electronic equipment can be increased, damages and an interference of static electricity to the rear end circuit are reduced, and effective electrostatic protection is provided for the electronic equipment.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Electrostatic protection apparatus, radio frequency circuit and electronic equipment

InactiveCN107565529AImprove electrostatic discharge abilityEffective electrostatic protectionTransmissionEmergency protective arrangements for limiting excess voltage/currentElectrostatic dischargeInductor

Embodiments of the invention disclose an electrostatic protection apparatus, a radio frequency circuit and electronic equipment. The electrostatic protection apparatus comprises a front end interface,an electrostatic protection circuit and a back end circuit; the electrostatic protection circuit is positioned between the front end interface and the back end circuit; one end of the electrostatic protection circuit is connected with the front end interface while the other end is connected with the back end circuit; and the electrostatic protection circuit consists of an electrostatic dischargecircuit and an inductor in connection, and is used for performing discharging of the electrostatic current transmitted by the front end interface. By virtue of the embodiments in the invention, effective electrostatic protection can be provided for the electronic equipment.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Protection circuit, radio frequency circuit, and electronic equipment

InactiveCN107592593AImprove electrostatic discharge abilityEffective electrostatic protectionTransmissionTransducer circuitsCapacitanceElectric equipment

Embodiments of the application disclose a protection circuit, a radio frequency circuit, and electronic equipment. The protection circuit comprises a front-end interface, a back-end circuit and a capacitor, the capacitor is arranged between the front-end interface and the back-end circuit in parallel, one terminal of the capacitor is separately connected with the front-end interface and the rear-end circuit, the other end of the capacitor is connected to the ground, and the capacitor is used for discharging an electrostatic current transmitted by the front-end interface. According to the scheme, the electrostatic discharging capability of the electronic equipment can be increased, the damage to the back-end circuit and the interference with the back-end circuit by static electricity are reduced, and effective electrostatic protection is provided for the electronic equipment.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

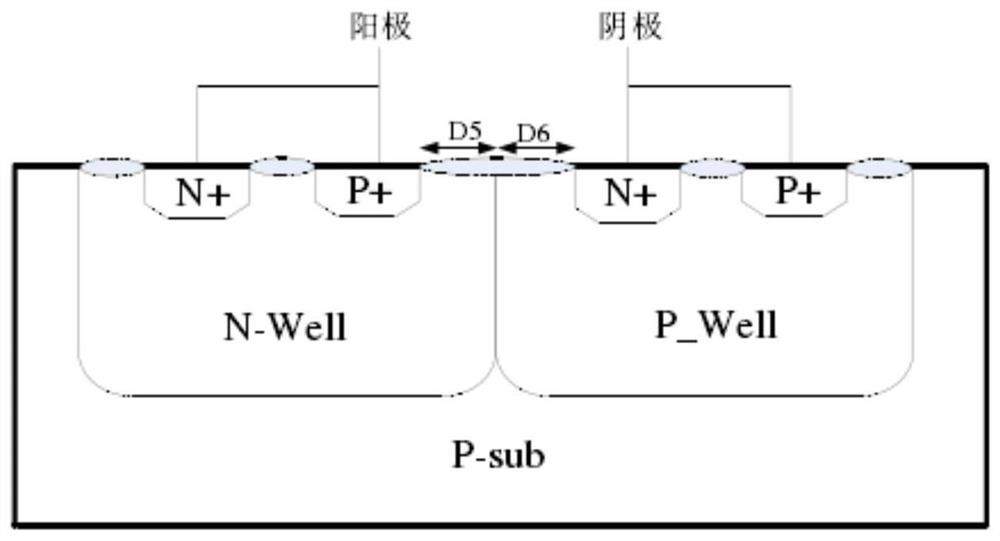

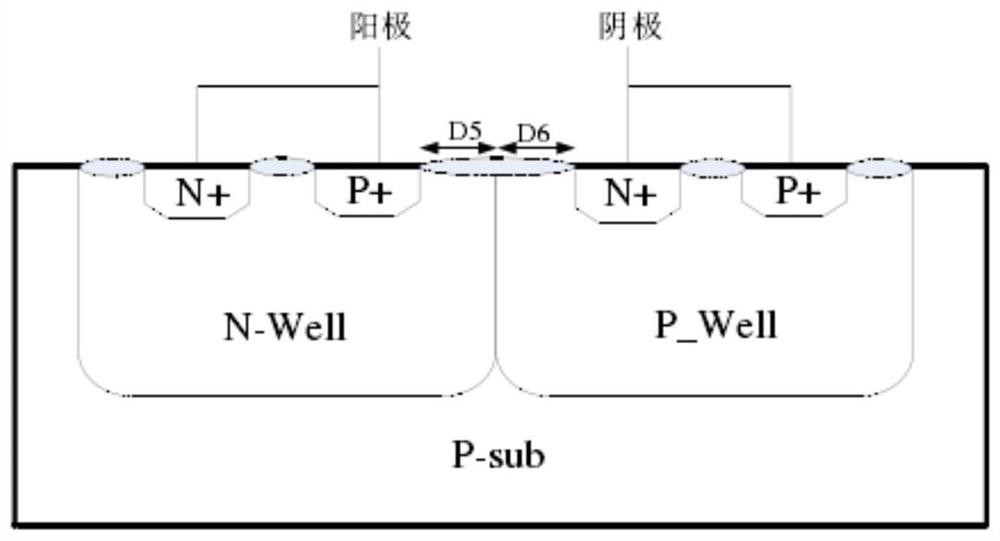

High area efficiency diode triggered controllable silicon based on two-dimension design

The invention discloses high area efficiency diode triggered controllable silicon based on two-dimension design. The high area efficiency diode triggered controllable silicon based on the two-dimension design comprises a P-type substrate, N wells, a P well, P+ injection regions, N+ injection regions, metal, a shallow-trench isolation part, a cathode and an anode, wherein the N wells comprise a first N well and a second N well, the P+ injection region comprises a first P+ injection region and a second P+ injection region, the N+ injection regions comprise a first N+ injection region, a second N+ injection region, a third N+ injection region, a fourth N+ injection region and a fifth N+ injection region, and the first N well, the P well and the second N well are arranged on the P-type substrate in sequence along the transverse direction. According to the high area efficiency diode triggered controllable silicon based on the two-dimension design, a diode is embedded into the controllable silicon at a trigger stage, electric current flows mainly along the longitudinal direction of a device, thereby, well resistance in the longitudinal direction of the device is fully utilized, and compared with conventional diode triggered controllable silicon, the high area efficiency diode triggered controllable silicon based on the two-dimension design has the advantages that only a few of series diodes of the device are required so that high trigger voltage can be achieved, and the area efficiency is increased.

Owner:HAINING BERNSTEIN BIOTECH CO LTD

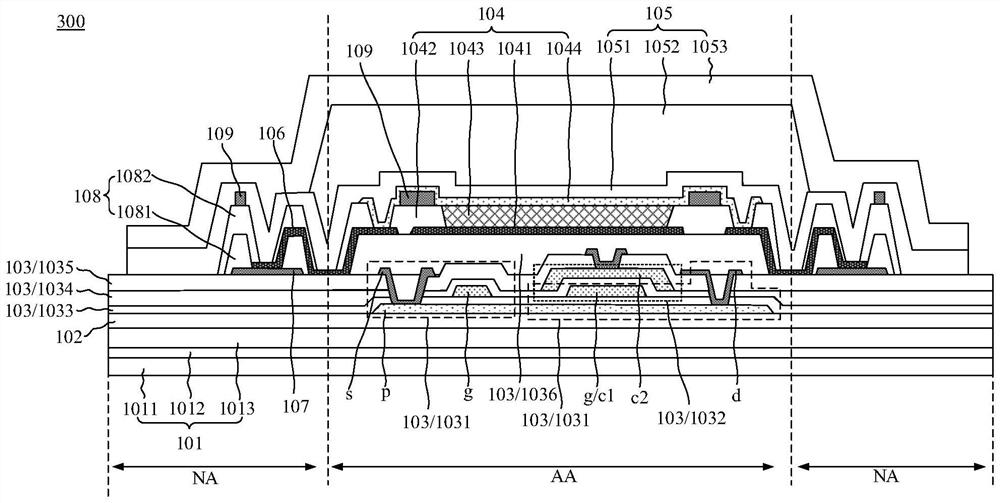

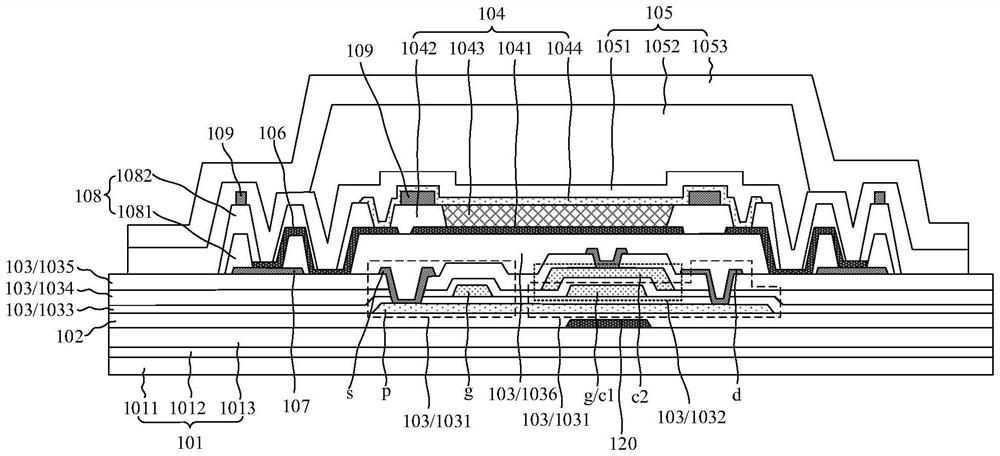

Display screen and electronic equipment

PendingCN114784058AEffective electrostatic protectionAvoid Feature DriftSemiconductor/solid-state device detailsSolid-state devicesMaterials scienceElectrostatic discharge

The embodiment of the invention provides a display screen and electronic equipment, relates to the technical field of display, and can perform effective electrostatic protection on transistors in a display panel. The display screen comprises a display panel, and the display panel comprises a display area and a non-display area surrounding the display area; the non-display area is provided with an electrostatic discharge structure, the electrostatic discharge structure is located in the edge area of a layer above the substrate of the non-display area, the outer edge of the electrostatic discharge structure is flush with the cutting edge of the substrate of the display panel, and the electrostatic discharge structure is electrically connected with a constant voltage structure used for providing fixed voltage.

Owner:HUAWEI TECH CO LTD

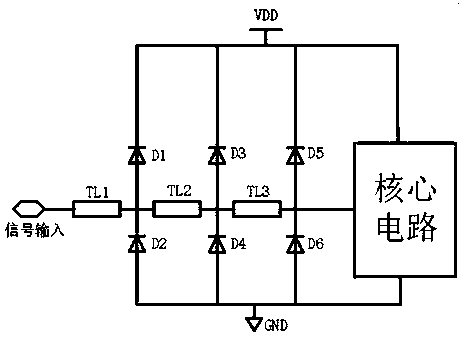

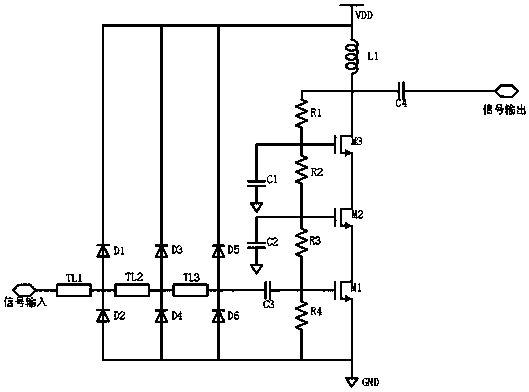

Power amplifier with electrostatic discharge protection circuit

InactiveCN108322195AIncrease load impedanceGuaranteed Phase ConsistencyAmplifier with semiconductor-devices/discharge-tubesAmplifier protection circuit arrangementsCoplanar waveguideEngineering

The invention relates to a power amplifier with an electrostatic discharge protection circuit. A core circuit uses a NMOS (N-channel metal oxide semiconductor) tube stacking structure; source electrodes and drain electrodes of three NMOS tubes are sequentially connected. Each NMOS tube is in bias arrangement in AB type; tandem resistors form a bias circuit. The electrostatic discharge protection circuit uses a distributed electrostatic discharge protection structure; the schematic diagram is shown as Figure 1; a diode in the protection circuit uses a PN junction diode; each electrostatic discharge protection unit uses the same diode; the diodes in parallel connection are connected through CPW (coplanar waveguide); the electrostatic discharge protection degrade of the core radio frequency power amplifier can be effectively improved; the parasitic effect of the protection circuit is weakened; the power amplifier is applicable to high work frequency.

Owner:天津大学(青岛)海洋工程研究院有限公司

Electrostatic protection device, radio frequency circuit, and electronic device

InactiveCN107359606AImprove electrostatic discharge abilityImprove stabilityEmergency protective arrangements for limiting excess voltage/currentEngineeringResistor

The embodiment of the application discloses an electrostatic protection device, a radio frequency circuit, and an electronic device. The electrostatic protection device comprises a front-end interface, an electrostatic protection circuit and a rear-end circuit. The electrostatic protection circuit is arranged between the front-end interface and the rear-end circuit; and one end of the electrostatic protection circuit is connected with the front-end interface and the other end is connected with the rear-end circuit. The electrostatic protection circuit formed by at least one resistor is used for discharging electrostatic currents transmitted by the front-end interface. Therefore, electrostatic protection on an electronic device is realized.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

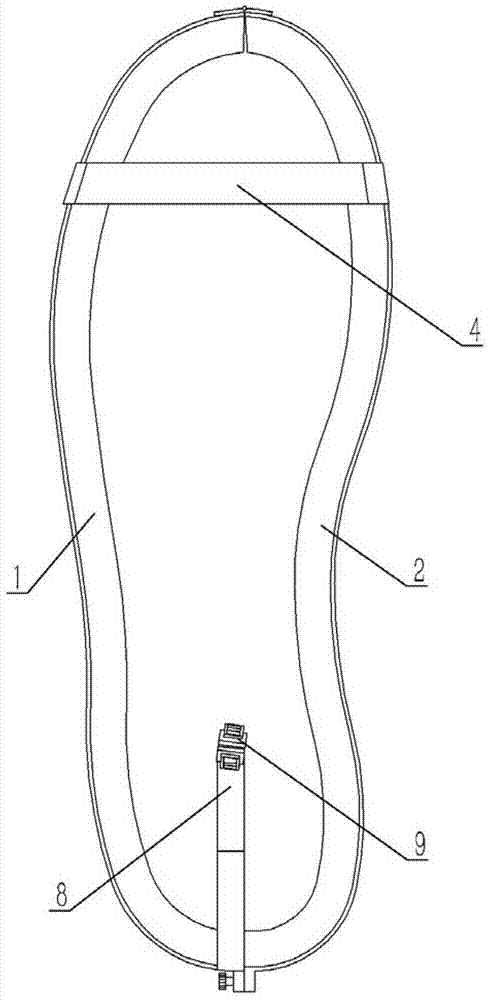

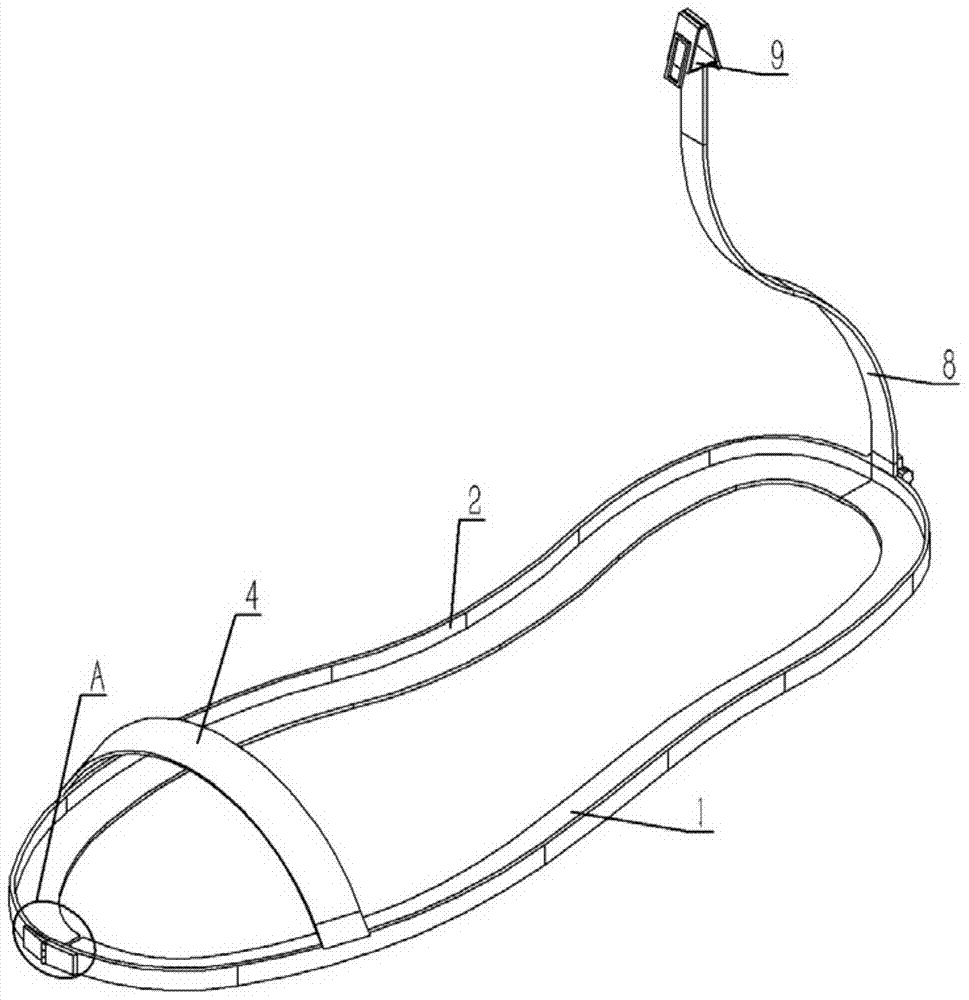

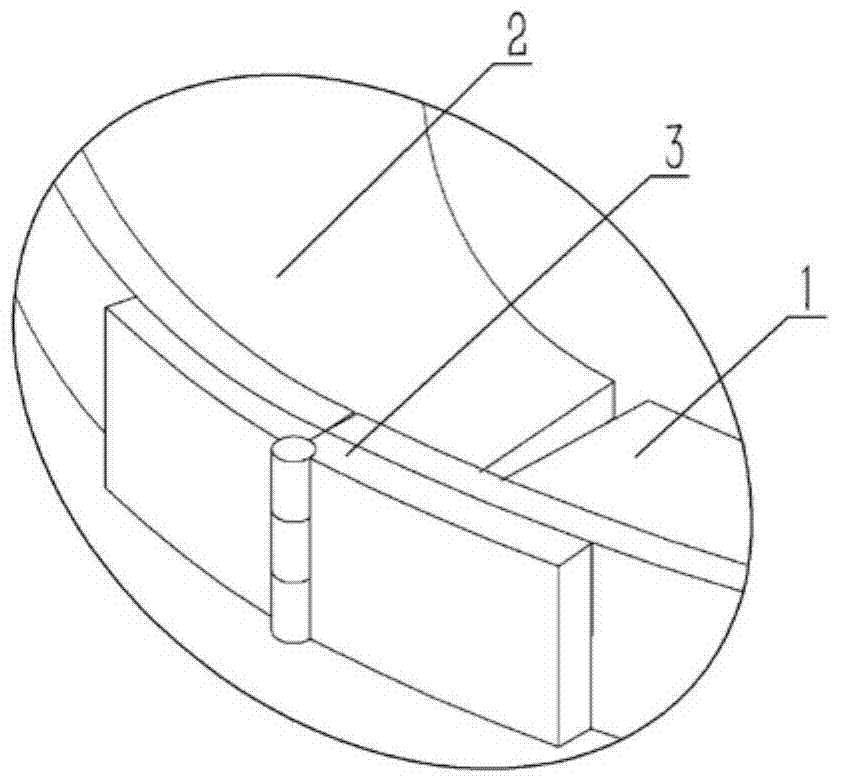

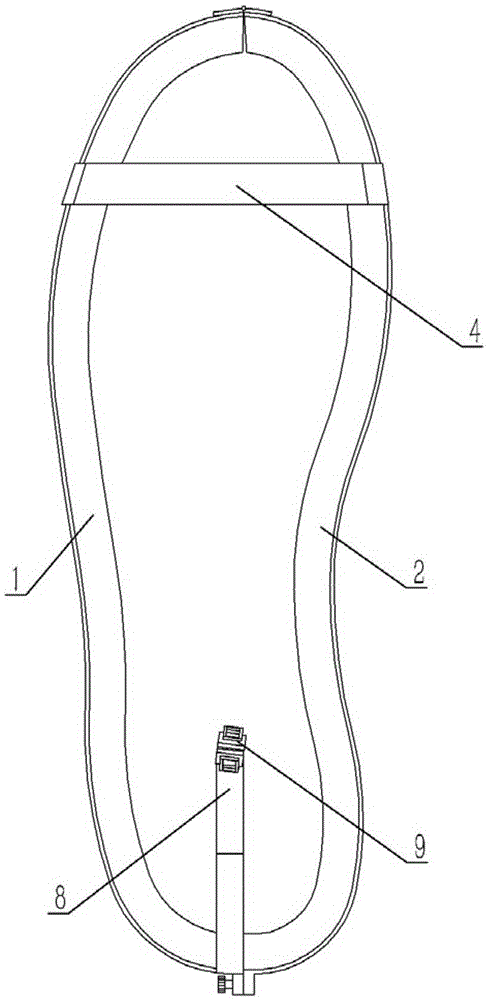

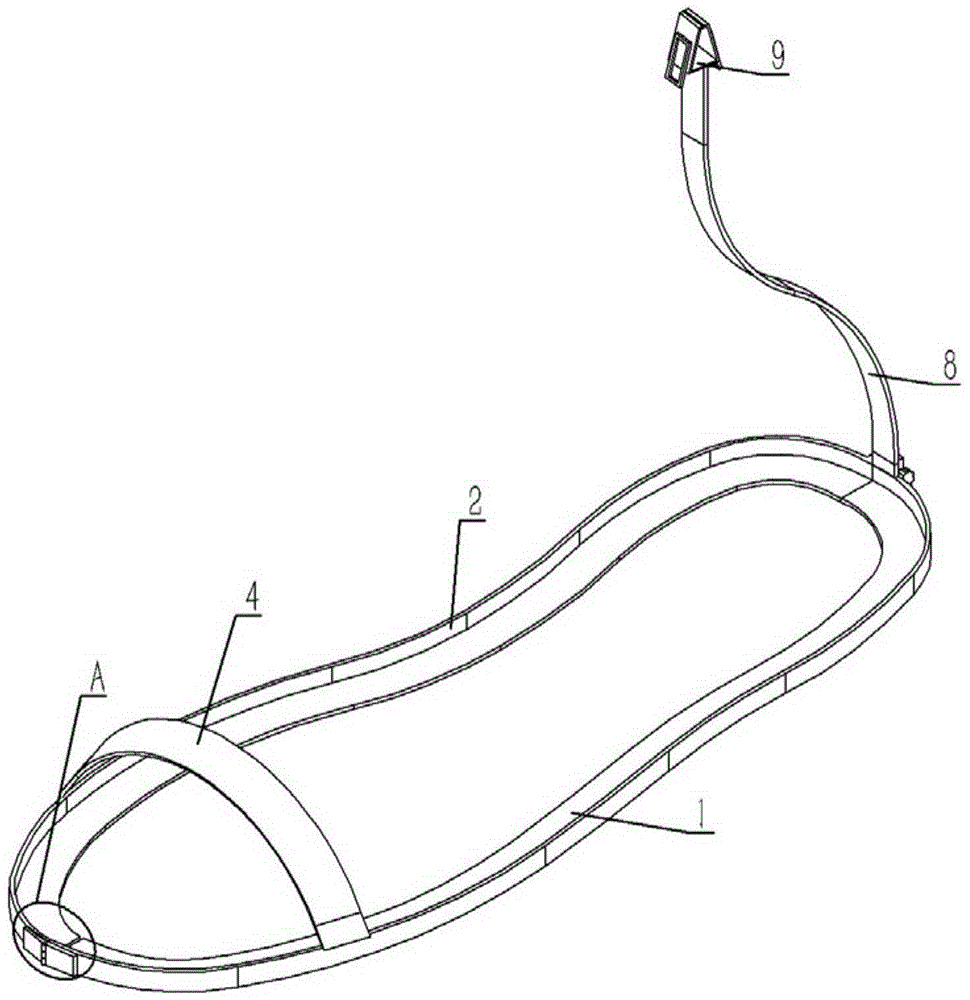

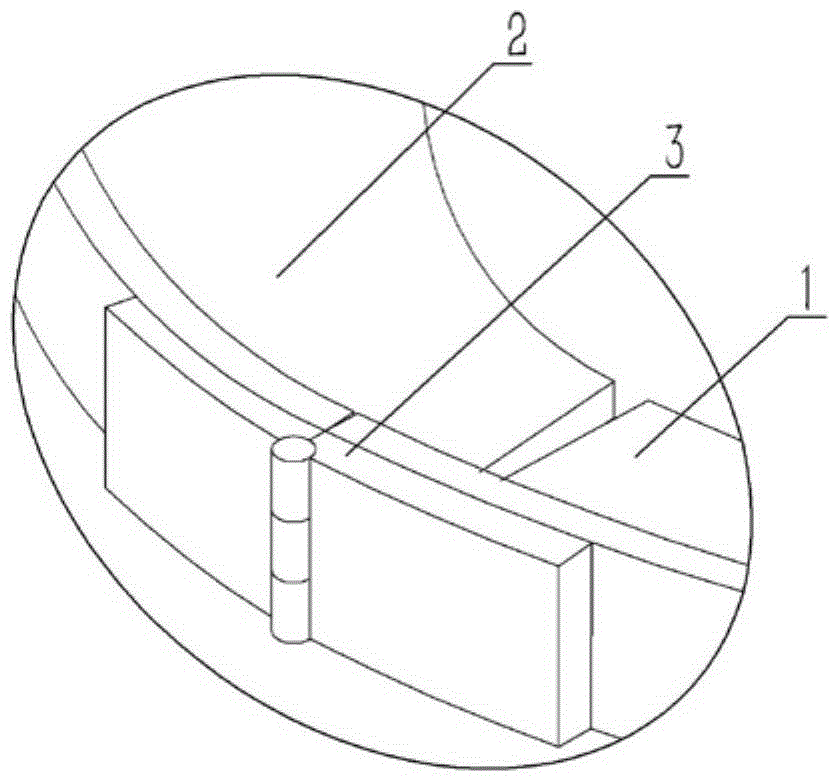

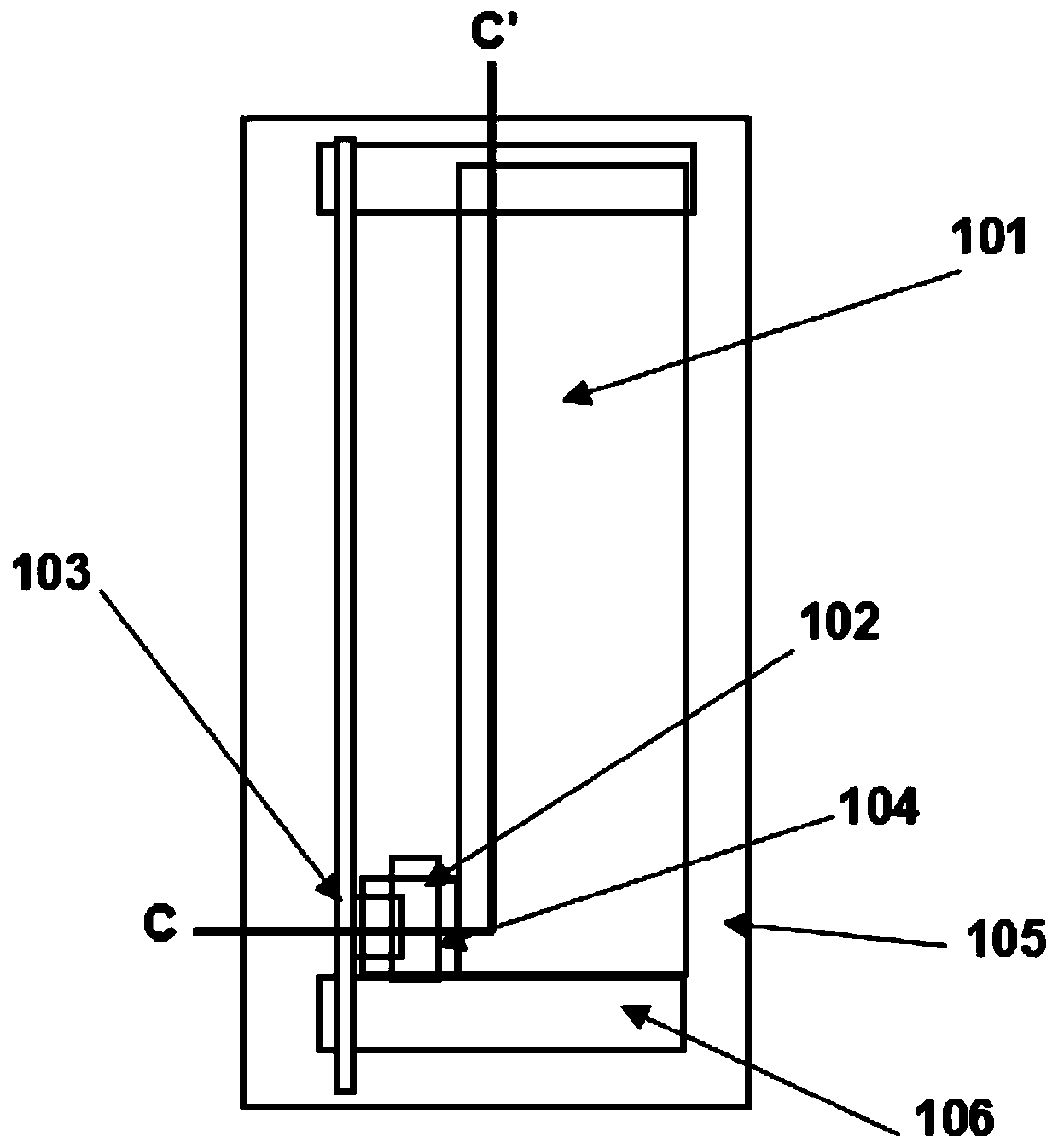

Hinge type anti-static shoe cover

ActiveCN104116264AEasy to replaceEffective electrostatic protectionFootwearAgricultural engineeringConductive rubber

The invention discloses a hinge type anti-static shoe cover which comprises an outer framework with the L-shaped cross section and an inner framework. The top end of he outer framework and the top end of the inner framework are connected together through a hinge in a hinged mode, a first connecting block and a second connecting block are formed at the tail end of the outer framework and the tail end of the inner framework respectively, and the first connecting block and the second connecting block are provided with threaded holes respectively and are connected through bolts in a threaded mode; the front side of the outer framework and the front side of the inner framework are provided with a spring belt, the two ends of the spring belt are fixed to the outer framework and the inner framework respectively, the tail end of the outer framework is fixedly connected with conductive rubber tape, the upper end of the conductive rubber tape is fixedly provided with a clamp, and the outer framework, the inner framework and the clamp are wrapped with conductive rubber. The novel anti-static shoe cover can be arranged on a shoe in a sleeved mode, the conductive rubber on the shoe cover is connected with an anti-static overall, replacement is convenient, and meanwhile efficient implementation electrostatic protection can be achieved.

Owner:SUZHOU JINGRO TECH

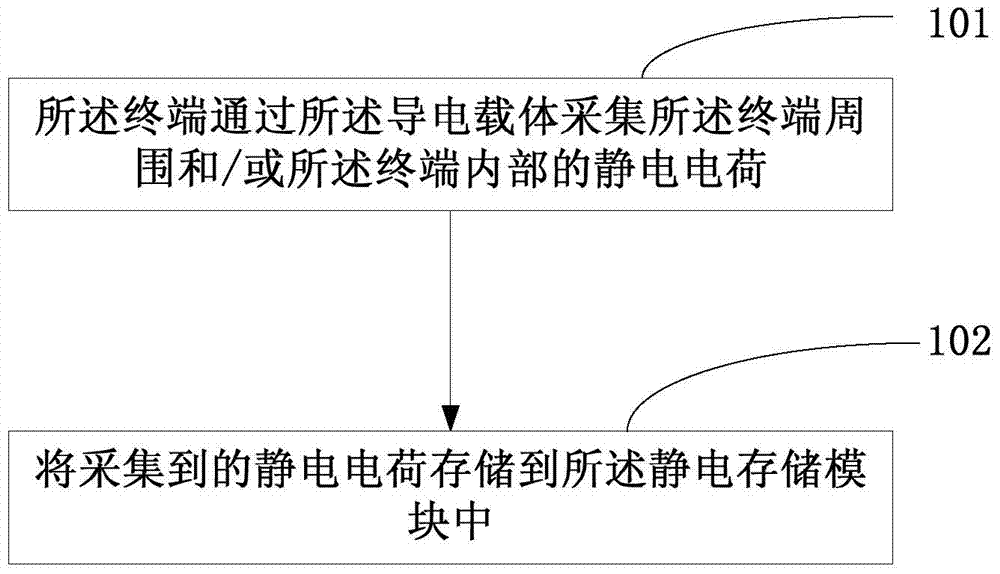

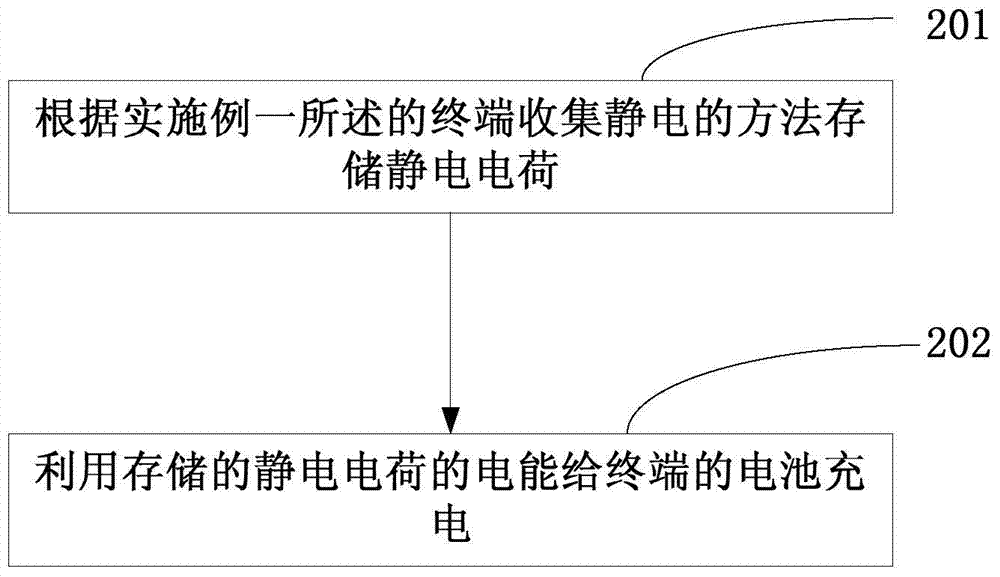

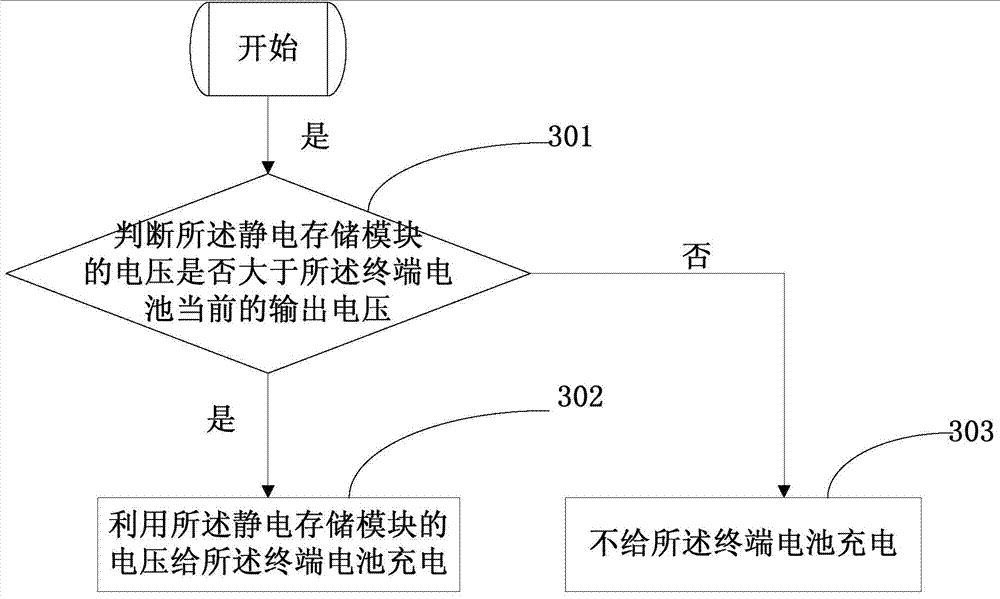

A terminal and method for collecting static electricity and charging the same

ActiveCN104427732BEffective electrostatic protectionAvoid damageBatteries circuit arrangementsElectrotherapyEngineeringElectrostatic discharge

The invention discloses a terminal and methods for collecting static electricity and charging the same. The outer surface of the terminal of the present invention is provided with a conductive carrier, and the method for collecting static electricity by the terminal of the present invention includes: the terminal collects the electrostatic charge around the terminal and / or inside the terminal through the conductive carrier; collects the collected static electricity Charge is stored into the electrostatic storage module. The present invention absorbs the static electricity generated by the human body or other substances through the conductive carrier, and stores the collected static electricity to effectively protect the terminal from static electricity.

Owner:ZTE CORP

a terminal device

ActiveCN108023978BEffective electrostatic protectionEnsure the consistency of electrostatic protectionTelephone set constructionsTerminal equipmentEngineering

The object of the invention is to provide a terminal device. The terminal device comprises a screen module; a bracket disposed on the periphery of the screen module; and a grounded metal middle framelocated on one side of the back face of the screen module; an inner side face of the bracket is a metal surface, and a gap is reversed between the inner surface of the bracket and the metal middle frame; and electrostatic protection structure is arranged between the metal surface of the bracket and the metal middle frame, and the electrostatic protection structure can enable electrostatic conduction between the metal surface of the bracket and the metal middle frame. The electrostatic problem on the side edge of the screen module can be effectively solved, an effective electrostatic protectionfunction can be performed on the side edges of the screen module, and the antenna performance is ensured.

Owner:VIVO MOBILE COMM CO LTD

A hinge type anti-static shoe cover

ActiveCN104116264BEasy to replaceEffective electrostatic protectionFootwearAgricultural engineeringConductive rubber

The invention discloses a hinge type anti-static shoe cover which comprises an outer framework with the L-shaped cross section and an inner framework. The top end of he outer framework and the top end of the inner framework are connected together through a hinge in a hinged mode, a first connecting block and a second connecting block are formed at the tail end of the outer framework and the tail end of the inner framework respectively, and the first connecting block and the second connecting block are provided with threaded holes respectively and are connected through bolts in a threaded mode; the front side of the outer framework and the front side of the inner framework are provided with a spring belt, the two ends of the spring belt are fixed to the outer framework and the inner framework respectively, the tail end of the outer framework is fixedly connected with conductive rubber tape, the upper end of the conductive rubber tape is fixedly provided with a clamp, and the outer framework, the inner framework and the clamp are wrapped with conductive rubber. The novel anti-static shoe cover can be arranged on a shoe in a sleeved mode, the conductive rubber on the shoe cover is connected with an anti-static overall, replacement is convenient, and meanwhile efficient implementation electrostatic protection can be achieved.

Owner:SUZHOU JINGRO TECH

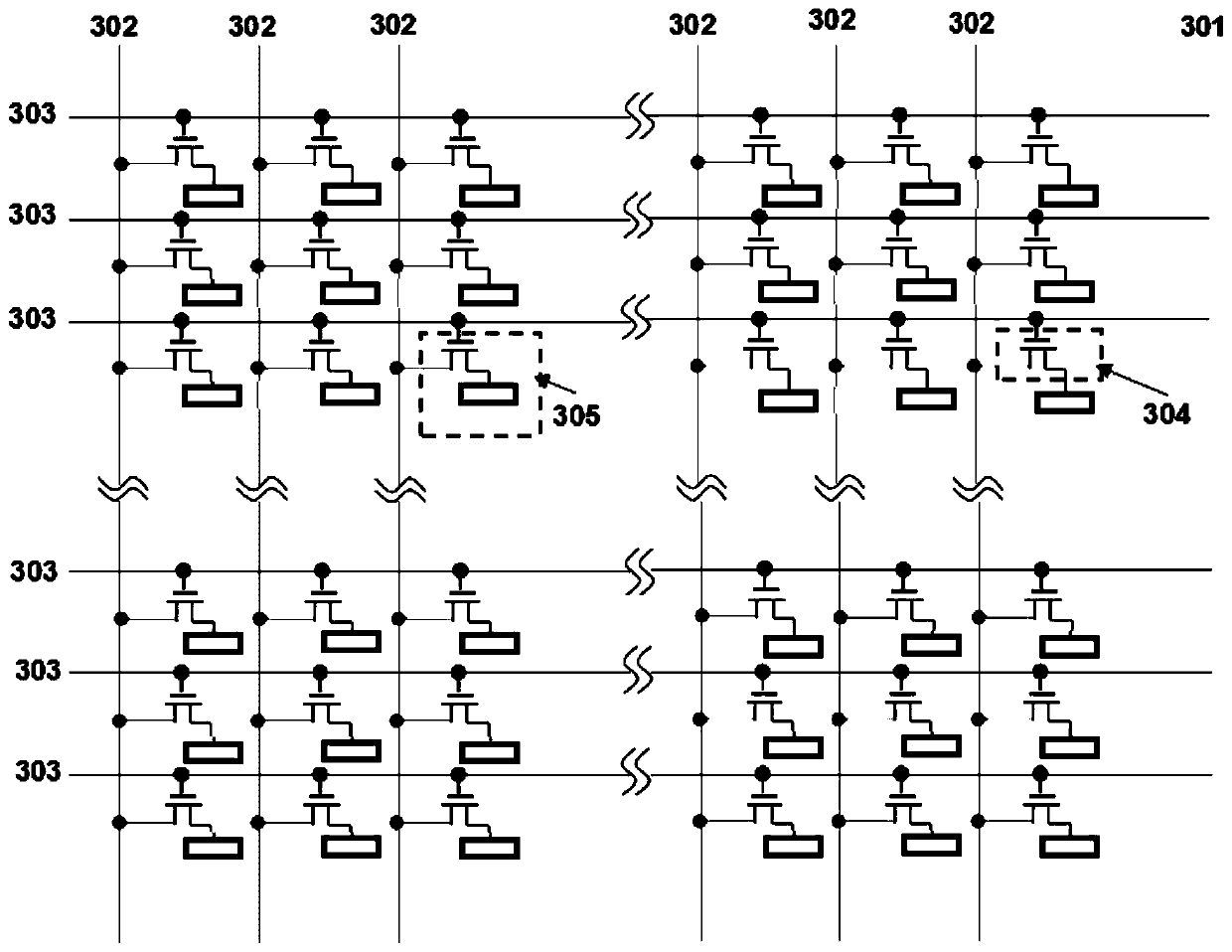

Method of assessing electro-static discharge sensitivity of flat panel display product in manufacture

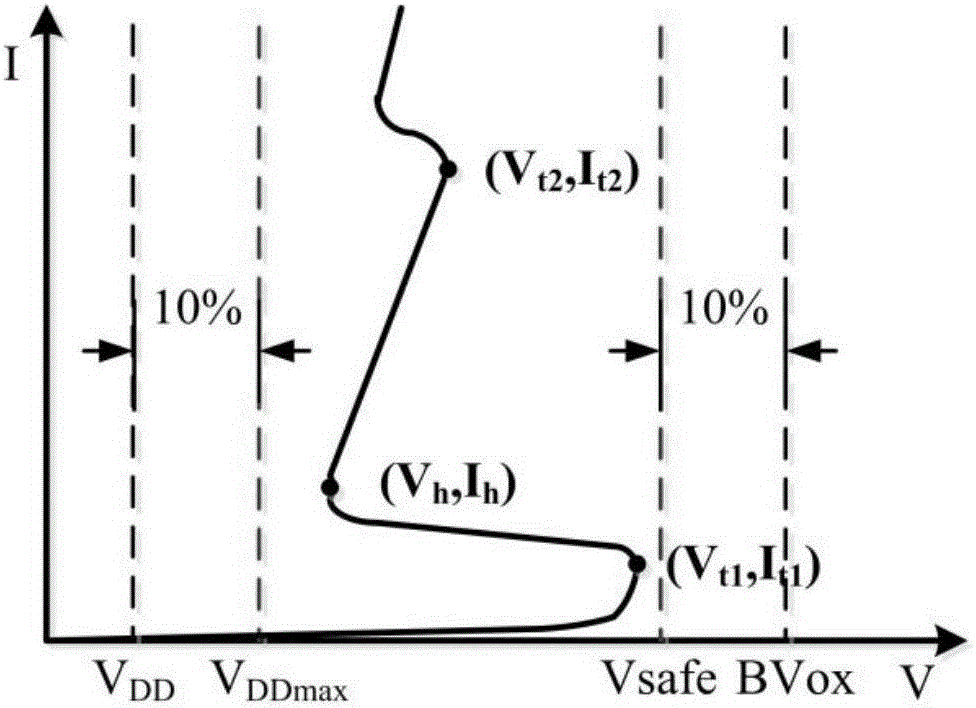

ActiveCN109933910AEffective electrostatic protectionSpecial data processing applicationsManufacturing computing systemsSensitivity testElectron

The invention discloses a method of assessing electro-static discharge (ESD) sensitivity of flat panel display (FPD) product in manufacture. The method comprises the following steps of: A, establishing an electronic device structure simulation model of an FPD product in a front-end manufacturing process; B, establishing an ESD failure condition simulation model in the front end manufacturing process of the FPD product according to the simulation model in the step A; and C, establishing an ESD failure sensitivity test method in the front end manufacturing process of the FPD product according tothe simulation model in the step B. With the adoption of the method and the device, an FPD manufacturing factory can master the ESD sensitivity degree of the FPD product of the FPD manufacturing factory, and reasonable electrostatic protection planning design can be performed in the factory according to the ESD sensitivity degree, so that an effective electrostatic protection target in an FPD product production and manufacturing stage is realized.

Owner:广州林恩静电科学技术应用有限公司

A Low Trigger Voltage Bidirectional SCR Device Based on Buried Layer Triggering

ActiveCN106206569BOpen fastEffective electrostatic protectionSolid-state devicesDiodeIsolation effectLow voltage

The invention belongs to the field of electronic technology and provides a low trigger voltage bidirectional SCR device based on buried layer triggering, which is used to reduce the trigger voltage of the bidirectional SCR device. The bidirectional SCR device of the present invention comprises a main device, n and m trigger devices on both sides of the main device, the trigger devices are diode devices, and adjacent trigger devices are connected in series; the main device is in the basic bidirectional SCR structure The first conductivity type well region A and the first conductivity type well region C of the first conductivity type well region are respectively provided with a first conductivity type heavily doped region, and the closed first conductivity type that only plays an isolation role in the basic bidirectional SCR is heavily doped. The doped buried layer is connected in series with external trigger diodes on both sides to form a low-voltage trigger channel of "buried layer + diode string", thereby reducing the trigger voltage of bidirectional SCR devices; at the same time, the trigger voltage can be adjusted by adjusting the number of trigger devices; The invention also effectively improves the opening speed of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

An esd protection device for soi power switch

ActiveCN109742071BReduce ion concentrationIncrease holding voltageSolid-state devicesSemiconductor devicesDevice materialVoltage droop

The invention relates to the technical field of semiconductor devices, in particular to an ESD protection device for an SOI power switch, comprising: a P-type substrate; an N-type deep well on the P-type substrate; first sequentially arranged on the N-type deep well N well, first P well, first P-type intrinsic doped region, second N well, second P-type intrinsic doped region, second P well, third N well, first P-type intrinsic doped region The impurity region isolates the first P well and the second N well, and the second P-type intrinsic doping region isolates the second N well and the second P well; the first P well includes a first P+ injection region, a first N+ injection region ; The second P well includes a second N+ injection region and a second P+ injection region; there is a gate oxide layer on the second N well, the first P+ injection region and the first N+ injection region are connected to the anode, and the second N+ injection region and The second P+ injection region is connected to the cathode, which increases the maintenance voltage of the device, reduces the trigger voltage of the device, and improves the bidirectional protection performance.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Protection circuit, radio frequency circuit and electronic equipment

InactiveCN107612575AImprove electrostatic discharge abilityReduce damage and disruptionTransmissionEmergency protective arrangements for limiting excess voltage/currentElectrostatic dischargeInductor

The embodiment of the application discloses a protection circuit, a radio frequency circuit and electronic equipment. The protection circuit comprises a front-end interface, a rear-end circuit and aninductor; the inductor is arranged in parallel between the front-end interface and the rear-end circuit; one end of the inductor is respectively connected with the front-end interface and the rear-endcircuit, and the other end of the inductor is grounded; and the inductor is used for carrying out discharging on an electrostatic current transmitted by the front-end interface. According to the scheme, electrostatic discharging capacity of the electronic equipment can be improved, damage and interference of static electricity to the rear-end circuit are reduced, and effective electrostatic protection is provided for the electronic equipment.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

A High Area Efficiency Diode Triggered SCR Based on Two-Dimensional Design

The invention discloses high area efficiency diode triggered controllable silicon based on two-dimension design. The high area efficiency diode triggered controllable silicon based on the two-dimension design comprises a P-type substrate, N wells, a P well, P+ injection regions, N+ injection regions, metal, a shallow-trench isolation part, a cathode and an anode, wherein the N wells comprise a first N well and a second N well, the P+ injection region comprises a first P+ injection region and a second P+ injection region, the N+ injection regions comprise a first N+ injection region, a second N+ injection region, a third N+ injection region, a fourth N+ injection region and a fifth N+ injection region, and the first N well, the P well and the second N well are arranged on the P-type substrate in sequence along the transverse direction. According to the high area efficiency diode triggered controllable silicon based on the two-dimension design, a diode is embedded into the controllable silicon at a trigger stage, electric current flows mainly along the longitudinal direction of a device, thereby, well resistance in the longitudinal direction of the device is fully utilized, and compared with conventional diode triggered controllable silicon, the high area efficiency diode triggered controllable silicon based on the two-dimension design has the advantages that only a few of series diodes of the device are required so that high trigger voltage can be achieved, and the area efficiency is increased.

Owner:HAINING BERNSTEIN BIOTECH CO LTD

An esd protection device for soi power switch

ActiveCN109786374BIncrease holding voltageLower the trigger voltageSolid-state devicesSemiconductor devicesDevice materialVoltage drop

The present invention relates to the technical field of semiconductor devices, in particular to an ESD protection device for an SOI power switch, comprising: a P-type substrate; an N-type deep well on the P-type substrate; first sequentially arranged on the N-type deep well N well, first P well, second N well, second P well, third N well, the width range of the second N well is 2‑8μm; the first P well includes the first P+ injection region, the first N+ Implantation region, there is a second P+ implantation region across between the first P well and the second N well; the second P well includes a second N+ implantation region, a fourth P+ implantation region, between the second N well and the second There is a third P+ injection region across the P wells; there is a gate oxide layer on the second N well, the length of the gate oxide layer is 0.25-6 μm, the first P+ injection region and the first N+ injection region are connected to the anode, and the second N well is connected to the anode. The second N+ injection region and the fourth P+ injection region are connected to the cathode, which increases the sustain voltage of the device, reduces the trigger voltage of the device, and improves the protection performance.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

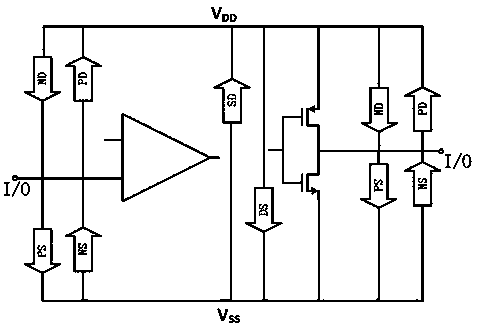

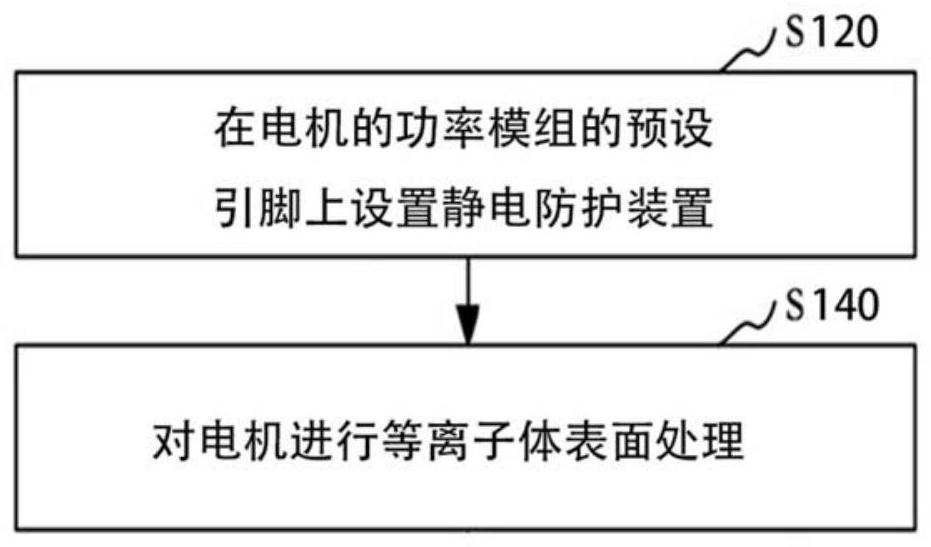

Electrostatic protection method and equipment, computer equipment and readable storage medium

PendingCN112074065ASo as not to damageEffective electrostatic protectionElectrostatic chargesEarth/grounding circuitsHemt circuitsEngineering

The invention discloses an electrostatic protection method and equipment, computer equipment and a readable storage medium. The electrostatic protection method is applied to the preparation of a motor, and comprises the following steps: setting an electrostatic protection device on a preset pin of a power module of a motor; and performing plasma surface treatment on the motor, wherein the electrostatic protection device comprises a short circuit assembly, a shielding assembly and an electrostatic protection circuit. According to the method, the specific pin of the transistor in the power module is short-circuited, shielded or connected with the protection circuit by using the specific electrostatic protection device, so that effective electrostatic protection of the electrode with relatively low withstand voltage is realized, the operation is convenient and fast, the stability is good, and the power module is prevented from being damaged by static electricity generated in the electrodepreparation process.

Owner:SHANGHAI VALEO AUTOMOTIVE ELECTRICAL SYST

Electrostatic protection device and manufacturing method thereof

PendingCN114078836AEffective electrostatic protectionAvoid latch-upTransistorSolid-state devicesLDMOSVoltage spike

The invention provides an electrostatic protection device and a manufacturing method thereof. The electrostatic protection device comprises: a substrate; a drift region formed on the substrate; a well region formed on the drift region; and a first body region and a second body region which are arranged on the two sides of the well region respectively, wherein the distance between the well region and the first body region is smaller than the distance between the well region and the second body region. Only a first heavily doped region is arranged in the first body region, a second heavily doped region and a third heavily doped region are arranged in the second body region, and only a fourth heavily doped region is arranged in the well region. Only a parasitic PNP triode is reserved on one side of the drain end of a traditional LDMOS-SCR device, a parasitic SCR is reserved on the other side of the drain end of the traditional LDMOS-SCR device, meanwhile, the relevant size is designed, so thateffective electrostatic protection is achieved, and the PNP is triggered before the SCR, and the latch-up phenomenon caused by deep hysteresis reaching a very low maintaining voltage due to the parasitic SCR mistakenly triggered when voltage overshoot or voltage spike burrs occur is avoided.

Owner:JOULWATT TECH INC LTD

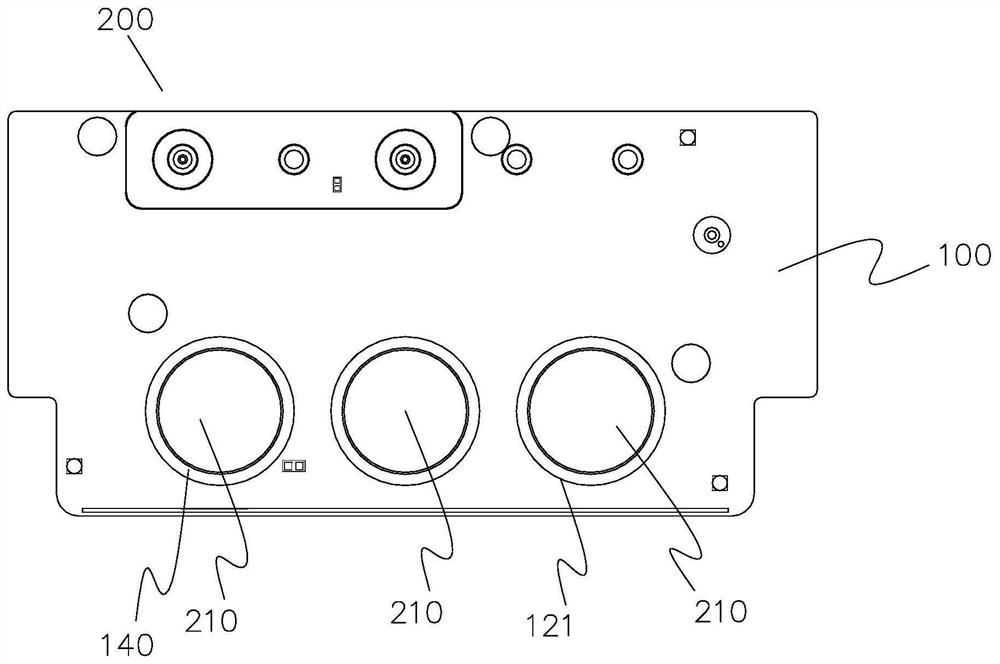

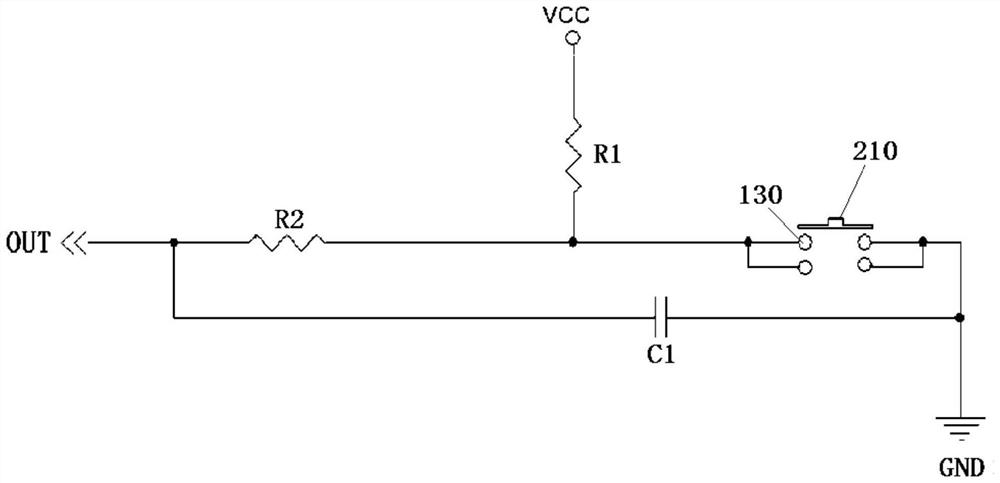

Printed circuit board, printed assembly board and electronic equipment

PendingCN113556866ALow costEffective electrostatic protectionHigh voltage circuit adaptationsOvervoltage circuit protectionGround planePrinted circuit board

The invention relates to a printed circuit board, a printed assembly board and electronic equipment, and the printed circuit board comprises an insulating substrate, an operation part bonding pad printed on the insulating substrate, a ground plane printed on the insulating substrate, and a protection layer covering the ground plane. The operation part bonding pad is a bonding pad used for being connected with an operation part receiving external triggering; and the protection layer forms a window beside the operation part bonding pad, so that the ground plane is exposed outwards at the window.

Owner:ALIBABA GRP HLDG LTD