Power amplifier with electrostatic discharge protection circuit

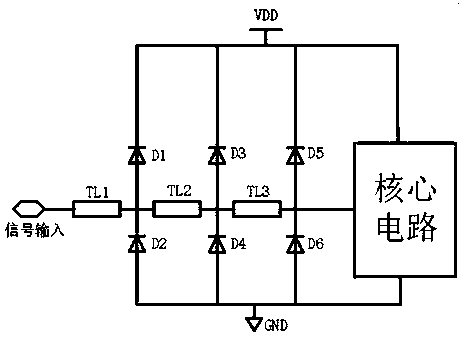

An electrostatic discharge protection and power amplifier technology, which is applied to amplifiers with semiconductor devices/discharge tubes, amplifier protection circuit layout, amplifiers, etc. Ensure phase consistency, achieve output power, and improve the effect of protection level

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

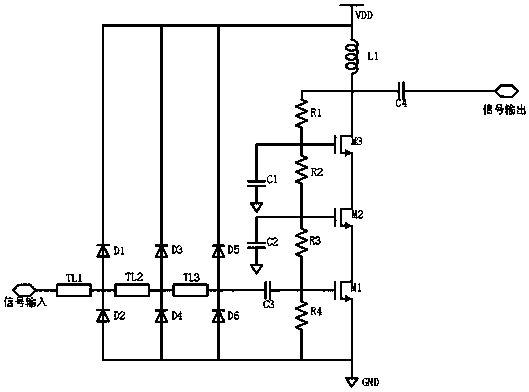

[0016] In order to illustrate the technical solution of the present invention more clearly, the present invention will be further described below in conjunction with the accompanying drawings. For those skilled in the art, other drawings can also be obtained based on these drawings without creative effort.

[0017] Such as figure 2 As shown, the core stack structure power amplifier of the present invention is composed of three NMOS transistors M1, M2, M3, the DC bias of each NMOS transistor is biased in class AB, and the resistors R1, R2, R3, and R4 are voltage dividing resistors , to provide bias voltage for the gates of the three NMOS transistors, and the bias point can be optimized by continuously adjusting the resistance ratio of the four resistors. The gates of the three NMOS transistors are respectively connected to three external capacitors C1, C2, and C3. The gate capacitances of the three NMOS transistors and the three external gate capacitors are used to adjust the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More