Mask slice graphic structure and manufacturing method of semiconductor chip

A pattern structure and mask technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of inability, the cutting line cannot have any graphics and metal, and the process inspection mark pattern cannot be placed. Achieve the effect of avoiding stress damage, ensuring inspection and electrical performance testing, and avoiding wear and tear

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

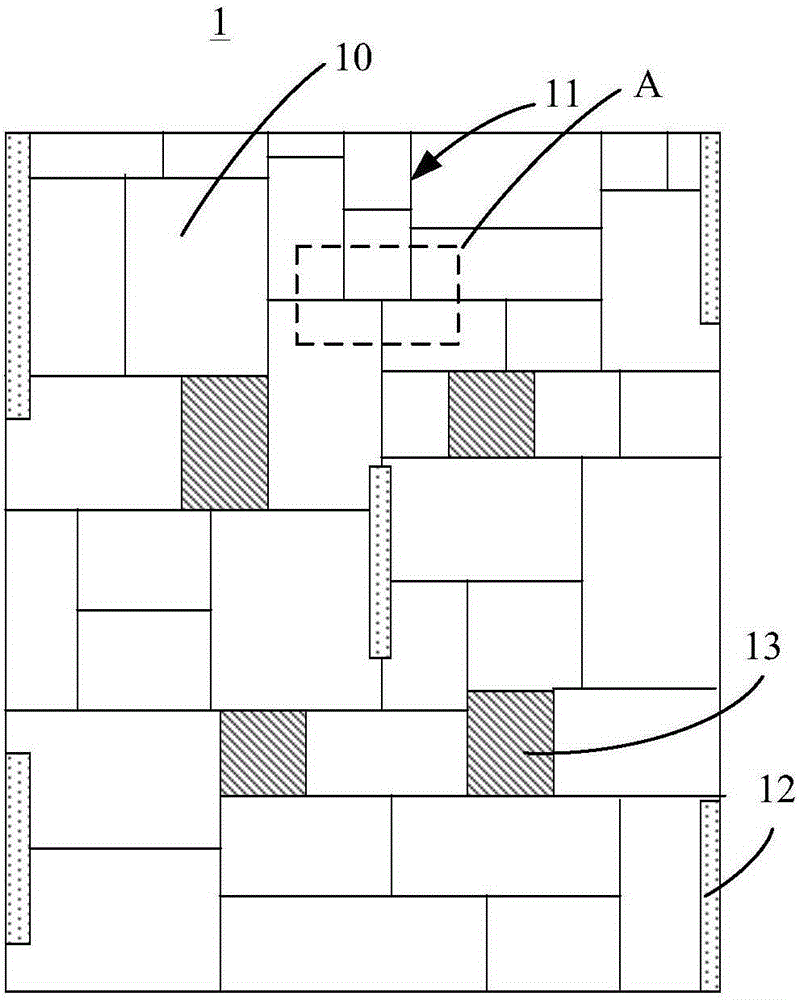

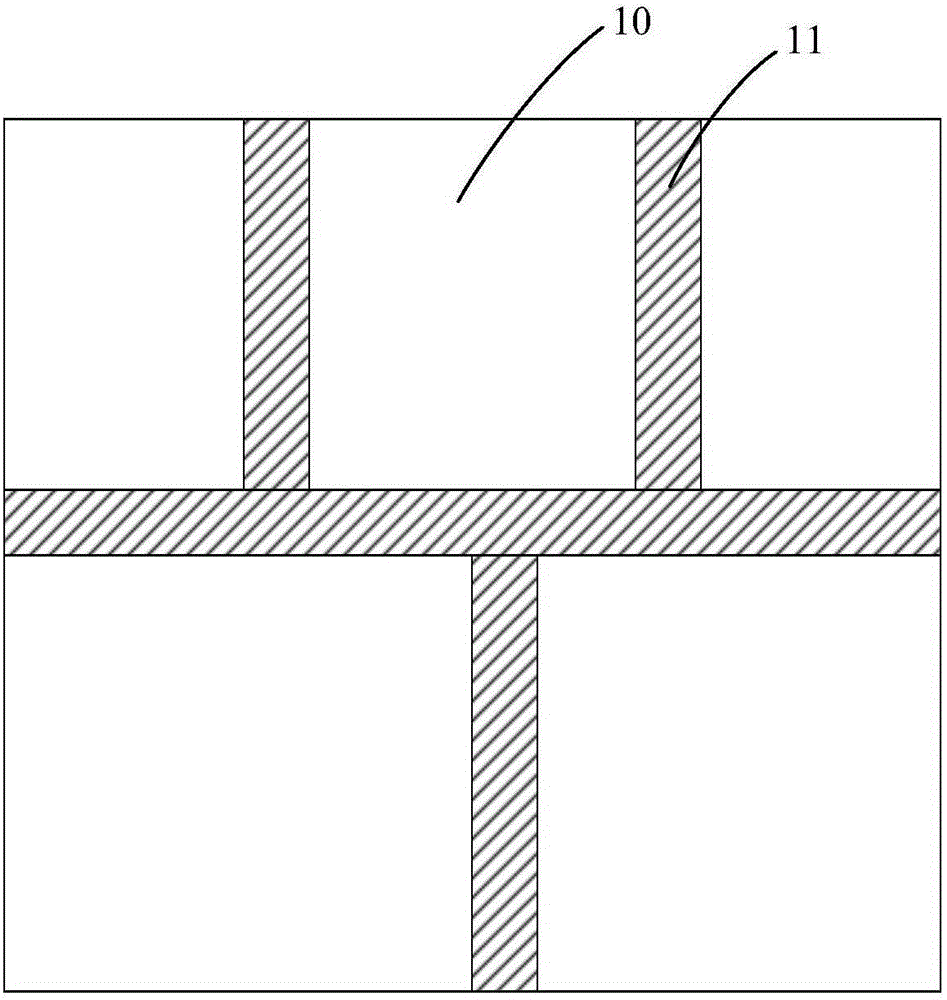

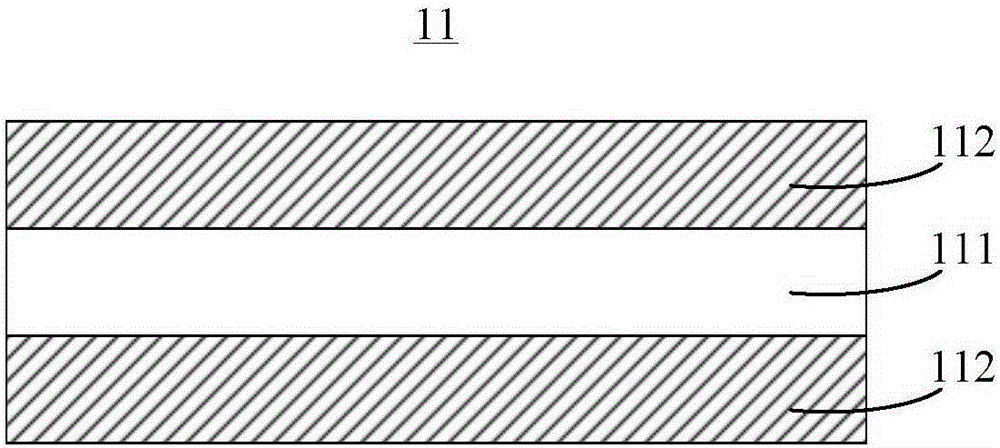

[0030] The mask pattern structure and semiconductor chip manufacturing method of the present invention will be described in more detail below in conjunction with schematic diagrams, wherein a preferred embodiment of the present invention is shown, it should be understood that those skilled in the art can modify the present invention described here, and still The advantageous effects of the present invention are realized. Therefore, the following description should be understood as the broad knowledge of those skilled in the art, but not as a limitation of the present invention.

[0031] In the following paragraphs the invention is described more specifically by way of example with reference to the accompanying drawings. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More