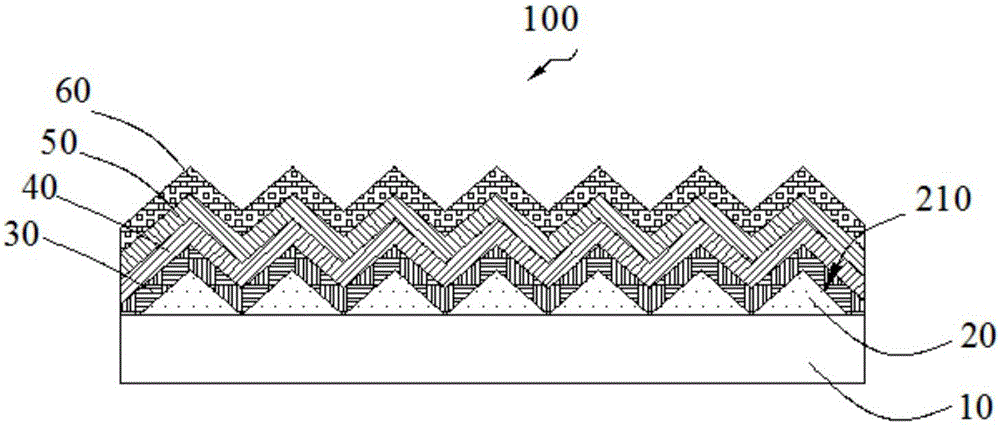

Array substrate, manufacturing method therefor, and liquid crystal display panel

A technology of array substrate and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of GOA circuit design difficulties, large area occupied by capacitors, and increased size, so as to reduce the occupation space, achieve narrow frame design, and increase the effect of facing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

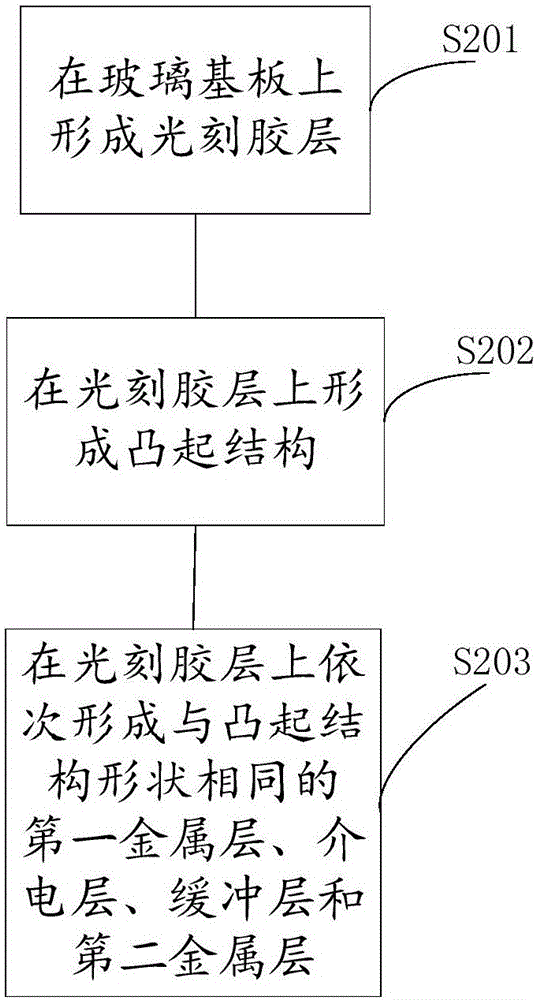

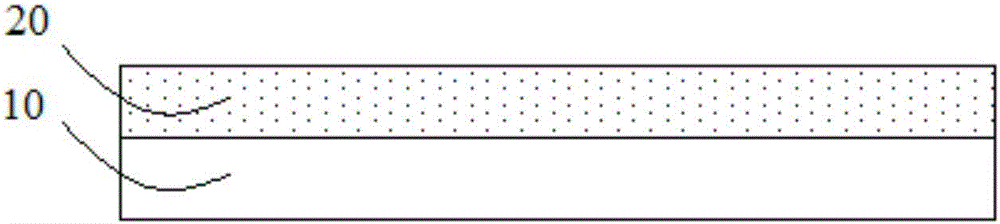

[0027] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0028] In addition, the following descriptions of the various embodiments refer to the attached drawings to illustrate specific embodiments in which the present invention can be implemented. The directional terms mentioned in the present invention, for example, "upper", "lower", "front", "rear", "left", "right", "inner", "outer", "side", etc., only is to refer to the direction of the attached drawings. Therefore, the direction terms used are for ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More